對VGA進行控制,實現任一彩色圖像的顯示。通過采用FPGA設計VGA接口可以將要顯示的數據直接送到液晶顯示器,節省了計算機的處理過程,加快了數據的處理速度,節約了硬件成本。##系統總體框架設計##MATLAB程序##結果分析

2014-03-24 11:54:22 4104

4104

在高速系統中FPGA時序約束不止包括內部時鐘約束,還應包括完整的IO時序約束和時序例外約束才能實現PCB板級的時序收斂。因此,FPGA時序約束中IO口時序約束也是一個重點。只有約束正確才能在高速情況下保證FPGA和外部器件通信正確。

2022-09-27 09:56:09 1382

1382 本帖最后由 eehome 于 2013-1-5 10:06 編輯

本人初學,在這里請教一下各位前輩,用VHDL要做到800*600(60Hz)的VGA如何顯示橫彩條、豎彩條和方格,應該如何編寫程序?對于時序脈沖和消隱也不太理解,懇請大神解釋!!!不勝感激!!!

2012-12-14 12:44:07

經過兩天的惡補,特別是學習了《第五章_FPGA時 序收斂》及其相關的視頻后,我基本上明白了時序分析的概念和用法。之后的幾天,我會根據一些官方的文件對時序分析進行更系統、深入的學習。先總結一下之前

2011-09-23 10:26:01

對自己的設計的實現方式越了解,對自己的設計的時序要求越了解,對目標器件的資源分布和結構越了解,對EDA工具執行約束的效果越了解,那么對設計的時序約束目標就會越清晰,相應地,設計的時序收斂過程就會更可

2016-06-02 15:54:04

的過程是從一次成功的時序收斂結果開始,把特定的一組邏輯(Design Partition)在FPGA上實現的布局位置和布線結果(Netlist)固定下來,保證這一布局布線結果可以在新的編譯中重現,相應

2017-12-27 09:15:17

VGA驅動接口時序設計之1概述本文節選自特權同學的圖書《FPGA設計實戰演練(邏輯篇)》配套例程下載鏈接:http://pan.baidu.com/s/1pJ5bCtt 第六章第8節中我們給出

2015-07-26 21:56:45

VGA驅動接口時序設計之2源同步接口本文節選自特權同學的圖書《FPGA設計實戰演練(邏輯篇)》配套例程下載鏈接:http://pan.baidu.com/s/1pJ5bCtt 好,有了這些信息,我們

2015-07-29 11:19:04

VGA驅動接口時序設計之3時鐘約束本文節選自特權同學的圖書《FPGA設計實戰演練(邏輯篇)》配套例程下載鏈接:http://pan.baidu.com/s/1pJ5bCtt 如圖8.26所示

2015-07-30 22:07:42

`VGA驅動接口時序設計之5建立和保持時間計算本文節選自特權同學的圖書《FPGA設計實戰演練(邏輯篇)》配套例程下載鏈接:http://pan.baidu.com/s/1pJ5bCtt 在我們

2015-08-05 11:14:57

VGA驅動接口時序設計之6建立和保持時間約束本文節選自特權同學的圖書《FPGA設計實戰演練(邏輯篇)》配套例程下載鏈接:http://pan.baidu.com/s/1pJ5bCtt 接著,我們可以

2015-08-06 21:49:33

FPGA數字信號處理實現原理及方法

2012-08-15 19:00:58

FPGA數字信號處理實現原理及方法

2012-08-19 13:37:35

FPGA的時序優化高級研修班通知通過設立四大專題,幫助工程師更加深入理解FPGA時序,并掌握時序約束和優化的方法。1.FPGA靜態時序分析2.FPGA異步電路處理方法3.FPGA時序約束方法4.FPGA時序優化方法

2013-03-27 15:20:27

邏輯設計及構建testbench的方法及技巧;針對FPGA器件的代碼優化方案;第二階段 FPGA設計原則(面積與速度平衡互換原則、硬件可實現原則、同步設計原則等;FPGA的四種操作技巧(乒乓操作、串并轉

2012-09-13 20:07:24

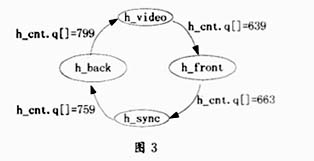

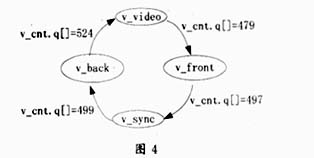

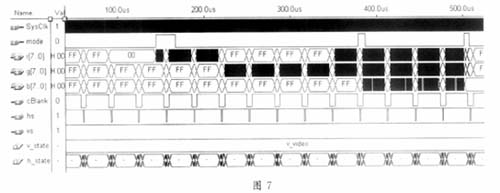

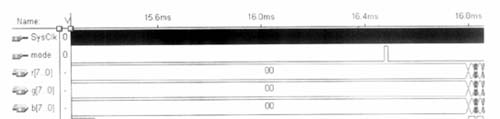

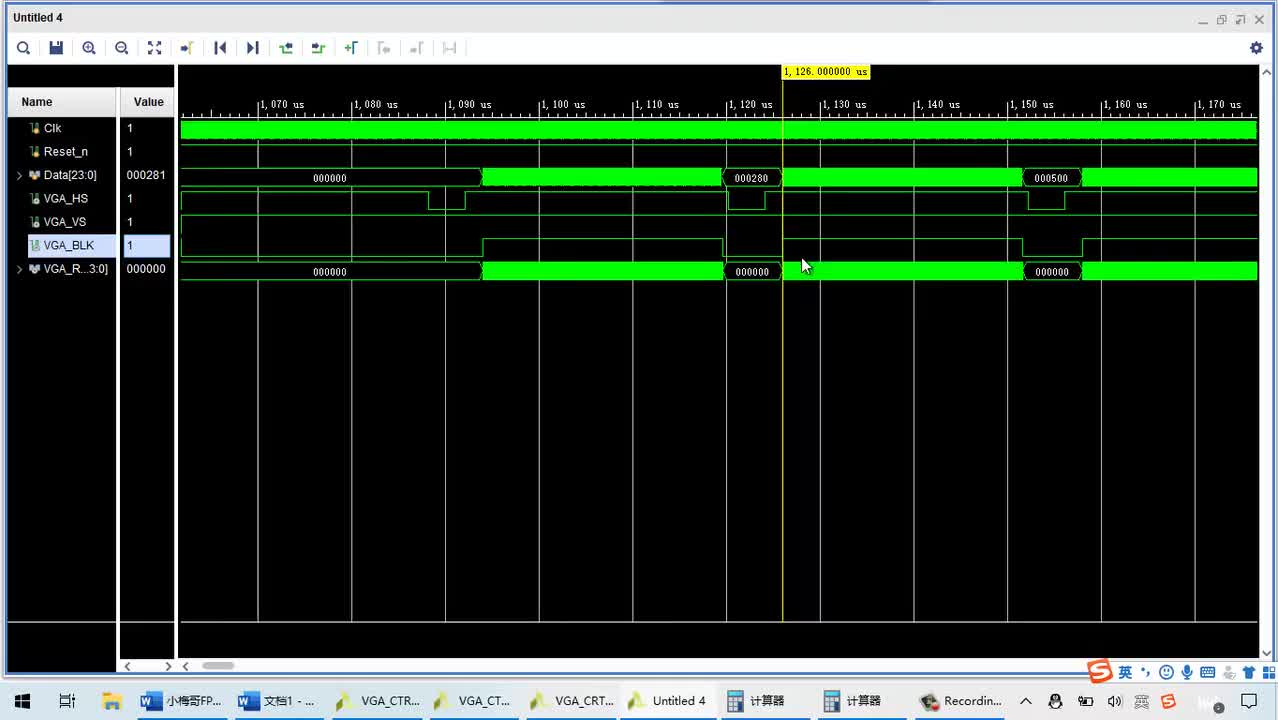

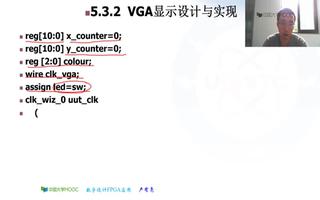

輸入的50MHz的時鐘,產生VGA協議所需要的25MHz的時鐘。vga_ctrl為VGA協議的驅動模塊。vga_ctrl設計實現按照設計分析中的設計方法,進行設計即可。hs_en為列有效顯示的表示信號

2023-03-22 16:51:57

如果將一臺PC機VGA數據在另一臺PC上顯示以及采集VGA信號,傳統的方法是將VGA信號通過視頻轉換器VGA—VIDEO變成視頻信號,再通過視頻采集卡在另一臺PC機上顯示采集。這樣VGA信號經過視頻

2010-08-17 17:50:26

VGA彩條顯示(1) 系統上電后,板卡傳入系統時鐘(sys_clk)和復位信號(sys_rst_n)到頂層模塊;(2) 系統時鐘由頂層模塊傳入時鐘生成模塊(clk_gen),分頻產生 VGA 工作

2022-02-16 06:03:18

VGA顯示原理與VGA時序實現

2012-08-15 16:57:38

三、模塊設計架構設計我們要實現的功能,概括起來就是FPGA產生VGA時序,即控制VGA_R4~R0、VGA_G5~G0、VGA_B4~B0、VGA_HSYNC和VGA_VSYNC,讓顯示器顯示紅色

2018-10-05 11:19:50

三、模塊設計架構設計我們要實現的功能,概括起來就是FPGA產生VGA時序,即控制VGA_R4~R0、VGA_G5~G0、VGA_B4~B0、VGA_HSYNC和VGA_VSYNC,讓顯示器顯示紅色

2019-08-12 09:12:47

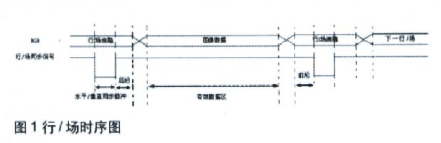

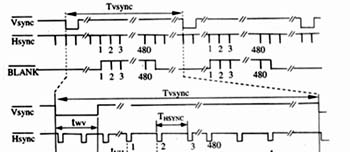

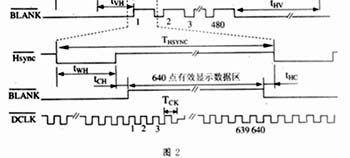

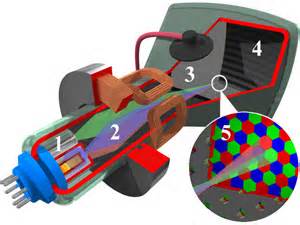

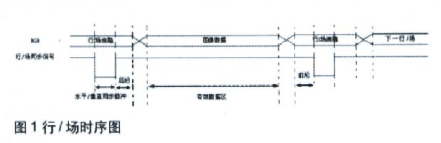

來確定狀態。VGA的接口時序如圖所示,場同步信號VSYNC在每幀(即送一次全屏的圖像)開始的時候產生一個固定寬度的高脈沖,行同步信號HSYNC在每行開始的時候產生一個固定寬度的高脈沖,色彩數據在某些

2016-04-08 09:55:22

,本實例需要用戶自己準備好一臺VGA顯示器和相應的VGA線,VGA線用于連接SF-SP6開發板的J1插座和顯示器。FPGA內部產生ColorBar以及VGA時序用于驅動顯示器顯示。Vga的驅動大體

2016-04-11 09:51:49

的設計思想,您需要在大腦或草稿中構思好您的電路框架,再用硬件描述語言把這一設計理念實現化,讓FPGA讀懂您想要的需求,讓它變成您需要的樣子。如此一來,我們需要先了解VGA信號的構成,以及VGA顯示成像

2017-08-15 09:49:59

通過PL直接配置。 2. 程序設計 本實驗實現通過HDMI顯示彩條,實驗中設計了視頻時序發生和彩條發生模塊“color_bar.v”,I2C Master 寄存器配置模塊

2021-01-15 16:49:10

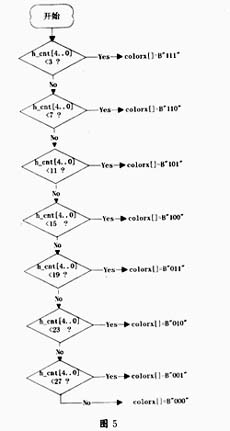

`我想顯示8條均勻的彩條,在640*480的屏幕上面,但是最后那條白色的彩條有一半左右變成黑的了下圖是現象圖和程序圖程序該怎么改,萬分感謝。`

2017-11-26 10:12:34

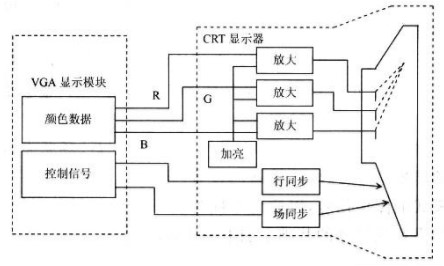

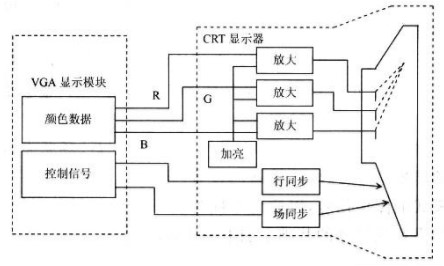

外設連接如圖2.23所示。這個VGA驅動顯示色彩通過3個信號,即R、G、B信號進行設定,實現8色的顯示效果。場同步VSY信號和行同步HSY信號也都由FPGA引腳輸出產生。圖2.23 FPGA與VGA外設

2017-11-07 19:14:38

存儲一定容量的圖像信息,豐富的I/O資源可以隨即擴展外接大容量存儲器的特性,因此由 FPGA完成對圖像數據的處理及產生行場掃描時序信號。很好地實現了圖象數據處理的實時性和穩定性,達到了性能與價格的完美

2019-07-17 07:12:48

,成為電腦顯卡上應用最為廣泛的接口類型,絕大多數的顯卡都帶有此種接口。VGA類型的顯示驅動需要比較高的掃面頻率和盡量短的處理時間,因而通過FPGA來實現VGA顯示的驅動和控制非常有效。在FPGA中

2017-08-02 11:40:35

`基于fpga的1080P彩條dvi接口c顯示,IIC配置ch7301芯片控制dvi輸出彩條,除了第一個彩條和第二個彩條,其他彩條顏色都對,第一個彩條顏色本來是紅色卻變成了洋紅色,第二個本來是黃色

2019-03-12 21:36:39

大家好,我想知道如何實現硬件(FPGA)中的時序報告給出的時序。我的意思是,如何測量FPGA和FPGA中輸入信號的建立或保持時間與靜態時間報告給出的值進行比較。FPGA怪胎以上來自于谷歌翻譯以下

2019-01-15 11:07:15

如何利用FPGA實現VGA的彩色圖片顯示?

2021-06-02 06:20:26

如何利用FPGA的LVDS信號轉VGA源碼及方案

2018-09-29 20:37:41

本帖最后由 演戲00 于 2017-5-27 21:43 編輯

剛接觸fpga不久,這段代碼就是直接抄書上的例子,但用vga接顯示屏之后一直是無信號,我的板子的clk是20MHz,vga的5個

2017-05-27 21:42:09

VGA簡介我們在“VGA彩條顯示實驗”中對VGA視頻傳輸標準作了詳細的介紹,包括VGA接口定義、行場同步時序、以及顯示分辨率等。如果大家對這部分內容不是很熟悉的話,請參考“VGA彩條顯示實驗”中的VGA

2020-08-05 11:12:24

芯片相連接。由于本次實驗不涉及觸摸功能的實現,因此這些信號并未用到。本實驗中,各端口信號的管腳分配如下表所示:表 22.3.1 RGB TFT-LCD彩條實驗管腳分配程序設計RGB TFT-LCD輸入時序

2020-08-08 10:59:22

傳輸標準作了詳細的介紹,包括VGA接口定義、行場同步時序、以及顯示分辨率等。如果大家對這部分內容不是很熟悉的話,請參考“VGA彩條顯示實驗”中的VGA簡介部分。實驗任務本章的實驗任務是使用開拓者開發板上

2020-08-03 15:16:29

用FPGA實現VGA顯示

2015-05-22 18:05:19

算機內部以數字方式生成的顯示圖像信息,通過顯卡中的ADC轉變為R、G、B三基色信號和行、場同步信號,通過電纜傳輸到顯示設備中。VGA時序VGA的時序包括水平時序和垂直時序,且兩者都包含的時序參數有

2019-06-04 05:00:12

波形發生器是信號處理領域中必不可少的設備。這里,介紹了基于FPGA 的模擬電路中階梯波、階梯波等常用漸變信號的波形實現方法,并詳細地闡述了其相應硬件電路的工作原理

2009-12-19 16:17:30 40

40 基于FPGA的DDS信號源設計與實現

利用DDS和 FPGA 技術設計一種信號發生器.介紹了該信號發生器的工作原理、 設計思路及實現方法.在 FPGA 器件上實現了基于 DDS技

2010-02-11 08:48:05 223

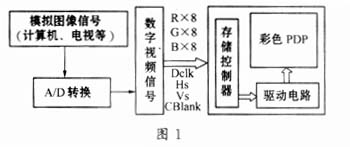

223 利用現場可編程邏輯器件產生GHI時序信號和彩條圖像信號J并將其作為信號源J應用于彩色等離子顯示器的電路開發J方便彩色等離子顯示器驅動控制電路的調試K關鍵詞L視頻圖形

2010-07-17 16:40:14 26

26 本文介紹了基于FPGA/CPLD的嵌入式VGA顯示系統的設計,詳細討論了用VHDL設計行場掃描時序的方法,這種設計方法稍作改動便可產生任意行場掃描時序,具有很好的移植性。該顯示系統

2010-07-28 17:13:22 49

49 一般企業在使用投影儀等設備時,其VGA接頭大多需要人工焊接,接頭多,難焊是VGA的焊接的兩個難頭,弄不好要么沒信號,要么出現色差,下面我把如何焊接VGA頭的方法介紹

2010-09-13 16:08:30 0

0 利用FPGA 設計一個類似點陣LCD 顯示的VGA 顯示控制器,可實現文字及簡單的圖表顯示。工作時只需將要顯示內容轉換成對應字模送入FPGA,即可實現相應內容的顯示。關鍵詞:FPGA

2010-09-22 10:17:23 137

137 介紹了基于Xilinx Spartan- 3E FPGA XC3S250E 來完成分辨率為738×575 的PAL 制數字視頻信號到800×600 的VGA 格式轉換的實現方法。關鍵詞: 圖像放大; PAL; VGA; FPGA

目前, 絕大多數監

2010-09-22 10:29:16 174

174 摘要:介紹了基于FPGA的圖形式LCD&VGA控制器的設計,詳細討論了用VHDL設計行場掃描時序的方法,這種設計方法稍作改動便可產生任意行場掃描時序,具有很好的可重用性。

2009-06-20 13:28:05 1369

1369

帶有PAL色同步信號的彩條信號視頻動畫

2009-07-31 11:46:57 2029

2029

未壓縮的彩條信號行頻圖

2009-07-31 12:31:11 756

756

已壓縮的彩條信號矢量圖

2009-07-31 12:34:12 1097

1097

已壓縮的彩條信號行頻圖

2009-07-31 12:34:48 595

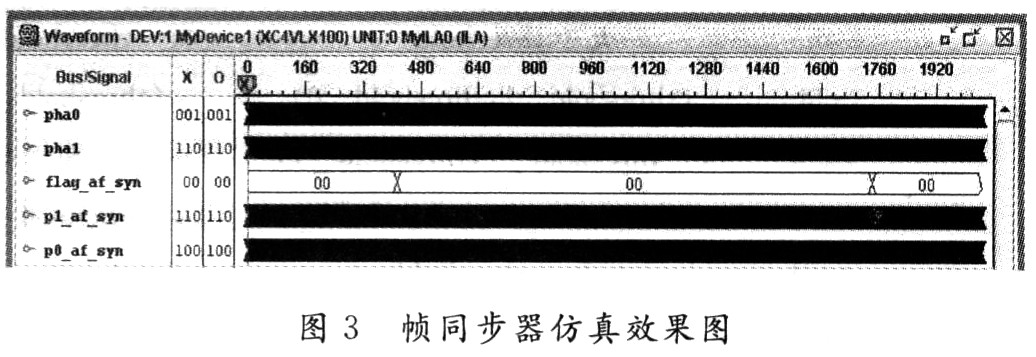

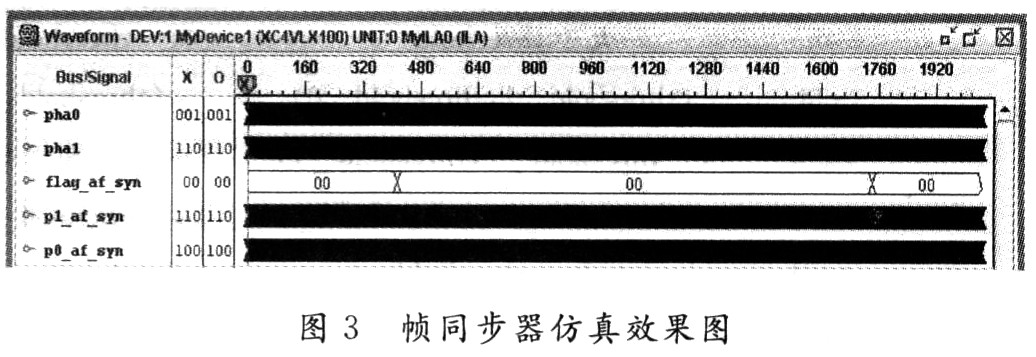

595 一種高速幀同步和相位模糊估計的方法及其FPGA實現

摘要:提出僅依靠接收符號和本地同步碼快速確定MPSK調制符號的幀同步,并同時估計其相位模糊值的計算方法,給

2010-01-27 09:38:17 1278

1278

摘要:文中詳述了FPGA被動串行配置方式的時序,給出配置流程圖及實現的程序代碼,并通過實例驗證了該方法的優越

2010-07-21 14:48:48 1326

1326

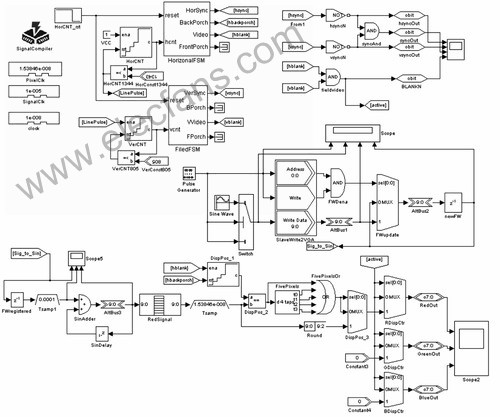

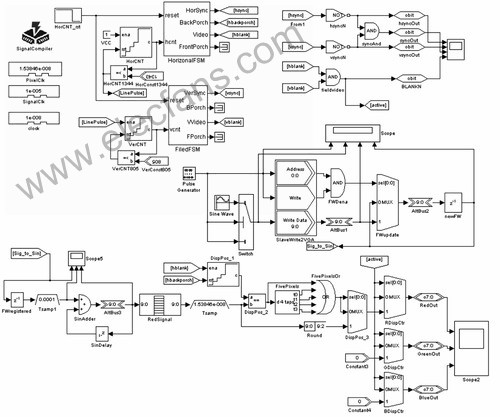

本文基于DSP Builder的VGA接口設計方法,對VGA接口時序和系統設計需求進行了介紹,并在硬件平臺下實現一維與二維信號的顯示。 VGA接口標準 VGA顯

2010-08-03 10:23:40 1209

1209

經過硬件平臺的驗證,基于FPGA 的VGA 圖形顯示器已達到設計要求,可實現彩條、漢字、小圖像和大圖像的顯示,并可實現FPGA 器件對顯示器的單片控制

2011-06-08 09:55:43 1992

1992

本文介紹了一種模目信號設計方法,利用FPGA產生時序及控制,DSP實時計算所需要的回波,從而實現對雷達目標回波的模擬,這樣可以在沒有陣面數據的情況下,使信號處理分系統調試能

2011-07-05 09:46:27 1110

1110

本文設計的基于FPGA的數字圖像實時生成系統,可以實現各種數字、文字、彩條、ROM圖像信號輸出。其圖像顯示控制器的系統處理耗時小于20ms,完全達到了實時要求(50場/秒)。所進行的原

2011-09-19 10:54:55 4951

4951

VGA圖像信號發生器的設計涉及到圖像數據的處理,對電路的工作速度和性能要求較高,VGA工業標準要求的時鐘頻率高達25MHz,使用傳統的電子電路設計方法是難以實現的。采用專用的視頻

2012-05-25 10:29:16 2350

2350

當你的FPGA設計不能滿足時序要求時,原因也許并不明顯。解決方案不僅僅依賴于使用FPGA的實現工具來優化設計從而滿足時序要求,也需要設計者具有明確目標和診斷/隔離時序問題的能力。

2014-08-15 14:22:10 1169

1169 基于FPGA的VGA接口實現和字符顯示論文

2015-10-29 17:18:24 8

8 FPGA時序約束方法很好地資料,兩大主流的時序約束都講了!

2015-12-14 14:21:25 19

19 fpga vga 顯示,介紹了如何實現vga的操作以及如何配置

2016-03-15 18:29:06 6

6 Xilinx FPGA工程例子源碼:用FPGA模擬VGA時序PS_2總線的鍵盤接口VHDL源代碼

2016-06-07 15:11:20 32

32 基于FPGA的VGA圖像控制器的設計與實現

2016-08-30 15:10:14 11

11 三目立體視覺外極線校正及其FPGA實現方法

2016-09-17 07:30:24 16

16 華清遠見FPGA代碼-VGA接口的設計與實現

2016-10-27 18:07:54 8

8 混沌擴頻SPWM最優參數選取方法及其在FPGA上的實時實現_朱少平

2017-01-08 10:57:06 0

0 當你的FPGA設計不能滿足時序要求時,原因也許并不明顯。解決方案不僅僅依賴于使用FPGA的實現工具來優化設計從而滿足時序要求,也需要設計者具有明確目標和診斷/隔離時序問題的能力。設計者現在有一些

2017-02-09 01:59:11 264

264 多抽樣率的數字信號處理及其FPGA實現

2017-10-30 11:42:44 10

10 作時序和布局約束是實現設計要求的關鍵因素。本文是介紹其使用方法的入門讀物。 完成 RTL 設計只是 FPGA 設計量產準備工作中的一部分。接下來的挑戰是確保設計滿足芯片內的時序和性能要求。為此

2017-11-17 05:23:01 2417

2417

一個好的FPGA設計一定是包含兩個層面:良好的代碼風格和合理的約束。時序約束作為FPGA設計中不可或缺的一部分,已發揮著越來越重要的作用。毋庸置疑,時序約束的最終目的是實現時序收斂。時序收斂作為

2017-11-17 07:54:36 2326

2326

現有的工具和技術可幫助您有效地實現時序性能目標。當您的FPGA 設計無法滿足時序性能目標時,其原因可能并不明顯。解決方案不僅取決于FPGA 實現工具為滿足時序要求而優化設計的能力,還取決于設計人員指定前方目標,診斷并隔離下游時序問題的能力。

2017-11-18 04:32:34 2951

2951 的效果,依據該原理,可以實現圖像的采集及在VGA顯示屏上顯示的實現。利用FPGA產生VGA時序信號和發送圖像信息,并將其作為圖像信號采集系統,將大大減小圖像開發的難度和投入。

2017-11-18 12:42:02 2114

2114 作為賽靈思用戶論壇的定期訪客(見 ),我注意到新用戶往往對時序收斂以及如何使用時序約束來達到時序收斂感到困惑。為幫助 FPGA設計新手實現時序收斂,讓我們來深入了解時序約束以及如何利用時序約束實現

2017-11-24 19:37:55 4903

4903

本文為大家分享fpga控制vga顯示圖片的方法。

2018-01-15 15:56:33 7656

7656 VGA是一種學習FPGA最常見的基礎實驗。雖然現在的顯示屏大多已經采用DVI和HDMI方案,但其實VGA在另一個地方還有應用,那就是大屏的LCD。目前4.3寸以上的TFT基本都是VGA接口,這樣在完成一個FPGA系統設計時,選擇一個VGA接口的TFT用來顯示便是最簡單方便的方案。

2018-06-26 07:03:00 15969

15969 利用現場可編程邏輯器件產生VGA時序信號和彩條圖像信號,并將其作為信號源,應用于電視機或計算機等彩色顯示器的電路開發,方便彩色顯示器驅動控制電路的調試。計算機顯示器的顯示有許多標準,常見的有VGA,SVGA等。

2019-05-03 09:09:00 3695

3695

中國大學MOOC

本課程以目前流行的Xilinx 7系列FPGA的開發為主線,全面講解FPGA的原理及電路設計、Verilog HDL語言及VIVADO的應用,并循序漸進地從組合邏輯、時序邏輯的開發開始,深入到FPGA的基礎應用、綜合應用和進階應用。

2019-08-07 06:00:00 2342

2342

VGA技術的應用還主要基于VGA顯示卡的計算機、筆記本等設備,而在一些既要求顯示彩色高分辨率圖像又沒有必要使用計算機的設備上,VGA技術的應用卻很少見到。

2019-09-20 07:01:00 1392

1392

VGA技術的應用還主要基于VGA顯示卡的計算機、筆記本等設備,而在一些既要求顯示彩色高分辨率圖像又沒有必要使用計算機的設備上,VGA技術的應用卻很少見到。

2019-09-10 06:09:00 2309

2309

本實驗是用 FPGA 來實現 VGA 圖像控制器,控制顯示器顯示彩條信號,分別通過撥碼開關選擇顯示橫彩條、豎彩條和棋盤格。學習并掌握 VGA 圖像顯示控制器的設計。

2019-06-25 17:40:09 11

11 VGA(視頻圖形陣列)作為一種標準的顯示接口得到廣泛的應用。依據VGA顯示原理,介紹了利用FPGA實現對VGA圖形控制器的Verilog設計方法。詳細描述了各硬件模塊的工作原理及實現途徑,并給出了軟件設計思路。

2019-06-29 10:05:30 4793

4793

隨著電子技術的發展,VGA(視頻圖形陣列)接口出現在很多嵌入式平臺上,用于圖像信息的實時顯示等。在某些情況下,設計者希望通過普通的顯示器或投影儀觀測FPGA內部的一些矢量信號,即把帶VGA接口的顯示器當作示波器使用等,這就需要對數據進行處理,使之能夠在顯示器上實時顯示。

2020-04-06 08:22:00 1685

1685

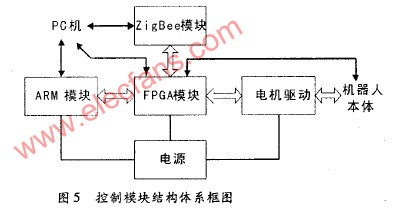

介紹了單片機與FPGA 異步串行通信的實現方法,給出了系統結構原理框圖及其部分VHDL 程序,并定義了發送器和接收器的端口信號。

2020-09-29 16:20:00 8

8 依據VGA顯示原理。利用VHDL作為設計語言.設計了一種基于現場可編程器件FPGA的VGA多圖像控制器,并在硬件平臺上實現設計目標。與傳統的設計相比,增加了圖像模式的選擇,便于嵌入式系統應用擴展。使用FPGA代替VGA的專用顯示芯片,可以提高數據處理速度,節約硬件成本。

2021-01-29 15:27:51 20

20 VGA彩條顯示(1) 系統上電后,板卡傳入系統時鐘(sys_clk)和復位信號(sys_rst_n)到頂層模塊;(2) 系統時鐘由頂層模塊傳入時鐘生成模塊(clk_gen),分頻產生 VGA 工作

2021-12-17 18:44:18 8

8 FPGA-VGA的實現資料合集

2022-01-05 15:34:15 19

19 對于建立時間和保持時間本文就不再過多敘述,可參考【FPGA】幾種時序問題的常見解決方法-------3,可以說在數字高速信號處理中最基本的概念就是建立時間和保持時間,而我們要做的就是解決亞穩態問題和傳輸穩定問題。

2022-12-13 11:03:58 225

225

電子發燒友App

電子發燒友App

評論