大家好,又到了每日學(xué)習(xí)的時(shí)間了,今天我們來(lái)聊一聊基于FPGA的異步FIFO的實(shí)現(xiàn)。 一、FIFO簡(jiǎn)介 FIFO是英文First In First Out 的縮寫(xiě),是一種先進(jìn)先出的數(shù)據(jù)緩存器,它與普通

2018-06-21 11:15:25 6164

6164

非對(duì)稱(chēng)算法,你了解多少呢?

2022-09-05 21:07:42 3788

3788

FIFO (先入先出, First In First Out )存儲(chǔ)器,在 FPGA 和數(shù)字 IC 設(shè)計(jì)中非常常用。 根據(jù)接入的時(shí)鐘信號(hào),可以分為同步 FIFO 和異步 FIFO 。

2023-06-27 10:24:37 1199

1199

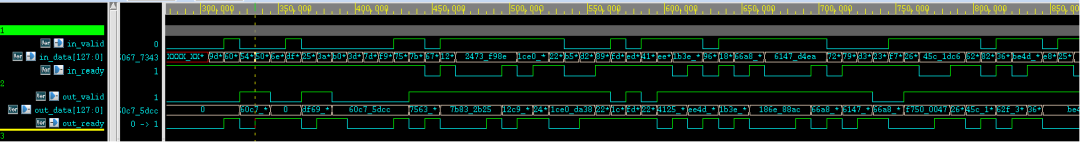

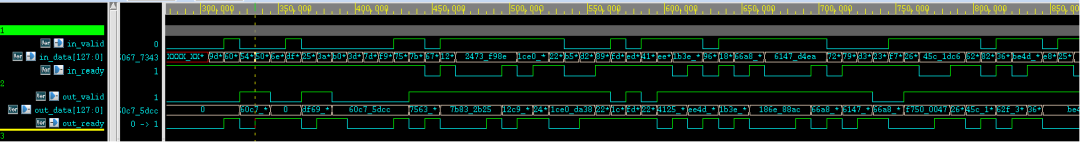

按照正常的思路,在前文完成前向時(shí)序優(yōu)化和后向時(shí)序優(yōu)化后,后面緊跟的應(yīng)該是雙向時(shí)序優(yōu)化策略了,不過(guò)不急,需要先實(shí)現(xiàn)一下握手型同步FIFO。

2023-12-04 14:03:49 263

263

本文簡(jiǎn)述了非對(duì)稱(chēng)晶閘管的結(jié)構(gòu)特點(diǎn)及其工作原理,分析了非對(duì)稱(chēng)晶閘管的關(guān)鍵結(jié)構(gòu)參數(shù)對(duì)其特性的影響,以及結(jié)構(gòu)參數(shù)之間的相互制約關(guān)系。對(duì)6.5kV非對(duì)稱(chēng)晶閘管進(jìn)行了特性模擬與優(yōu)化,給出優(yōu)化設(shè)計(jì)的縱向結(jié)構(gòu)參數(shù)

2010-05-04 08:06:51

非對(duì)稱(chēng)ZVS半橋電路原理圖

2009-10-30 14:29:47

本文從對(duì)比兩顆分立MCU與單芯片雙核MCU開(kāi)始(以LPC4350為例),展開(kāi)介紹了非對(duì)稱(chēng)雙核MCU的基礎(chǔ)知識(shí)與重要特點(diǎn)。接下來(lái),重點(diǎn)介紹了核間通信的概念與幾種實(shí)現(xiàn)方式,尤其是基于消息池的控制/狀態(tài)

2021-11-01 06:29:40

透鏡條 白色 非對(duì)稱(chēng) 卡入式

2024-03-14 23:11:32

如題,STM32F0 如何輸出非對(duì)稱(chēng)PWM波形。如何設(shè)置的? 請(qǐng)教高手。目前正在高單電阻電流采樣的SVPWM控制。

2017-08-03 08:56:47

進(jìn)行通信,因此系統(tǒng)穩(wěn)定性將大大提高,有效地降低系統(tǒng)崩潰概率,從而保證數(shù)據(jù)信息完整性。

更低“系統(tǒng)硬件成本”內(nèi)部通信的方式?jīng)Q定了僅需一套硬件電路即刻實(shí)現(xiàn)復(fù)雜的功能,使得非對(duì)稱(chēng)AMP架構(gòu)方案擁有更低的系統(tǒng)

2023-12-01 09:35:26

普通單片機(jī)可以處理非對(duì)稱(chēng)加密算法嗎?速度如何?求大神解答

2015-09-17 12:38:26

我有 DNA 424 NFC 標(biāo)簽,但遇到了問(wèn)題。標(biāo)簽是對(duì)稱(chēng)加密的。這意味著我不能與其他想要獨(dú)立驗(yàn)證掃描的來(lái)源共享密鑰(這是我的實(shí)現(xiàn)想要允許的)。更具體地說(shuō),該實(shí)現(xiàn)將使用區(qū)塊鏈,我不能將對(duì)稱(chēng)密鑰放在

2023-04-14 06:21:54

幀同步是什么工作原理?如何用VHDL語(yǔ)言實(shí)現(xiàn)幀同步的設(shè)計(jì)?

2021-04-08 06:33:59

本文系統(tǒng)地介紹了 C2000 Concerto 系列非對(duì)稱(chēng)雙核 MCU 的基礎(chǔ)知識(shí)和重要特點(diǎn)。

2021-04-02 06:02:42

我想知道 NXP 是否提供了使用加密模塊實(shí)現(xiàn)非對(duì)稱(chēng)密鑰導(dǎo)入(RSA 或 ECC)的示例?

RTD 中的示例僅實(shí)現(xiàn)對(duì)稱(chēng)密鑰導(dǎo)入 (AES)。

2023-04-28 06:54:24

什么是對(duì)稱(chēng)密鑰密碼體制?對(duì)稱(chēng)密鑰密碼體制的缺點(diǎn)是什么?非對(duì)稱(chēng)加密算法又是什么?非對(duì)稱(chēng)加密算法的缺點(diǎn)是什么?

2021-12-23 06:05:12

蘋(píng)果獲得Macbook Pro非對(duì)稱(chēng)散熱風(fēng)扇設(shè)計(jì)專(zhuān)利本周四蘋(píng)果獲準(zhǔn)了三項(xiàng)新專(zhuān)利,專(zhuān)利內(nèi)容主要與最新Retina顯示屏MacBook Pro上的非對(duì)稱(chēng)散熱風(fēng)扇葉片相關(guān),這種設(shè)計(jì)可在極大降低散熱帶來(lái)噪音

2012-12-23 10:30:52

本文討論了在ASIC設(shè)計(jì)中數(shù)據(jù)在不同時(shí)鐘之間傳遞數(shù)據(jù)所產(chǎn)生的亞穩(wěn)態(tài)問(wèn)題,并提出了一種新的異步FIFO的設(shè)計(jì)方法,并用VHDL語(yǔ)言進(jìn)行描述,利用Altera公司的Cyclone系列的EP1C6進(jìn)行硬件實(shí)現(xiàn),該電路軟件仿真和硬件實(shí)現(xiàn)已經(jīng)通過(guò)驗(yàn)證,并應(yīng)用到各種電路中。

2021-04-29 06:54:00

DC-DC拓?fù)浣Y(jié)構(gòu)中常用到的橋式電路中的驅(qū)動(dòng)方式有對(duì)稱(chēng)驅(qū)動(dòng)、非對(duì)稱(chēng)驅(qū)動(dòng)以及互補(bǔ)驅(qū)動(dòng)幾個(gè)概念,請(qǐng)問(wèn)這三種驅(qū)動(dòng)方式的具體區(qū)別是什么?因?yàn)樵谟?jì)算伏秒平衡時(shí)與非橋式電路有所差別,為什么有些作用時(shí)間是(1/2 - D)Ts呢?

2019-05-07 19:58:36

請(qǐng)問(wèn)哪位知道代碼開(kāi)源的適合AMP,非對(duì)稱(chēng)模式下的操作系統(tǒng),只需要簡(jiǎn)單的核間任務(wù)通信和資源同步就可以。

2013-12-11 17:38:49

基于橢圓曲線上的雙線性映射提出一種非對(duì)稱(chēng)公鑰叛逆者追蹤方案。采用Lagrange 插值實(shí)現(xiàn)一個(gè)密鑰一次加密對(duì)應(yīng)多個(gè)不同的解密密鑰解密。結(jié)合Weil 配對(duì)的雙線性特性并利用與普通密

2009-03-28 08:41:48 15

15 首先介紹異步FIFO 的概念、應(yīng)用及其結(jié)構(gòu),然后分析實(shí)現(xiàn)異步FIFO的難點(diǎn)問(wèn)題及其解決辦法; 在傳統(tǒng)設(shè)計(jì)的基礎(chǔ)上提出一種新穎的電路結(jié)構(gòu)并對(duì)其進(jìn)行綜合仿真和FPGA 實(shí)現(xiàn)。

2009-04-16 09:25:29 46

46 基于FPGA對(duì)稱(chēng)型FIR濾波器的設(shè)計(jì)與實(shí)現(xiàn):在基于FPGA的對(duì)稱(chēng)型FIR數(shù)字濾波器設(shè)計(jì)中,為了提高速度和運(yùn)行效率,提出了使用線性I相位結(jié)構(gòu)和加法樹(shù)乘法器的方法,并利用Altera公I(xiàn)司的FPG

2009-09-25 15:38:38 30

30 本文主要研究了用FPGA 芯片內(nèi)部的EBRSRAM 來(lái)實(shí)現(xiàn)異步FIFO 設(shè)計(jì)方案,重點(diǎn)闡述了異步FIFO 的標(biāo)志信號(hào)——空/滿狀態(tài)的設(shè)計(jì)思路,并且用VHDL 語(yǔ)言實(shí)現(xiàn),最后進(jìn)行了仿真驗(yàn)證。

2010-01-13 17:11:58 40

40 給出了一個(gè)利用格雷碼對(duì)地址編碼的羿步FIFO 的實(shí)現(xiàn)方法,并給出了VHDL 程序,以解決異步讀寫(xiě)時(shí)鐘引起的問(wèn)題。

2010-07-16 15:15:42 26

26 用光學(xué)技術(shù)測(cè)量三維非對(duì)稱(chēng)溫度場(chǎng)

2010-07-26 15:54:46 11

11 本文設(shè)計(jì)了一種在數(shù)字通信系統(tǒng)中的數(shù)字鎖相位同步提取方案,詳細(xì)介紹了本設(shè)計(jì)的位同步提取原理及其各個(gè)組成功能模塊的VHDL語(yǔ)言實(shí)現(xiàn),并在Quartus II開(kāi)發(fā)平臺(tái)上仿真驗(yàn)證通過(guò)。本

2010-08-06 14:28:08 64

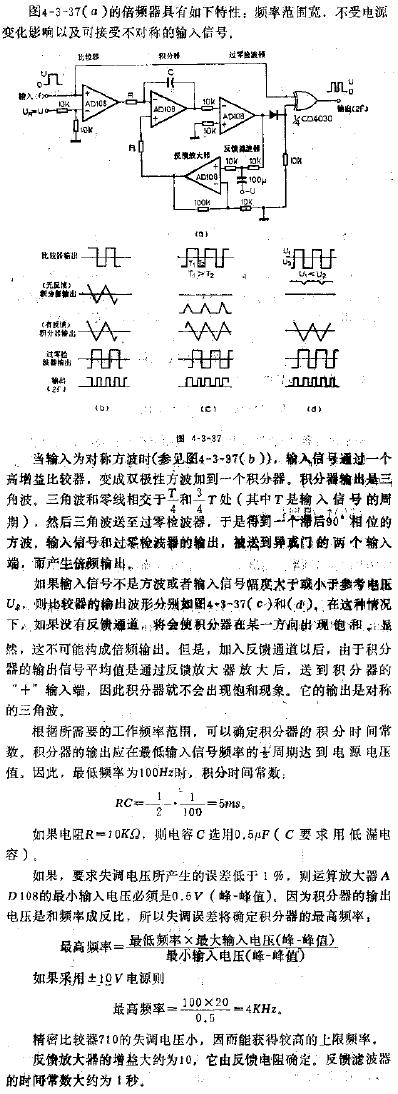

64 非對(duì)稱(chēng)型多諧振蕩器電路圖

如圖A所示,非門(mén)G3用于輸出波形整形。

非對(duì)稱(chēng)

2007-11-22 12:55:25 3575

3575

基于FPGA的FIFO設(shè)計(jì)和應(yīng)用

引 言

在利用DSP實(shí)現(xiàn)視頻實(shí)時(shí)跟蹤時(shí),需要進(jìn)行大量高速的圖像采集。而DSP本身自帶的FIFO并不足以支持系統(tǒng)中大量數(shù)據(jù)的暫時(shí)存儲(chǔ)

2009-11-20 11:25:45 2127

2127

LSI豐富非對(duì)稱(chēng)多核解決方案

LSI 公司 宣布推出適用于無(wú)線應(yīng)用的最新系列非對(duì)稱(chēng)多核芯片解決方案和軟件。這些新一代處理器基于 LSI 前代業(yè)界領(lǐng)先的無(wú)線基礎(chǔ)設(shè)施

2010-02-23 09:06:56 542

542 什么是非對(duì)稱(chēng)數(shù)字用戶(hù)線(ADSL)

概述 ADSL是DSL的一種非對(duì)稱(chēng)版本,它利用數(shù)字編碼技術(shù)從現(xiàn)有銅質(zhì)電話線上獲取最大數(shù)據(jù)傳輸容量,同

2010-04-06 09:17:20 5905

5905 摘要:介紹了利用非對(duì)稱(chēng)光纖腔作為邊沿濾波器的光纖光柵波長(zhǎng)移位檢測(cè)方案。基于薄膜干涉理論對(duì)該非對(duì)稱(chēng)F-P腔的反射率響應(yīng)關(guān)系進(jìn)行計(jì)算與分析,得出該F-P腔的結(jié)構(gòu)參數(shù),改善了普通F-P腔的反射特性,具有線性范圍寬和純屬度好的優(yōu)點(diǎn)。利用該F-P腔的某一線性濾

2011-02-16 03:21:22 30

30 本文闡述了主同步搜索的改進(jìn)型算法,并且針對(duì)這種算法提出了基于片上RAM 的實(shí)現(xiàn)方式,最大程度地節(jié)省了FPGA 的硬件資源,為WCDMA 同步的FPGA 實(shí)現(xiàn)提供了很好的解決方案。這種技術(shù)可

2011-05-14 16:45:53 30

30 由于對(duì)稱(chēng)加密體制的安全性難以保障,在網(wǎng)絡(luò)安全狀況日益嚴(yán)重的情況下,需要有一種強(qiáng)有力的安全加密方法來(lái)保護(hù)重要的數(shù)據(jù)不被竊取和篡改,非對(duì)稱(chēng)加密體制利用公鑰和私鑰來(lái)解決

2011-06-08 14:56:17 0

0 飛思卡爾半導(dǎo)體針對(duì)2.11GHz~2.17GHz頻段的3G市場(chǎng)推出的方案是,提供包含兩個(gè)專(zhuān)用LDMOS器件的芯片集,用于

非對(duì)稱(chēng)Doherty拓?fù)洹?/div>

2011-08-25 14:31:45 1630

1630

提出了一種可用于非對(duì)稱(chēng)層合板結(jié)構(gòu)的高階簡(jiǎn)化位移模型,以精確的模擬剪切變形效應(yīng),并驗(yàn)證該模型是正確有效的。運(yùn)用高階溫度場(chǎng)理論以精確描述溫度沿板厚度的分布。從而建立了

2011-09-07 18:52:04 0

0 為了解決基于LabVIEWFPGA模塊的DMAFIFO深度設(shè)定不當(dāng)帶來(lái)的數(shù)據(jù)不連續(xù)問(wèn)題,結(jié)合LabVIEWFPGA的編程特點(diǎn)和DMA FIFO的工作原理,提出了一種設(shè)定 FIFO 深度的方法。對(duì)FIFO不同深度的實(shí)驗(yàn)表明,采

2011-09-26 13:45:17 6923

6923

文中給出了異步FIFO的實(shí)現(xiàn)代碼和FPGA與DSP的硬件連接電路。經(jīng)驗(yàn)證,利用異步FIFO的方法,在FPGA與DSP通信中的應(yīng)用,具有傳輸速度快、穩(wěn)定可靠、實(shí)現(xiàn)方便的優(yōu)點(diǎn)。

2011-12-12 14:28:22 51

51 本文從對(duì)比兩顆分立MCU與單芯片雙核MCU開(kāi)始(以LPC4350為例),展開(kāi)介紹了非對(duì)稱(chēng)雙核MCU的基礎(chǔ)知識(shí)與重要特點(diǎn)。接下來(lái),重點(diǎn)介紹了核間通信的概念與幾種實(shí)現(xiàn)方式,尤其是基于消息池的

2012-03-26 15:31:09 3244

3244

本文從對(duì)比兩顆分立MCU與單芯片雙核MCU開(kāi)始(以LPC4350為例),展開(kāi)介紹了非對(duì)稱(chēng) 雙核MCU 的基礎(chǔ)知識(shí)與重要特點(diǎn)。接下來(lái),重點(diǎn)介紹了核間通信的概念與幾種實(shí)現(xiàn)方式,尤其是基于消息池

2012-04-11 10:05:21 958

958

為實(shí)現(xiàn)目標(biāo)識(shí)別與跟蹤的應(yīng)用目的 ,在基于 TMS320DM642 的 FIFO 基礎(chǔ)上擴(kuò)展存儲(chǔ)空間 ,提出一種基于

FPGA實(shí)現(xiàn) SDRAM 控制器的方法。分析所用 SDRAM 的特點(diǎn)和工作原理

2015-10-29 14:05:57 2

2 異步FIFO結(jié)構(gòu)及FPGA設(shè)計(jì),解決亞穩(wěn)態(tài)的問(wèn)題

2015-11-10 15:21:37 4

4 JAVA教程之非對(duì)稱(chēng)加密,很好的JAVA的資料,快來(lái)下載吧。

2016-04-13 10:18:23 6

6 非對(duì)稱(chēng)波驅(qū)動(dòng)的非接觸式超聲電機(jī),下來(lái)看看

2016-05-04 15:05:09 17

17 基于TMS320LF2407非對(duì)稱(chēng)采樣五電平脈沖實(shí)現(xiàn)

2016-05-06 15:39:23 16

16 非對(duì)稱(chēng)多諧振蕩器原理圖都是值得參考的設(shè)計(jì)。

2016-05-11 17:11:44 21

21 Xilinx FPGA工程例子源碼:VHDL實(shí)現(xiàn)對(duì)圖像的采集和壓縮

2016-06-07 14:54:57 6

6 VHDL例程 FIFO程序,感興趣的小伙伴們可以瞧一瞧。

2016-11-10 17:12:34 4

4 垂直軸風(fēng)力機(jī)非對(duì)稱(chēng)翼型葉片變攻角方法_張立軍

2016-12-29 14:40:19 0

0 病理嗓音發(fā)聲系統(tǒng)的非對(duì)稱(chēng)建模研究_陶智

2017-01-07 16:06:32 3

3 全彩LED顯示屏用非對(duì)稱(chēng)節(jié)能型LAMP器件的設(shè)計(jì)

2017-02-08 02:14:51 19

19 在我的上一篇博客中我介紹了利用Zynq SoC上的兩個(gè)ARM Cortex-A9 MPCore處理器執(zhí)行不同的任務(wù)程序,實(shí)現(xiàn)非對(duì)稱(chēng)的多進(jìn)程處理模式的概念。

2017-02-11 10:08:38 1898

1898

摘要 利用異步FIFO實(shí)現(xiàn)FPGA與DSP進(jìn)行數(shù)據(jù)通信的方案。FPGA在寫(xiě)時(shí)鐘的控制下將數(shù)據(jù)寫(xiě)入FIFO,再與DSP進(jìn)行握手后,DSP通過(guò)EMIFA接口將數(shù)據(jù)讀入。文中給出了異步FIFO的實(shí)現(xiàn)

2017-10-30 11:48:44 1

1 )片上集成的高速FIFO實(shí)現(xiàn)采集數(shù)據(jù)的高速緩存并通過(guò)對(duì)高速FIFO的讀寫(xiě)操作實(shí)現(xiàn)總線同步數(shù)據(jù)傳輸,提高數(shù)據(jù)的傳輸速率。

2018-07-12 09:06:00 4707

4707

對(duì)稱(chēng)加密算法在加密和解密時(shí)使用的是同一個(gè)秘鑰;而非對(duì)稱(chēng)加密算法需要兩個(gè)密鑰來(lái)進(jìn)行加密和解密,這兩個(gè)秘鑰是公開(kāi)密鑰(public key,簡(jiǎn)稱(chēng)公鑰)和私有密鑰(private key,簡(jiǎn)稱(chēng)私鑰)與對(duì)稱(chēng)

2017-12-10 10:38:10 21396

21396

對(duì)稱(chēng)式加密:解密方式是加密方式的逆運(yùn)算,即加密和解密使用的是同一個(gè)密鑰(初等加密算法)。非對(duì)稱(chēng)式加密:加密和解密需要兩個(gè)密鑰進(jìn)行,這兩個(gè)密鑰是公鑰和私鑰(高等加密算法)。

2017-12-10 10:54:50 4971

4971

針對(duì)光纖光柵反射譜不對(duì)稱(chēng)所導(dǎo)致的尋峰算法誤差問(wèn)題,提出了一種基于FPCA狀態(tài)機(jī)的非對(duì)稱(chēng)高斯擬合尋峰算法。算法通過(guò)狀態(tài)機(jī)之間的相互轉(zhuǎn)換完成對(duì)數(shù)據(jù)的篩選處理,然后引入非對(duì)稱(chēng)高斯模型,給出峰值補(bǔ)償修正公式

2018-01-09 10:58:58 3

3 針對(duì)由兩個(gè)非對(duì)稱(chēng)液壓缸組成的電液伺服同步舉升系統(tǒng),首先建立了該系統(tǒng)的非線性耦合模型,并在該模型的基礎(chǔ)上設(shè)計(jì)出一種魯棒自適應(yīng)跟蹤控制器。該控制器利用多變量后推設(shè)計(jì)方法實(shí)現(xiàn)了液壓缸對(duì)目標(biāo)軌跡的跟蹤控制

2018-02-28 14:29:44 0

0 深海有纜水下機(jī)器人在惡劣海況下作業(yè)時(shí),常配備相應(yīng)的升沉補(bǔ)償系統(tǒng)以提高水下機(jī)器人釋放和回收作業(yè)的安全性。重點(diǎn)研究了基于閥控非對(duì)稱(chēng)伺服缸的半主動(dòng)升沉補(bǔ)償方式,介紹了與實(shí)際系統(tǒng)相似的半主動(dòng)升沉補(bǔ)償模型系統(tǒng)

2018-03-13 15:38:06 1

1 node-auth-basic.atsln項(xiàng)目是一個(gè)一體化示例,它演示了使用CryptoAuthenticationlM器件(例如,ATECC508A)的公鑰、非對(duì)稱(chēng)技術(shù)的節(jié)點(diǎn)驗(yàn)證序列的各個(gè)階段。

2018-03-21 11:12:13 1

1 異步FIFO廣泛應(yīng)用于計(jì)算機(jī)網(wǎng)絡(luò)工業(yè)中進(jìn)行異步數(shù)據(jù)傳送,這里的異步是指發(fā)送用一種速率而接收用另一速率,因此異步FIFO有兩個(gè)不同的時(shí)鐘,一個(gè)為讀同步時(shí)鐘,一個(gè)為寫(xiě)同步時(shí)鐘。

2019-06-11 08:00:00 2788

2788

設(shè)計(jì)工程師通常在FPGA上實(shí)現(xiàn)FIFO(先進(jìn)先出寄存器)的時(shí)候,都會(huì)使用由芯片提供商所提供的FIFO。但是,由于其通用性使得其針對(duì)性變差,某些情況下會(huì)變得不方便或者將增加硬件成本。此時(shí),需要進(jìn)行自行

2018-11-28 08:10:00 6709

6709

非對(duì)稱(chēng)密鑰加密通過(guò)提供一種機(jī)制來(lái)驗(yàn)證交易的完整性和真實(shí)性,同時(shí)允許交易保持公開(kāi),從而在彼此不了解或彼此不信任的用戶(hù)之間實(shí)現(xiàn)信任關(guān)系。

2019-01-25 11:23:43 1312

1312 根據(jù)FIFO工作的時(shí)鐘域,可以將FIFO分為同步FIFO和異步FIFO。同步FIFO是指讀時(shí)鐘和寫(xiě)時(shí)鐘為同一個(gè)時(shí)鐘。在時(shí)鐘沿來(lái)臨時(shí)同時(shí)發(fā)生讀寫(xiě)操作。異步FIFO是指讀寫(xiě)時(shí)鐘不一致,讀寫(xiě)時(shí)鐘是互相獨(dú)立的。

2019-11-29 07:08:00 1609

1609 Steam最近發(fā)布了一項(xiàng)“遠(yuǎn)程同樂(lè)(Remote Play Together)”的功能,該功能將支持允許用戶(hù)聯(lián)網(wǎng)體驗(yàn)本地多人游戲。這一功能同時(shí)支持非對(duì)稱(chēng)VR內(nèi)容,你可以用頭顯進(jìn)行游戲,而朋友則作為

2019-11-22 09:23:32 995

995 當(dāng)前密碼學(xué)中的加密解密方式主要能分成兩類(lèi),分別是對(duì)稱(chēng)加密和非對(duì)稱(chēng)加密。這兩個(gè)加密體系的構(gòu)成都是一樣的,都包括:加解密算法、加密密鑰、解密密鑰。

2019-11-29 11:36:23 2148

2148 所謂非對(duì)稱(chēng)PWM輸出模式它是相對(duì)基于中心對(duì)稱(chēng)計(jì)數(shù)時(shí)的對(duì)稱(chēng)PWM輸出而言的。當(dāng)計(jì)數(shù)模式為中心對(duì)齊,某個(gè)輸出通道利用一個(gè)比較寄存器做PWM輸出時(shí),其對(duì)應(yīng)的PWM輸出波形呈中心對(duì)稱(chēng),如下圖所示:

2020-05-14 09:21:58 8759

8759

FPGA電路FIFO設(shè)計(jì)的源代碼

2020-07-08 17:34:37 15

15 提出了一種節(jié)能并可升級(jí)的異步FIFO的FPGA實(shí)現(xiàn)。此系統(tǒng)結(jié)構(gòu)利用FPGA內(nèi)自身的資源控制時(shí)鐘的暫停與恢復(fù),實(shí)現(xiàn)了高能效、高工作頻率的數(shù)據(jù)傳輸。該系統(tǒng)在Xilinx的VC4VSX55芯片中實(shí)現(xiàn),實(shí)際

2021-02-02 15:15:00 16

16 介紹一款非對(duì)稱(chēng)多諧振蕩器電路圖。

2021-03-17 10:06:38 13

13 相似關(guān)系出現(xiàn)非對(duì)稱(chēng)情況。為了能夠更好地度量用戶(hù)之間的相似關(guān)系,首先在均方差相似度公式的基礎(chǔ)上,引入非對(duì)稱(chēng)系數(shù)刻畫(huà)相似度的非對(duì)稱(chēng)性;然后根據(jù)元路徑的特征賦予不同元路徑權(quán)重,并將不同元路徑的相似度結(jié)果進(jìn)行加權(quán)以提

2021-04-13 10:57:57 3

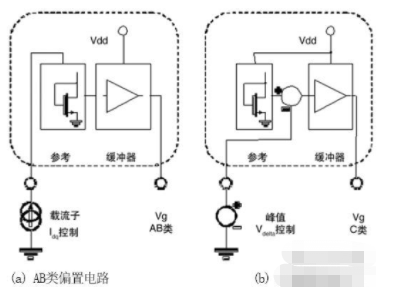

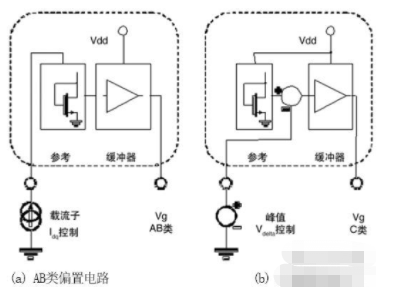

3 現(xiàn)有設(shè)計(jì)要與更高性能的放大器之間實(shí)現(xiàn)平滑過(guò)渡,必須采用下列設(shè)計(jì)選項(xiàng):在載頻和峰值器件之間應(yīng)用1dB非對(duì)稱(chēng)電平,優(yōu)化內(nèi)部匹配網(wǎng)絡(luò)來(lái)允許寬帶放大器設(shè)計(jì)(是規(guī)定帶寬的3倍)。此外,為提高視頻帶寬(VBW),減少對(duì)存儲(chǔ)器的影響,抑制調(diào)整和簡(jiǎn)化放大器設(shè)計(jì)人員的現(xiàn)場(chǎng)工作,專(zhuān)門(mén)設(shè)計(jì)了特定偏置電路,集成在晶體管中。

2021-05-05 11:12:00 1573

1573

基于非對(duì)稱(chēng)注意力機(jī)制殘差網(wǎng)絡(luò)的圖像檢測(cè)

2021-07-05 15:29:13 8

8 FIFO是在FPGA設(shè)計(jì)中使用的非常頻繁,也是影響FPGA設(shè)計(jì)代碼穩(wěn)定性以及效率等得關(guān)鍵因素。在數(shù)據(jù)連續(xù)讀取時(shí),為了能不間斷的讀出數(shù)據(jù)而又不導(dǎo)致FIFO為空后還錯(cuò)誤的讀出數(shù)據(jù)。可以將FIFO

2021-09-09 11:15:00 6293

6293 當(dāng)今世界,網(wǎng)絡(luò)安全問(wèn)題比以往任何時(shí)候都更需認(rèn)真對(duì)待。 本文是屬于《網(wǎng)絡(luò)安全》系列文章之一,我們將詳細(xì)闡述了安全性的基礎(chǔ)知識(shí)。在本文中,我們將闡述非對(duì)稱(chēng)加密的原理,這是確保真實(shí)性、完整性和保密性的唯一方法。

2022-04-07 09:46:58 1684

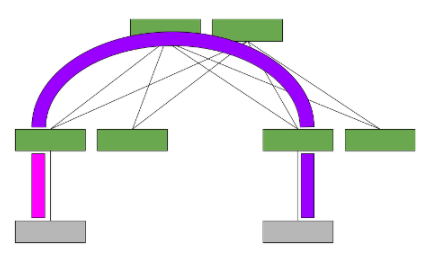

1684 如果您的數(shù)據(jù)中心可以分解為包含 VLAN 和子網(wǎng)的 Pod ,那么非對(duì)稱(chēng)模型也可以很好地工作。 Pod 中的每個(gè)葉都配置了本地 Pod 中的所有 vlan 和子網(wǎng)或 VNIs 。其他 pod

2022-04-08 15:29:26 2024

2024

非對(duì)稱(chēng)封裝的電源芯片的焊盤(pán)和鋼網(wǎng)設(shè)計(jì)建議

2022-10-28 11:59:44 0

0 FIFO的分類(lèi)根均FIFO工作的時(shí)鐘域,可以將FIFO分為同步FIFO和異步FIFO。同步FIFO是指讀時(shí)鐘和寫(xiě)時(shí)鐘為同一個(gè)時(shí)鐘。在時(shí)鐘沿來(lái)臨時(shí)同時(shí)發(fā)生讀寫(xiě)操作。異步FIFO是指讀寫(xiě)時(shí)鐘不一致,讀寫(xiě)時(shí)鐘是互相獨(dú)立的。

2022-11-01 09:57:08 1315

1315 同步FIFO的意思是說(shuō)FIFO的讀寫(xiě)時(shí)鐘是同一個(gè)時(shí)鐘,不同于異步FIFO,異步FIFO的讀寫(xiě)時(shí)鐘是完全異步的。同步FIFO的對(duì)外接口包括時(shí)鐘,清零,讀請(qǐng)求,寫(xiě)請(qǐng)求,數(shù)據(jù)輸入總線,數(shù)據(jù)輸出總線,空以及滿信號(hào)。

2022-11-01 09:58:16 1189

1189 使用 FSFA 系列飛兆電源開(kāi)關(guān) (FPS?) 設(shè)計(jì)具有電流倍增器和同步整流器的非對(duì)稱(chēng) PWM 半橋轉(zhuǎn)換器

2022-11-14 21:08:34 2

2 非對(duì)稱(chēng)雙 Power33 封裝的組裝指南

2022-11-15 19:33:26 0

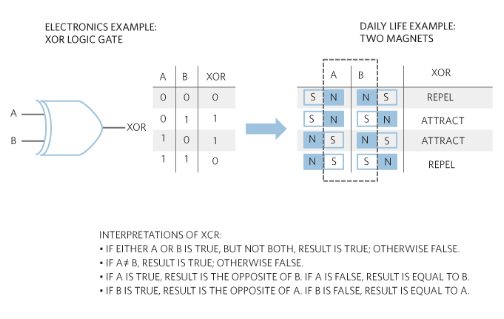

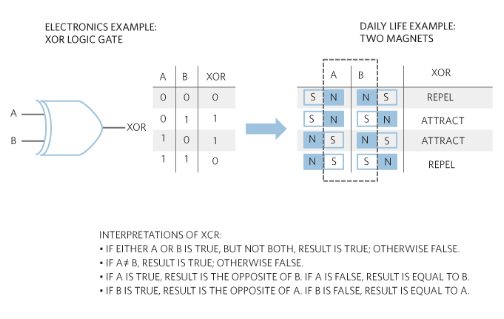

0 在我們的密碼學(xué)系列教程的最后兩期中,我們介紹了密碼學(xué)的基本概念和兩種基本類(lèi)型。本節(jié)討論最常見(jiàn)的加密算法的具體實(shí)現(xiàn)細(xì)節(jié),從基本的 XOR 函數(shù)開(kāi)始,然后進(jìn)入當(dāng)今使用的更復(fù)雜的對(duì)稱(chēng)和非對(duì)稱(chēng)算法。本文最后

2022-12-19 15:28:52 1261

1261

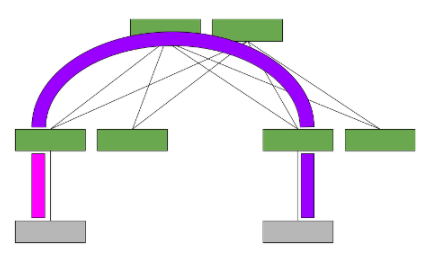

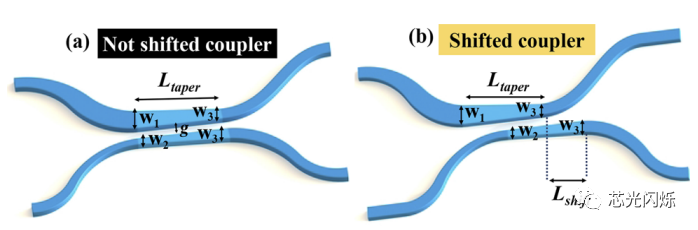

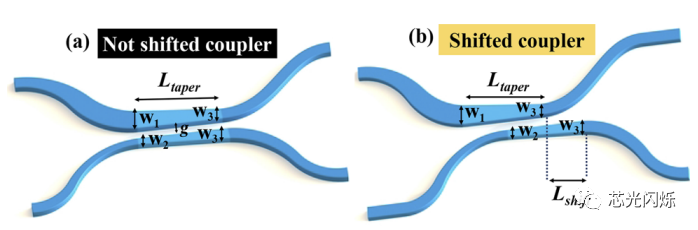

實(shí)現(xiàn)了一種基于非均勻非對(duì)稱(chēng)定向耦合器的新型寬帶波長(zhǎng)平坦3dB光耦合器。在1300-1600nm波長(zhǎng)范圍內(nèi),實(shí)現(xiàn)了3 dB± 0.3 dB的分束比。

2023-05-30 17:04:26 1008

1008

FIFO 是FPGA設(shè)計(jì)中最有用的模塊之一。FIFO 在模塊之間提供簡(jiǎn)單的握手和同步機(jī)制,是設(shè)計(jì)人員將數(shù)據(jù)從一個(gè)模塊傳輸?shù)搅硪粋€(gè)模塊的常用選擇。

2023-06-14 08:59:29 223

223 ? FIFO 是FPGA設(shè)計(jì)中最有用的模塊之一。FIFO 在模塊之間提供簡(jiǎn)單的握手和同步機(jī)制,是設(shè)計(jì)人員將數(shù)據(jù)從一個(gè)模塊傳輸?shù)搅硪粋€(gè)模塊的常用選擇。 在這篇文章中,展示了一個(gè)簡(jiǎn)單的 RTL 同步

2023-06-14 09:02:19 461

461 簡(jiǎn)單的一種,其特點(diǎn)是輸入和輸出都與時(shí)鐘信號(hào)同步,當(dāng)時(shí)鐘到來(lái)時(shí),數(shù)據(jù)總是處于穩(wěn)定狀態(tài),因此容易實(shí)現(xiàn)數(shù)據(jù)的傳輸和存儲(chǔ)。 而異步FIFO則是在波形的上升沿和下降沿上進(jìn)行處理,在輸入輸出端口處分別增加輸入和輸出指針,用于管理數(shù)據(jù)的讀寫(xiě)。異步FIFO的輸入和輸出可同時(shí)進(jìn)行,中間可以

2023-10-18 15:23:58 790

790 為什么三相短路是對(duì)稱(chēng)故障?單相短路是非對(duì)稱(chēng)故障呢? 三相短路是對(duì)稱(chēng)故障,而單相短路是非對(duì)稱(chēng)故障,其根本原因在于電網(wǎng)中的相量關(guān)系和電壓分布。 首先,對(duì)稱(chēng)故障指的是三相之間的關(guān)系相同,而非對(duì)稱(chēng)故障指的是

2024-02-18 11:41:26 350

350  電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論