CW32L052支持DMA(Direct Memory Access),即直接內存訪問,無需CPU干預,實現高速數據傳輸。

2024-02-27 11:36:20 554

554 數據傳輸模塊

2024-03-15 10:23:31

通過u***傳輸數據給fpga時,數據能不能以二進制的形式傳輸,fifo的16位數據線每一位代表一個二進制數,而不是每八位代表一個數據??

2017-12-12 15:32:31

請問有沒有現成的以太網插件,比如NI DAQ之類的插件,可以將FPGA內FIFO的數據傳輸到電腦上的?

2016-09-25 15:00:32

進行高速數據傳輸有幾種方案我知道可以用雙口RAM 或者協議的方式 但是不知道還有沒有其他的方式要求之間的通信速度要快 相互之間進行數據的交換其實就是FPGA把數據交給DSP進行處理 處理完了之后再有FPGA進行實時的圖像顯示而已

2012-08-06 10:56:57

我最近在做fpga 與pc機網口數據傳輸。 目前的想法是用lwipdemo來做。 已經調試出來了。 可以實現里面所有的功能。 現在,本人想在此基礎上進行修改,從而可以隨意的發送自己的包。做過相關工作的同學額可以相互交流一下。

2013-09-16 14:19:01

性問題,而且用FPGA實現的FIFO更容易修改和測試,可以降低成本和縮短開發周期。1 像素數據傳輸定時分析像素數據傳輸時序如圖1所示,像素數據傳輸在CLK的同步下進行,每次傳送256×2 bit

2015-01-28 14:47:10

USB通用串行總線(Universal Serial Bus),目前我們所說的USB一般都是指USB2.0,USB2.0接口是目前許多高速數據傳輸設備的首選接口,從1.1過渡到2.O,作為其重要指標

2019-05-27 07:32:44

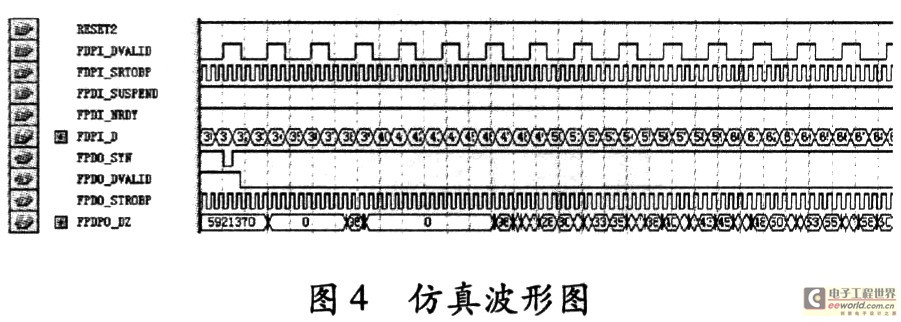

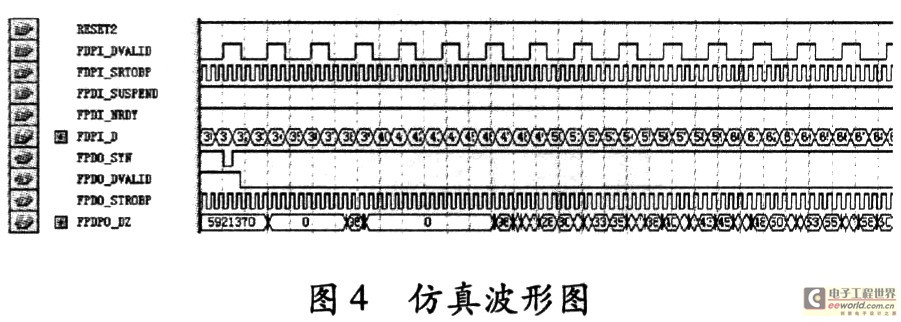

ADSP-21065L的片內RAM來中轉,然后再完成高速緩存到海量緩存的數據傳輸,具體做法如圖4所示。 ADSP內部開設有1k32bit的RAM塊構成中轉區,可利用外部口DMA通道0進行A/D高速緩存到片內

2020-12-04 15:59:14

LabVIEW編程LabVIEW開發高級數據采集技術 數據傳輸方式 例程與相關資料備NI-DAQmx驅動程序的傳統多功能DAQ和智能DAQ之間的最大差異在于:數據傳輸的執行方式。 NI-DAQmx

2022-01-16 20:29:26

的可靠性保證吧)!?應該使用什么協議才能夠實現可靠且速度高的數據傳輸呢!?或者,怎么樣的方式才能實現高速傳輸呢!?跪求大神指點啊!!!!

2013-11-07 16:46:49

ROHM公司日前研發了高速數據傳輸方式的Ir Simple-4M規格的控制器LSI,據稱其速度相當于現行IrDA標準傳輸(IrDA-115k方式)速度的50倍,數據傳輸速率為IrDA-4M方式的4

2018-11-19 16:51:08

有關Zynq-7000里面ARM和FPGA數據傳輸是怎么實現的?求大神解答

2022-07-25 14:42:00

openmv與STM32之間的數據傳輸怎么實現?

2021-12-13 07:35:00

wireline高速數據傳輸的均衡技術

2020-12-23 06:07:55

隨著存儲技術的迅速發展,存儲容量得到了迅速的增長,存儲系統的數據傳輸速度成為了主要的瓶頸。光纖的傳輸具有其速度上的優勢,然而,在光纖傳輸要受到光纖通道接口的限制,因此光纖通道應用于高速數據傳輸的一個關鍵技術問題是接口的設計問題,本文對有效地解決高數據傳輸在接口處的瓶頸具有現實意義。

2019-08-22 08:06:39

FPGA選用的是XC3S1600E,使用XCF08PFSG48C進行配置,選用并行數據傳輸時,XCF08PFSG48C的片選信號CE一直處于低電平,不跳高,但其他都正常,是怎么回事?

2013-09-04 13:33:49

異步fifo是用于跨時域時鐘傳輸的,但是同步fifo做緩存我就不是很理解了,到底這個緩存是什么意思,這樣一進一出,不是數據的傳輸嗎,為什么加個fifo,還有,如果是兩組視頻流傳輸,在切換的過程中如何能保證無縫切換?希望哪位好心人幫我解答一下

2013-08-27 19:23:36

嗨,我們可以通過微網格設計實現高速數據傳輸嗎?我正在使用Microlaze連接Aurora(3.125 Gbps)。數據正在轉移,這在console和ILA上得到驗證。但我怎樣才能確保數據速率為3.125 Gbps?微纖維以100 MHz運行。

2020-08-26 14:35:29

圖像數據傳輸卡的原理是什么?圖像數據傳輸卡的實現方法是什么?

2021-06-04 06:51:18

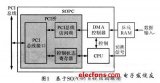

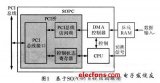

Interface,外部存儲器接口)可以實現片內RAM、片內和片外設備以及兩個片外設備之間的數據傳輸。dMAX模塊的內部結構如圖1所示。圖1 dMAX內部結構圖從圖中可以看出,dMAX主要由事件和中斷處理

2011-07-25 09:13:51

高度集成的靈活特性,滿足本設計的高速數據傳輸要求。其USB3.0模塊功能框圖如下圖1所示。圖 1 USB3.0模塊功能框圖本設計中,將USB3.0模塊作為從器件,從器件FIFO接口如圖2所示。該接口允許

2018-08-09 14:18:42

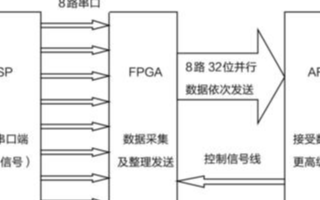

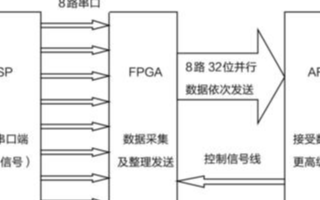

過DSP進行處理,DSP和FPGA相結合可以提高數據傳輸的效率。FPGA實現數據的串并轉換以及數據的拼接并對數據打包成符合1394b協議的數據包類型以及配置數據包的包頭信息,經過讀/寫FIFO并在

2012-05-14 12:35:39

高速LVDS數據傳輸方案和協議基于FPGA的高速LVDS數據傳輸本人在北京工作6年,從事FPGA外圍接口設計,非常熟悉高速LVDS數據傳輸,8B/10B編碼等,設計調試了多個FPGA與FPGA以及

2014-03-01 18:47:47

的網絡數據傳輸。3、 系統結構高速同步數據采集系統主要包括以下幾個部分:ARM控制器、存儲電路、FPGA邏輯控制電路、A/D轉換電路、FIFO緩存、電源電路、接口電路等。系統具備多通道數據采集接口

2010-08-31 09:14:55

基于DSP與PC機的PCI總線高速數據傳輸資料解析,不看肯定后悔

2021-06-03 06:47:49

外部主控制器實現對FX2 USB內部的FIFO進行控制,以實現數據的高速傳輸。該模塊可普遍適用于基于USB 2.0接口的高速數據傳輸或采集中。l 系統硬件模塊設計1.1 系統硬件框圖圖1中展示了

2021-06-24 07:00:00

嗨, 我正在使用Saturn Spartan6 numato板。我在董事會中實現了一個非常簡單的要求版本。現在我想將數據傳輸到FPGA或從FPGA傳輸到PC。請提出一些建議。謝謝。

2019-07-31 10:36:37

你好,我正在嘗試實現一個USB麥克風(用于測試ADC精度和USB特性)設備,PSoC枚舉工作良好。我無法找到任何有關如何實現ISO數據傳輸的文檔。我嘗試使用USPFSY1LoLoNEPEP API

2019-03-26 13:10:04

本文設計的基于FPGA和USB的高速數據傳輸、記錄系統不但具有體積小、功耗低、成本低、使用靈活方便、硬件電路簡單、可在線更新等特點;而且還充分利用了微機的資源,因而易開發且擴展性好。

2021-04-30 06:50:49

什么是LVDS技術?其有什么優勢?MAX9205和MAX9206的工作原理和工作模式是什么?如何去實現一種遠端高速數據傳輸系統的設計?

2021-06-02 06:10:56

無法將數據從Coordinator傳輸到EndDevice。雖然模板提供了數據傳輸的功能,但它并沒有告訴我如何以及在哪里調用該功能。所以我需要你幫助告訴我如何正確實現EndDevice和Coordinator之間的數據傳輸

2023-03-24 08:38:45

FIFO的數據讀寫不需要DSP的CPU參與,從而提高整個系統性能,實現數據交換和數據處理的同時進行。如何設計嵌入式FIFO數據傳輸系統?該怎么進行設計、配置及其使用?這些問題誰知道答案嗎?

2019-08-08 07:03:56

本文提出一種采用FPGA和CMOS數字傳感器實現前端數據采集、利用單片機進行圖像鑒別和壓縮、通過以太網控制器實現圖像數據傳輸的圖像監測系統。該系統不僅實現了圖像信號數據采集,而且數據傳輸速度和穩定性高;不僅靈活性好、成本低,而且具有網絡化、智能化等優點。

2021-05-26 06:58:29

:GWDZ.0.2010-02-036【正文快照】:Internet是人們學習、生活、工作中獲取和傳輸信息的重要途徑,而網絡應用對數據傳輸的實時性提出更高要求,因此,需要新型高速的網絡協議支持。RTP/RTCP協議、RTSP協議

2010-04-24 09:31:00

本文介紹了基于Xilinx Virtex-6 FPGA的高速串行數據傳輸系統的設計與實現,系統包含AXI DMA和GTX串行收發器,系統增加了流量控制機制來保證高速數據傳輸的可靠性。最后進行了仿真測試,測試結果顯示系統可以高速可靠地傳輸數據。

2021-05-25 06:45:36

移動無線傳輸數據的方式有哪幾種?怎么實現基于CDMA的移動無線數據傳輸系統的設計?

2021-05-28 06:36:18

怎么實現基于iNEMO模塊的姿態檢測及數據傳輸系統設計?

2021-05-19 06:06:01

大家好。現在我可以用評估板運行奴隸FIFO異步示例。我仍然想知道如何檢查從FIFO GPIF的傳輸速度。使用UART調試器,我發現在從FIFO異步示例中數據傳輸不是那么快。如何提高傳輸速度和最大傳輸

2019-04-29 14:10:58

結合高速嵌入式數據采集系統,提出一種基于CvcloneⅢ FPGA實現的異步FIFO和鎖相環(PLL)結構來實現高速緩存,該結構可成倍提高數據流通速率,增加數據采集系統的實時性。采用FPGA設計高速緩存,能針對外部硬件系統的改變,通過修改片內程序以應用于不同的硬件環境。

2021-04-30 06:19:52

用FPGA 控制W5300(采用的是TCP/IP協議)進行數據傳輸,上位機軟件用LABVIEW做!怎么才能進行數據傳輸。W5300怎么與LABVIEW進行數據傳輸!!各位大仙能不能給指明方向!謝謝

2014-12-30 19:29:00

過程時不可能像PL端那樣能實現精準的時序控制,為了實現整個DMA數據傳輸的有效進行,需要明白數據傳輸的整個過程。以下面工程為例來對傳輸過程進行描述。如上圖所示主要是完成PS端數據通過DMA到axis_data_fifo中,然后把axis_data_fifo中數據通過DMA傳輸到PS端,實現數據的回環傳輸。首

2022-01-07 06:22:51

數據傳輸模塊可以對系統采集的數據進行傳輸,幫助系統實現對安防信息的采集處理。二、、智慧能源環保智慧能源環保屬于智慧城市的一個部分,其物聯網應用主要集中在水能,電能,燃氣、路燈等能源以及井蓋、垃圾桶等環保

2019-06-18 04:21:52

和labview做下中轉。1,NI的哪個板卡可以實現這個功能? 只要一個通道的PT100采集2,labview接受板卡的速度可以達到或超過1ms1次吧?3,labview如何高速的將數據傳輸給執行器?執行器支持485通訊和網口通訊。

2018-06-16 09:09:34

本帖最后由 一只耳朵怪 于 2018-6-25 10:07 編輯

貴公司目前只推出了開發板,上面只有一個dsp芯片,怎么驗證Hyperlink的片間數據傳輸功能?

2018-06-25 06:23:42

曼徹斯特解碼,并送到音頻輸出接口。程序由3個線程構成,當數據傳輸服務程序在手機上啟動后形成,應用嵌入式系統和控制軟件實現數字數據的編解碼,數據信號在主控模塊中進行編解碼處理,再通過控制裝置讀取、寫入外部

2019-06-21 05:00:10

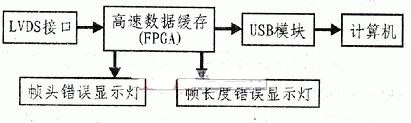

提出了一種紅外敏感器半實物仿真系統中多路實時數據傳輸與采集系統的設計方法,采用FPGA 內的SRAM 塊實現所要傳輸與采集數據的緩沖存儲,并通過高速USB2.0 接口芯片實現與主機的

2009-08-04 14:36:21 17

17 針對LVDS高速數據傳輸,本文分析并比較了三種有效的傳輸方案。結合這些方案的特點和合成孔徑雷達成像的需求,本文實現了使用高速時鐘采樣進行同步接收的LVDS傳輸方案。該

2009-08-26 09:04:12 15

15 本文通過一套數據采集卡的設計介紹了PCI 總線數據傳輸的基本過程,給出了系統整體設計方案和PCI 接口通信方式及驅動程序實現,并著重討論了PCI 數據傳輸中影響傳輸速率的

2009-09-21 10:19:54 34

34 DVI[1]接口標準作為新一代的數字顯示技術通訊標準,以全數字化的數據碼流在傳輸信道上傳輸,本文針對DVI 接口標準提出了一種基于FPGA 的高速實時的數據傳輸方案。方案中重

2009-09-22 10:12:34 15

15 為解決目前高速信號處理中的數據傳輸速度瓶頸以及傳輸距離的問題,設計并實現了一種基于FPGA 的高速數據傳輸系統,本系統借助Altera Cyclone III FPGA 的LVDS I/O 通道產生LVDS 信號,穩

2010-11-02 15:27:43 42

42

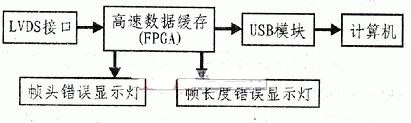

摘要:提出了一種基于FPGA和USB的高速數據傳輸、記錄及顯示系統的設計方案,并對其中的低電壓差分信號(LVDS

2006-04-16 21:36:33 584

584

基于FPDP的高速數據傳輸系統設計

隨著電子技術的高速發展,越來越多的信號處理系統,需要高速的數據采集和大吞吐量的數據傳輸,來實現數據的高速實時處理能力。

2009-12-01 09:41:44 2031

2031

什么是U盤的數據傳輸率

便攜存儲是依靠USB接口與系統相連,其接口的速度就限制著移動硬盤的數據傳輸率。目前的US

2010-01-30 10:21:25 622

622 數據傳輸速率是什么意思

數據傳輸速率是通過信道每秒可傳輸的數字信息量的量度。數據傳輸速率也稱為吞吐率。數據傳輸速率由很

2010-03-18 14:45:20 4934

4934 什么是數據傳輸中的成幀

數據傳輸中的成幀

成幀技術是一種用來在一個比特流內分配或標記信道的技術,為電信提供選擇基本的時隙結構和管理方式、錯誤

2010-03-18 14:46:33 3654

3654 本文介紹了基于C6727B的dMAX的基本結構以及基于dMAX的嵌入式FIFO軟硬件設計,設置通用GPIO引腳作為中斷,為了加快FIFO的傳輸速率,使用突發讀寫方式進行數據傳輸

2011-05-12 10:00:20 1622

1622

本文以dMAX和EMIF接口的數據傳輸為例,介紹嵌入式FIFO的設計、配置及其使用。

2011-06-23 17:19:13 1106

1106

基于USB2.0 的FIFO 方式, 利用FPGA 同步實現三個通道, 不同傳輸率的數據的發送和采集, 詳細說明多路數據發送與采集時,對不同數據傳輸速率的實現方法以及部分硬件和軟件設計, 最后, 簡要

2011-09-13 17:22:34 65

65 本文提出一種采用可編程片上系統SOPC實現偵察接收機PCI總線高速數據傳輸系統的設計方案。

2012-02-10 11:20:05 1350

1350

一種基于FPGA的IPv6主機數據傳輸模塊設計

2016-01-04 15:31:55 10

10 一種基于FPGA的以太網高速傳輸平臺,采用DM9000和FPGA芯片,實現100M以太網數據傳輸

2016-02-25 14:45:56 17

17 高速數據傳輸在家具生產設備上的應用

2017-02-07 18:09:20 10

10 分享下PS與PL之間數據傳輸比較另類的實現方式,實現目標是: 1、傳輸時數據不能滯留在一端,無論是1個字節還是1K字節都能立即發送; 2、PL端接口為FIFO接口; PS到PL的數據傳輸流程: PS

2017-02-08 01:00:11 1431

1431

基于ARM處理器和FPGA在數據傳輸中的應用與研究

2017-10-15 10:28:49 4

4 基于DSP和USB2_0高速數據傳輸系統的設計

2017-10-19 14:44:03 7

7 基于EDMA實現TMS320C64X與FPGA的數據傳輸

2017-10-21 10:14:09 4

4 項目發展的重要因素,對比發現,U DP 協議相較于TCP 協議而言,在可靠性上雖有欠缺,但在傳輸速率上占有一定優勢,更加適合高速率數據傳輸的場景。而基于FPGA 的應用相較于傳統的軟件實現而言可以節省CPU 資源,并且可使系統集成

2017-10-28 09:51:39 139

139 為了滿足2ynq-7000系列芯片的SRIO數據傳輸要求,提出了一種基于FPGA控制DMA傳輸進行SRIO通信的設計方案,并完成了ARM與FPGA核間高吞吐率的數據交互操作。系統的FPGA部分主要

2017-12-21 11:37:03 30

30 、預加重和均衡等技術,保證了數據傳輸的穩定性和同步性。保證采用UTP-5 雙絞線為傳輸介質時傳輸速率不低于400Mbps,傳輸距離為50 米時上的,實現低成本的遠距離高速數據傳輸。

2018-08-26 09:29:25 1552

1552

整個系統主要由低電壓差分信號(LVDS)接口電路、基于FPGA的高速數據緩存、判斷數據錯誤模塊、USB傳輸模塊和計算機組成,其系統結構框圖如圖1所示。當低電壓差分信號接口電路把接收的雷達數據形成分機數據送入FPGA緩存后,該信息便可通過USB接口進行傳輸、記錄并在計算機上顯示。

2019-05-16 08:14:00 3637

3637

為了實現高速數據傳輸,實時傳感器數據必不可少,因此需要最優的信號完整性 (SI) 與電磁兼容性 (EMC)。

2018-11-27 15:29:38 4561

4561

Frost&Sullivan發現,將5G集成到工業物聯網(IIoT)系統中將有助于該技術發展,以實現高速,低延遲和大容量數據傳輸。

2020-06-01 16:48:01 3049

3049 隨著集成電路技術的發展,FPGA和DSP以及ARM以其體積小、速度快、功耗低、設計靈活、利于系統集成、擴展升級等優點,被廣泛地應用于高速數字信號傳輸及數據處理,以DSP+FPGA+ARM的架構組成滿足實時性要求的高速數字處理系統已成為一種趨勢,本文主要研究FPGA在高速多路數據傳輸中的應用。

2021-04-24 09:04:49 4553

4553

問題,提出一種可實現高精度時間同步的數據傳輸方法。借助 TCP/IP協議棧和 White rabbit時鐘同步技術融合時鐘網絡與數據網絡,TCP/P協議棧在僅保留PC通信協議的基礎上,無需增加額外硬件,即可實現高效可靠的數據傳輸和高精度時鐘同步。測試結果表明,該方

2021-05-11 13:57:43 20

20 基于提升數據傳輸速率,提高數據傳輸實時性的目的,提出了一種基于UDP協議的點到點數據傳輸方案,并采用現場可編程邏輯門整列(FPGA)和以太網PHY芯片RIL821EG實現點到點的UDP高速數據傳輸

2021-06-01 09:58:33 12

12 在FPGA中對圖像的一行數據進行緩存時,可以采用FIFO這一結構,如上圖所示,新一行圖像數據流入到FIFO1中,FIFO1中會對圖像數據進行緩存,當FIFO1中緩存有一行圖像數據時,在下一行圖像數據來臨的時候,將FIFO1中緩存的圖像數據讀出,并傳遞給下一個FIFO

2022-05-10 09:59:29 3056

3056 數據傳輸技術主要用于多機通信領域,一般在數據交換過程中,為保證數據的穩定可靠傳輸而制定的特殊傳送規則。其傳輸過程也根據傳輸的物理介質而不同。

2023-02-22 11:14:25 1021

1021 數據傳輸方式是數據在信道上傳送所采取的方式。若按數據傳輸的順序可以分為并行傳輸和串行傳輸;若按數據傳輸的同步方式可分為同步傳輸和異步傳輸;若按數據傳輸的流向和時間關系可以分為單工、半雙工和全雙工數據傳輸。下面跟著科蘭布線小編一起詳細來了解一下吧。

2023-03-24 11:04:16 1109

1109 FIFO是異步數據傳輸時常用的存儲器,多bit數據異步傳輸時,無論是從快時鐘域到慢時鐘域,還是從慢時鐘域到快時鐘域,都可以使用FIFO處理。

2023-05-26 16:12:49 978

978

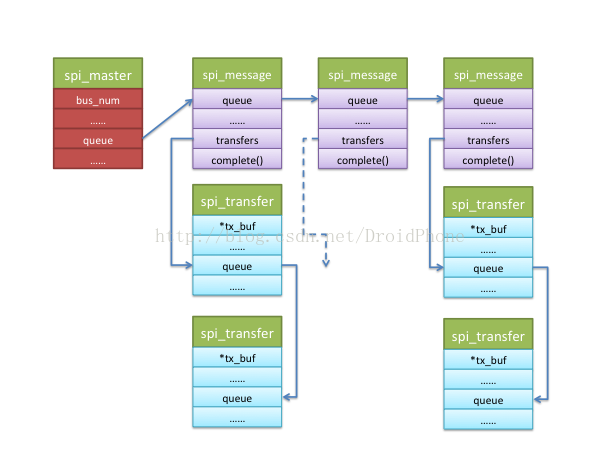

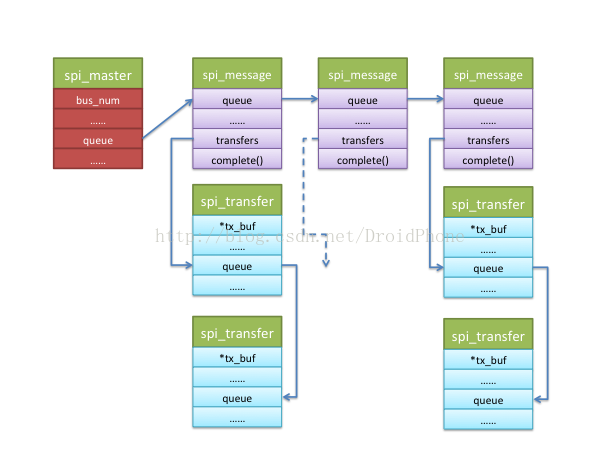

SPI 數據傳輸可以有兩種方式:同步方式和異步方式。 同步方式:數據傳輸的發起者必須等待本次傳輸的結束,期間不能做其它事情,用代碼來解釋就是,調用傳輸的函數后,直到數據傳輸完成,函數才會返回。 異步

2023-07-25 10:54:22 2899

2899

點擊上方 藍字 關注我們 本文設計的基于FPGA和USB的高速數據傳輸、記錄系統不但具有體積小、功耗低、成本低、使用靈活方便、硬件電路簡單、可在線更新等特點;而且還充分利用了微機的資源,因而易開發

2023-09-20 10:00:01 1452

1452

高速數據傳輸藍牙雙模方案 高速數據傳輸透傳模式是一種直接傳輸模式,數據通過藍牙模塊傳輸,不需要特定命令。 主控制器通過串口將數據發送給藍牙模塊,再傳輸給平臺。 平臺還可以將數據發送到藍牙模塊,再傳輸

2023-08-19 15:28:43 1

1 高速數據傳輸藍牙雙模方案 高速數據傳輸透傳模式是一種直接傳輸模式,數據通過藍牙模塊傳輸,不需要特定命令。 主控制器通過串口將數據發送給藍牙模塊,再傳輸給平臺。 平臺還可以將

2023-07-26 14:45:33

電子發燒友App

電子發燒友App

評論