xilinx verilog語法技巧 一 硬件描述語言(HDL)編碼技術(shù)讓您: ?描述數(shù)字邏輯電路中最常見的功能。 ?充分利用Xilinx?器件的架構(gòu)特性。 1 Flip-Flops

2020-12-13 10:29:00 3065

3065 今天給大俠帶來的是一周掌握FPGA Verilog HDL 語法,今天開啟第一天,下面咱們廢話就不多說了,一起來看看吧。

2022-07-18 09:47:40 2074

2074 今天給大俠帶來的是一周掌握FPGA Verilog HDL 語法,今天開啟第二天。上一篇提到了整數(shù)型以及參數(shù)型,此篇我們繼續(xù)來看變量以及后續(xù)其他內(nèi)容,結(jié)合實例理解理論語法,會讓你理解運用的更加透徹。下面咱們廢話就不多說了,一起來看看吧。

2022-07-18 09:52:36 1262

1262 Verilog 2005 版本支持使用省略位寬的方式賦值,’b,’d,’h,采用省略位寬的方式可以向左主動補齊,如果省略了進制符合b/d/h/o,則默認(rèn)是十進制。

2022-11-23 14:14:51 4427

4427 可綜合的語法是指硬件能夠?qū)崿F(xiàn)的一些語法,這些語法能夠被EDA工具支持,能夠通過編譯最終生成用于燒錄到FPGA器件中的配置數(shù)據(jù)流。

2023-07-23 12:25:10 770

770 Verilog HDL語法,要的拿

2016-01-24 22:53:48

Verilog HDL的基本語法 .pdf

2012-08-15 15:06:11

的語言。這也就是說,既可以用電路的功能描述也可以用元器件和它們之間的連接來建立所設(shè)計電路的Verilog HDL模型。Verilog模型可以是實際電路的不同級別的抽象。這些抽象的級別和它們對應(yīng)的模型類型

2019-09-06 09:14:16

Verilog 紅寶書_語法基礎(chǔ)(恒創(chuàng)科技原創(chuàng))

2013-09-27 22:02:08

本帖最后由 lee_st 于 2017-10-31 08:46 編輯

Verilog語法基礎(chǔ)講解之參數(shù)化設(shè)計

2017-10-21 20:56:17

Verilog比較細(xì)節(jié)的`語法

2012-09-17 23:47:41

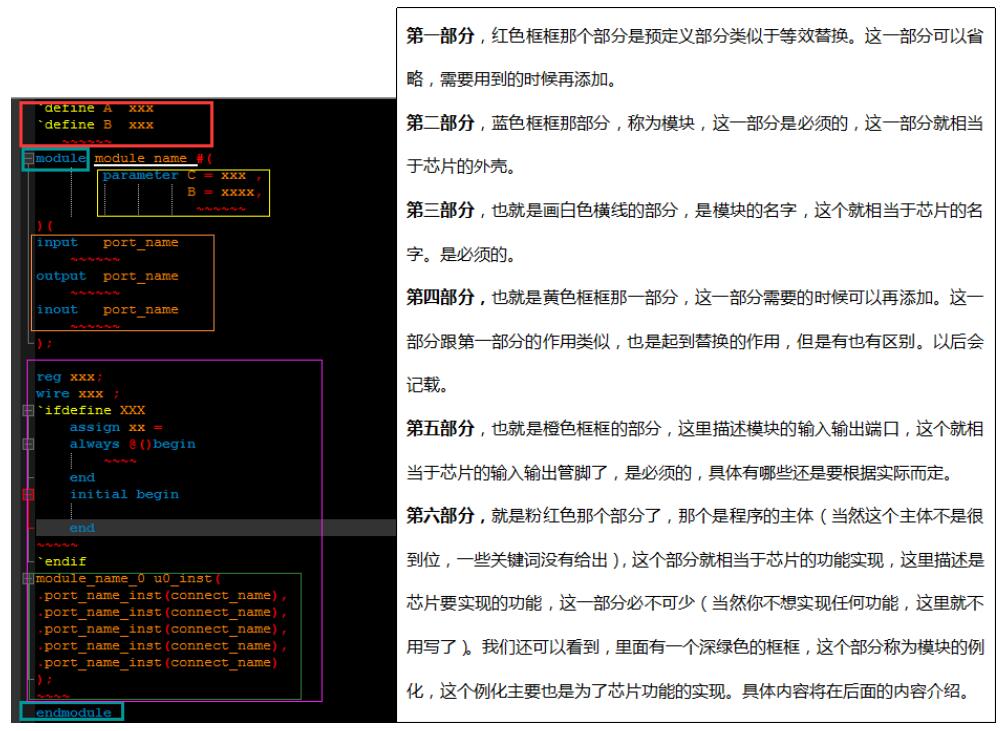

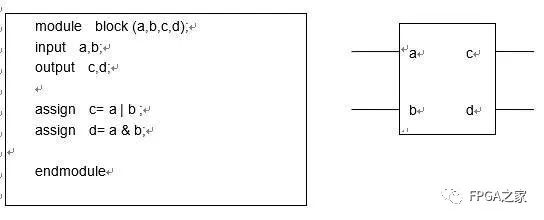

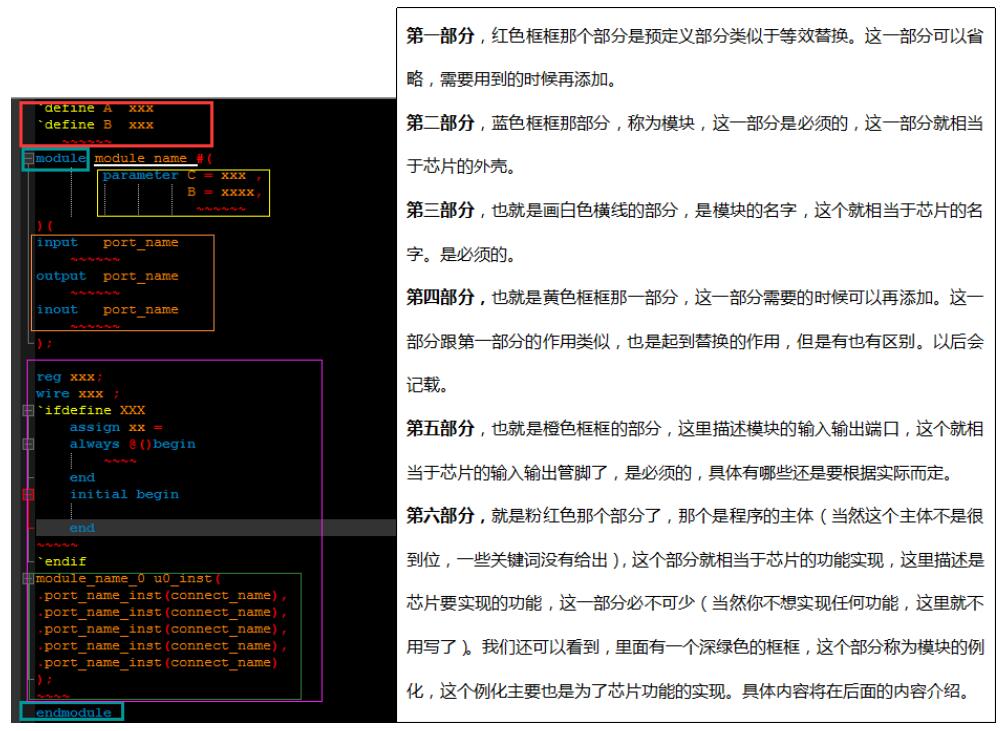

了解一下Verilog代碼的基本程序框架,這樣可以讓我們先對Verilog程序設(shè)計有一個整體的概念把握,進而在后續(xù)的Verilog語法學(xué)習(xí)中做到有的放矢。閱讀本節(jié)時請著眼于大體,而不要過分去苛求細(xì)節(jié)語法,細(xì)節(jié)的語法介紹將在后續(xù)的小節(jié)中慢慢展開。

2021-07-27 07:51:28

Verilog基礎(chǔ)語法

2021-05-27 08:00:00

本帖最后由 richthoffen 于 2021-3-3 10:30 編輯

Verilog紅寶書_語法篇_恒創(chuàng)科技出品 V1.0

2021-03-03 10:29:22

Verilog紅寶書_基本語法_上_恒創(chuàng)科技出品 V1.4

2016-10-09 08:55:47

Verilog紅寶書_基本語法_下_恒創(chuàng)科技出品 V1.1

2016-10-09 08:53:42

verilog 語法在復(fù)習(xí)進階

2013-09-19 08:18:00

verilog HDL語法總結(jié)

2020-03-16 14:26:27

verilog語法學(xué)習(xí)心得1.數(shù)字電路基礎(chǔ)知識: 布爾代數(shù)、門級電路的內(nèi)部晶體管結(jié)構(gòu)、組合邏輯電路分析與設(shè)計、觸發(fā)器、時序邏輯電路分析與設(shè)計2.數(shù)字系統(tǒng)的構(gòu)成: 傳感器AD數(shù)字處理器DA執(zhí)行部件3.

2012-01-12 15:15:21

verilog語法練習(xí)晉級篇

2016-09-02 13:40:12

verilog是什么?基本語法有哪些?

2021-09-18 07:41:04

FPGA-Verilog HDL語法參考語法規(guī)范下列規(guī)范應(yīng)用于語法描述,規(guī)則采用巴科斯—諾爾范式(B N F)書寫:1) 語法規(guī)則按自左向右非終結(jié)字符的字母序組織。2) 保留字、操作符和標(biāo)點標(biāo)記

2012-08-11 10:33:08

FPGA入門:Verilog/VHDL語法學(xué)習(xí)的經(jīng)驗之談 本文節(jié)選自特權(quán)同學(xué)的圖書《FPGA/CPLD邊練邊學(xué)——快速入門Verilog/VHDL》書中代碼請訪問網(wǎng)盤:http

2015-01-29 09:20:41

語法,這些語法能夠被EDA工具所支持,能夠通過編譯最終生成用于燒錄到FPGA器件中的配置數(shù)據(jù)流。無論是Verilog語言還是VHDL語言,可綜合的子集都很小。但是如何用好這些語法,什么樣的代碼風(fēng)格

2015-06-12 10:59:24

IMX OpenGL 著色器問題

2023-04-20 07:33:08

為什么我按照“基于M9K塊的單口RAM配置仿真實驗—LiangXuan-博客園的程序從頭做了一遍,發(fā)現(xiàn)dout輸出總是高阻態(tài),哪位大神能幫忙解決下嗎?感激不盡。在MegaWizard Plug-In Manager的配置上沒有那么詳細(xì),有沒有可能是這塊出了問題?求幫忙

2014-12-18 11:03:48

, 可以仔細(xì)閱讀這篇文章,了解一下Markdown的基本語法知識。新的改變我們對Markdown編輯器進行了一些功能拓展與語法支持,除了標(biāo)準(zhǔn)的Markdown編輯器功能,我們增加了如下幾點新功能,幫助你用它寫博客:全新的界面設(shè)計 ,將會帶來全新的寫作體驗;在創(chuàng)作中心設(shè)置你喜愛的代碼高亮樣式,Mark

2021-07-15 09:47:59

一下Markdown的基本語法知識。 ## 新的改變 我們對Markdown編輯器進行了一些功能拓展與語法支持,除了標(biāo)準(zhǔn)的Markdown編輯器功能,我們增加了如下幾點新功能,幫助你用它寫博客: 1.

2021-08-27 06:26:40

學(xué)習(xí)如何使用Markdown編輯器, 可以仔細(xì)閱讀這篇文章,了解一下Markdown的基本語法知識。(二)C語言程序代碼我們對Markdown編輯器進行了一些功能拓展與語法支持,除了標(biāo)準(zhǔn)的Markdown編輯器功能,我們增加了如下幾點新功能,幫助你用它寫博客:全新的界面設(shè)計 ,將會帶來全新的寫作體驗;在創(chuàng)作中心設(shè)置你喜

2021-07-14 08:38:45

嗨,我想用Modelsim XE來模擬我的設(shè)計。您能否提供以下有關(guān)Modelsim XE模擬器的信息或我可以找到這些信息的任何鏈接:-1。它是否支持系統(tǒng)verilog進行驗證?2。代碼覆蓋率支持.3

2018-11-27 14:20:41

本書主要講解verilog語法知識,只需看前7章,后面是例子。

2014-10-10 09:38:56

VHDL與verilog 的比較1vhdl語法要求嚴(yán)格 如賦值的數(shù)據(jù)類型必須一致, 左邊為整數(shù),右邊必須也為整數(shù), 左邊為矢量右邊必須也為矢量左右的數(shù)據(jù)的 位寬必須也一致,例如: library

2013-05-30 15:12:47

本帖最后由 eehome 于 2013-1-5 09:56 編輯

《Verilog HDL實驗練習(xí)與語法手冊》-夏宇聞

2012-08-09 14:09:08

、固核與硬核:1.3Verilog HDL設(shè)計流程:注:Verilog HDL語法的兩個部分第一章Verilog基礎(chǔ)知識1.1Verilog HDL開發(fā)的優(yōu)勢:語法簡單,可綜合性與系統(tǒng)仿真性能強,支持

2022-03-22 10:26:00

活動介紹:

每日一練活動主要針對 Verilog 入門常用語法及常用技巧的練習(xí),30個關(guān)于語法練習(xí)的題目,每天更新一個題目及公布前一天的參考答案及相關(guān)解析

活動規(guī)則:

每日一練活動結(jié)束后,根據(jù)參與

2023-08-01 10:37:52

我看不出來這個語法問題怎么修改,提示是說有語法錯誤。難道不是用parameter?

2013-09-17 21:28:18

。備注:1、各位也可以在ST官網(wǎng)查詢他們的GDB數(shù)據(jù)手冊,里面講的很清楚,也講了如何處理GDB報錯的問題。我截個圖2、原文在我個人的博客園那邊,有興趣也可以看一下關(guān)于STM32CubeIDE無法正常啟動GDB服務(wù)端的解決辦法 - 墨髯 - 博客園 (cnblogs.com)

2023-02-01 22:57:23

,是指硬件能夠?qū)崿F(xiàn)的一些語法,這些語法能夠被EDA工具所支持,能夠通過編譯最終生成用于燒錄到FPGA器件中的配置數(shù)據(jù)流。無論是Verilog語言還是VHDL語言,可綜合的子集都很小。但是如何用好這些語法

2017-12-06 19:50:25

可綜合的Verilog語法和語義(劍橋大學(xué),影印)

2012-08-06 13:03:57

嵌入式Linux開發(fā)環(huán)境搭建-安裝交叉編譯工具鏈1、下載2、解壓3、設(shè)置環(huán)境變量參考文檔ubuntu下安裝交叉編譯工具鏈 - emlslxl - 博客園arm交叉編譯器gnueabi

2021-11-05 08:02:27

`是否能夠、如何使用word發(fā)表發(fā)燒友論壇的個人博客?“博客園、新浪博客”都支持使用word發(fā)表,方便本地管理和更改,大大簡化排版工作!希望能給出官方教程啊!`

2014-08-19 11:26:30

本文轉(zhuǎn)載IC_learner - 博客園數(shù)字IC之路-SDC篇(一):基本的時序路徑約束_u012675910的博客-CSDN博客_sdc約束 RTL代碼描述了電路的時序邏輯和組合邏輯,即RTL代碼

2022-03-01 06:48:09

大部分教程都是針對HAL庫的。終于找到一篇教程之后,發(fā)現(xiàn)復(fù)制進去的庫在鏈接時會和PlatformIO自帶的庫沖突。這是我參考的文章:STM32F103 在VSCode下使用Platform IO 基于CMSIS標(biāo)準(zhǔn)庫函數(shù)開發(fā) - Zennn - 博客園 (cnblogs.com)研究一番之后,是因為syst

2022-01-07 06:08:48

有沒有verilog語法手冊可以方便查找

2013-04-18 17:47:10

[/td][td]C語言函數(shù)大全(語法著色版) --By NullC語言函數(shù)大全,已包含絕大部分的函數(shù)。每個函數(shù)包含函數(shù)名,功能,用法,舉例,內(nèi)容詳盡。

2012-07-28 00:21:20

至芯科技之a(chǎn)ltera 系列FPGA教程 第八篇 verilog基礎(chǔ)語法

2016-08-11 03:24:24

如題,剛好要用到I2C器件,發(fā)現(xiàn)沒有硬件支持.如果用GPIO端口模擬,軟件硬件需要注意點什么呢?比如是否需要用代碼專門處理GPIO.模擬成開漏的方式?我在博客園看到了一篇博客,博主說代碼適用于

2022-09-07 07:50:02

- 博客園https://www.cnblogs.com/wahahahehehe/p/16896184.html后續(xù)針對具體芯片型號再做詳細(xì)說明

2023-03-26 11:56:55

Verilog-HDL實踐與應(yīng)用系統(tǒng)設(shè)計本書從實用的角度介紹了硬件描述語言Verilog-HDL。通過動手實踐,體驗Verilog-HDL的語法結(jié)構(gòu)、功能等內(nèi)涵。在前五章,以簡單的實例列舉了Verilog-HDL的用法;

2009-11-14 22:57:40 146

146 用Verilog實現(xiàn)8255芯片功能

2010-11-03 17:06:09 144

144 什么是頂點著色單元 頂點著色單元是顯示芯片內(nèi)部用來處理頂點(Vertex)信息并完成著色工作的并行處理

2009-12-25 10:46:02 326

326 Synthesizable Verilog is a subset of the full Verilog HDL [9] that lies within the domain

2011-03-03 15:46:01 0

0 Verilog 黃金參考指南是Verilog 硬件描述語言及其語法語義合并以及將它應(yīng)用到硬件設(shè)計的一個簡明的快速參考指南 Verilog 黃金參考指南并不是要代替IEEE 的標(biāo)準(zhǔn)Verilog 語言參考手冊它不像

2011-12-26 15:03:06 0

0 可綜合的Verilog語法和語義(劍橋大學(xué),影印):第七版

2012-05-21 14:50:14 27

27 Verilog_HDL的基本語法詳解(夏宇聞版):Verilog HDL是一種用于數(shù)字邏輯電路設(shè)計的語言。用Verilog HDL描述的電路設(shè)計就是該電路的Verilog HDL模型。Verilog HDL既是一種行為描述的語言也是一種結(jié)

2012-10-08 14:48:31 0

0 verilog語言經(jīng)典教材,本書講解了verilog的基本語法和經(jīng)典例子等等。

2015-11-10 11:44:20 23

23 Verilog硬件描述語言參考手冊,Verilog語法內(nèi)容介紹

2015-11-12 17:20:37 0

0 Verilog HDL實驗練習(xí)與語法手冊-高教

2016-05-11 11:30:19 0

0 Verilog_HDL語言的學(xué)習(xí),為FPGA編程打下堅實的基礎(chǔ)

2016-05-19 16:40:52 12

12 12月15日,博客平臺WordPress宣布,所有基于WordPress框架的博客系統(tǒng)都將支持VR內(nèi)容。該博客框架系統(tǒng)將會支持360度圖片、360度視頻,允許通過電腦、手機以及VR頭顯進行瀏覽觀看。

2016-12-17 10:49:12 813

813 用圖的著色方法解決排課沖突問題_安衛(wèi)鋼

2017-03-20 09:29:12 0

0 學(xué)習(xí)verilog最重要的不是語法,“因為10%的語法就能完成90%的工作”,verilog語言常用語言就是always@(),if~else,case,assign這幾個了。

2018-03-26 14:06:00 2678

2678

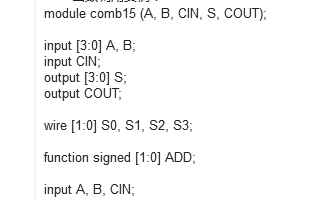

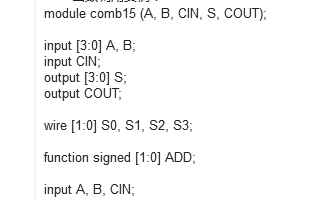

大家好,又到了每日學(xué)習(xí)的時間了,今天我們來聊一聊FPGA verilog中的function用法與例子。 函數(shù)的功能和任務(wù)的功能類似,但二者還存在很大的不同。在 Verilog HDL 語法中也存在

2018-08-10 13:42:16 18695

18695

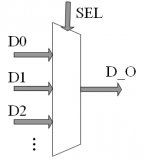

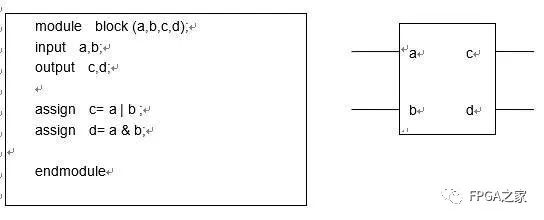

常見的Verilog描述語句與對應(yīng)的邏輯關(guān)系;熟悉語法與邏輯之間的關(guān)系

2018-09-15 08:18:03 9777

9777

本文檔的主要內(nèi)容詳細(xì)介紹的是UltraEdit MPASM語法著色文件免費下載。

2019-01-22 15:54:42 8

8 本文檔的主要內(nèi)容詳細(xì)介紹的是FPGA視頻教程之Verilog語法基礎(chǔ)的詳細(xì)資料說明資料免費下載

2019-03-01 11:35:00 16

16 Verilog HDL是一種用于數(shù)字系統(tǒng)設(shè)計的語言。用Verilog HDL描述的電路設(shè)計就是該電路的Verilog HDL模型也稱為模塊。Verilog HDL既是一種行為描述的語言也是一種結(jié)構(gòu)描述的語言。

2019-03-08 14:29:12 12094

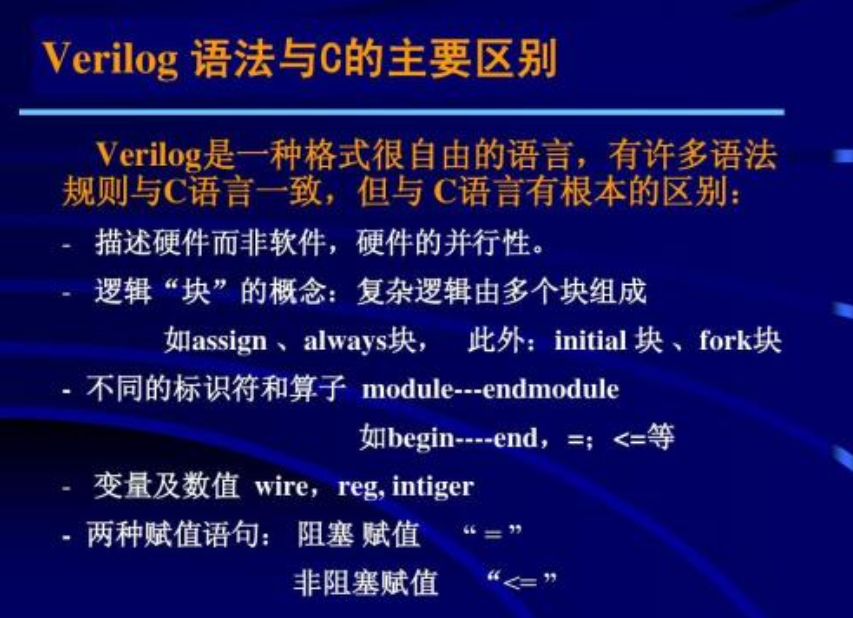

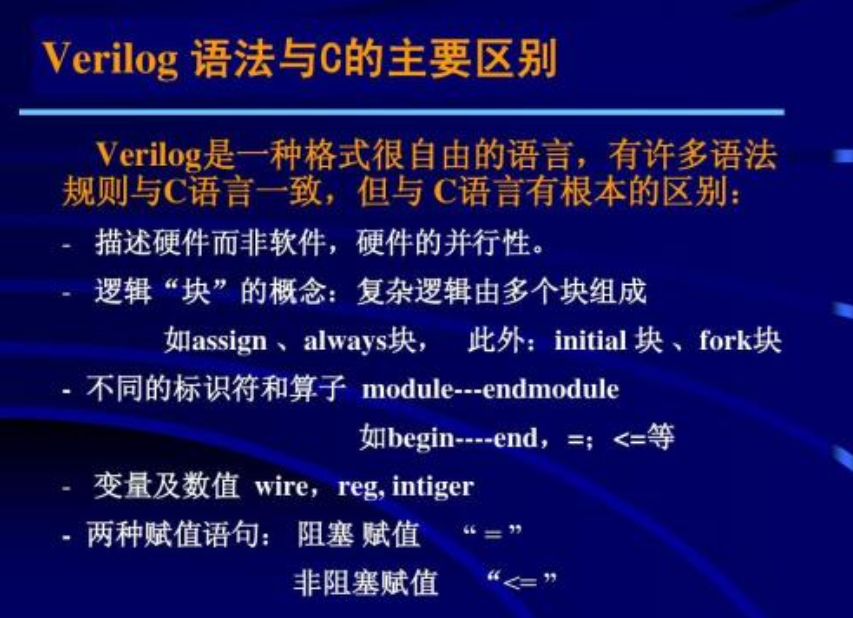

12094 Verilog HDL語言不僅定義了語法,而且對每個語法結(jié)構(gòu)都定義了清晰的模擬、仿真語義。因此,用這種語言編寫的模型能夠使用Verilog仿真器進行驗證。語言從C編程語言中繼承了多種操作符和結(jié)構(gòu)。

2019-09-27 07:09:00 1518

1518

Verilog與C語言還是存在許多差別。另外,作為一種與普通計算機編程語言不同的硬件描述語言,它還具有一些獨特的語言要素,例如向量形式的線網(wǎng)和寄存器、過程中的非阻塞賦值等。總的來說,具備C語言的設(shè)計人員將能夠很快掌握Verilog硬件描述語言。

2019-12-11 07:02:00 1446

1446

硬件描述語言基本語法和實踐

(1)VHDL 和Verilog HDL的各自特點和應(yīng)用范圍

(2)Verilog HDL基本結(jié)構(gòu)語言要素與語法規(guī)則

(3) Verilog HDL組合邏輯語句結(jié)構(gòu)

2019-07-03 17:36:00 53

53 本文檔的主要內(nèi)容詳細(xì)介紹的是有關(guān)Verilog中的一些語法詳細(xì)資料說明。

2019-07-25 17:08:33 2

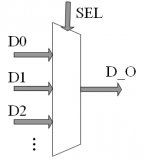

2 首先我們不開始講Verilog HDL的語法,我們從Verilog HDL的程序結(jié)構(gòu)出發(fā)。相信大家都看過芯片吧,它有個名字,有個外殼,外殼向外伸出有引腳(BGA封裝的那種請不要亂攪和。。。),然后芯片它可以實現(xiàn)一定的功能。

2020-08-27 09:18:12 2277

2277

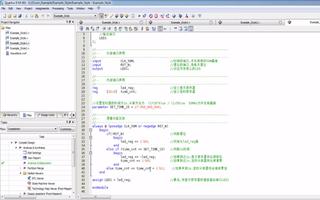

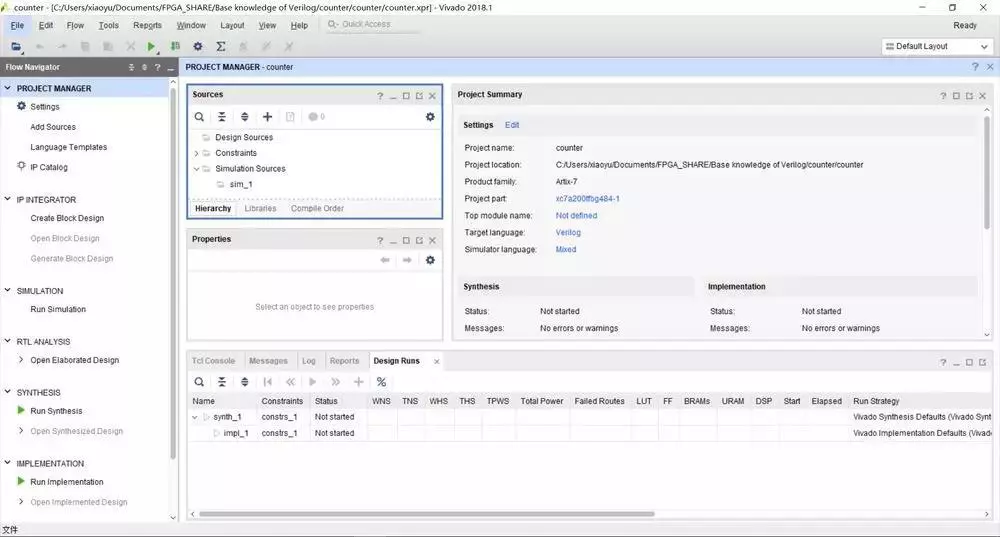

綜合,可以用這個語法來描述什么邏輯功能電路呢? 其實Xilinx已經(jīng)貼心地準(zhǔn)備好了答案,還給你準(zhǔn)備了一堆參考實例。 二. Verilog行為級描述 資料名稱“Vivado Design Suite

2021-01-02 09:45:00 1280

1280

本文檔的主要內(nèi)容詳細(xì)介紹的是FPGA的Verilog學(xué)習(xí)教程課件免費下載包括了:語法入門,語法進階,示例等等。

2021-01-21 16:30:00 14

14 Verilog黃金參考指南是一個緊湊的快速參考指南Verilog硬件描述語言,其語法,語義,綜合和應(yīng)用程序的硬件設(shè)計。

2021-02-01 15:37:00 22

22 Verilog 黃金參考指南是Verilog 硬件描述語言及其語法語義合并以及將它應(yīng)用到硬件設(shè)計的一個簡明的快速參考指南

2021-02-05 16:23:00 24

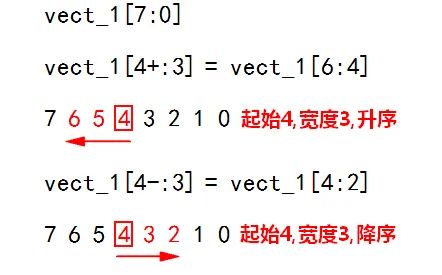

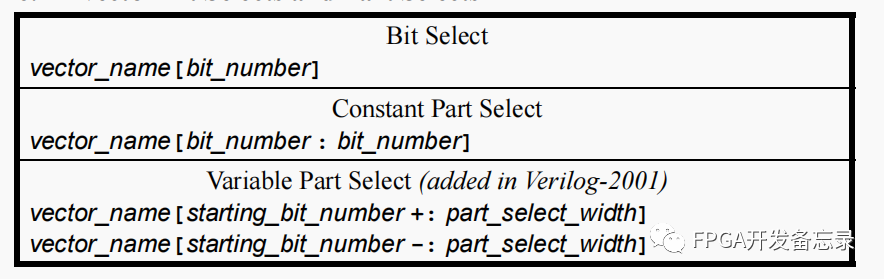

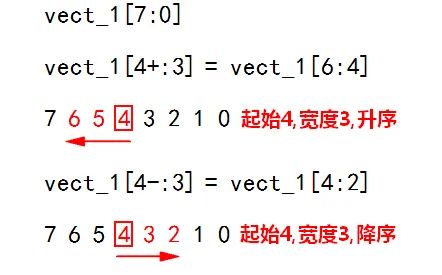

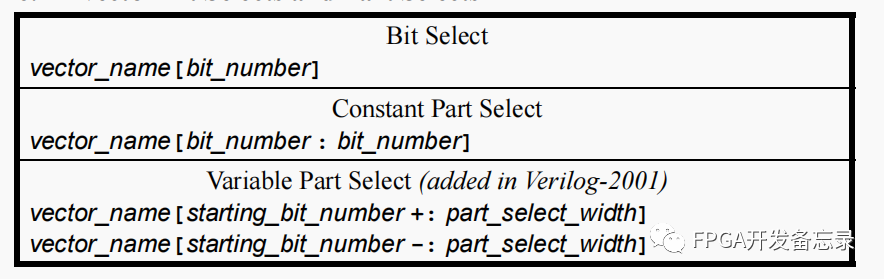

24 Verilog比較方便的一個特點就是數(shù)據(jù)的截取和拼接功能了,截取使用方括號[],拼接使用大括號{}。

2021-03-21 10:01:47 2662

2662

電子發(fā)燒友網(wǎng)為你提供+:和-:符號,Verilog標(biāo)準(zhǔn)文檔中的一個語法資料下載的電子資料下載,更有其他相關(guān)的電路圖、源代碼、課件教程、中文資料、英文資料、參考設(shè)計、用戶指南、解決方案等資料,希望可以幫助到廣大的電子工程師們。

2021-03-27 08:41:41 15

15 Verilog語法進階說明。

2021-05-06 16:14:58 29

29 簡單介紹Verilog HDL語言和仿真工具。

2021-05-06 16:17:10 617

617 Verilog入門教程,介紹Verilog的語法知識,基本程序編寫。

2021-08-13 10:56:40 2

2 Verilog HDL入門教程-Verilog HDL的基本語法

2022-01-07 09:23:42 159

159 C語言常常讓人覺得它所能表達的東西非常有限。它不具有類似第一級函數(shù)和模式匹配這樣的高級功能。但是C非常簡單,并且仍然有一些非常有用的語法技巧和功能,只是沒有多少人知道罷了。

2022-03-10 17:42:27 1774

1774 Verilog HDL是一種用于數(shù)字系統(tǒng)設(shè)計的語言。用Verilog HDL描述的電路設(shè)計就是該電路的Verilog HDL模型也稱為模塊。Verilog HDL既是一種行為描述的語言也是一種結(jié)構(gòu)描述的語言。

2022-12-08 14:00:57 1928

1928 Verilog-2005中有3個generate 語句可以用來很方便地實現(xiàn)重復(fù)賦值和例化(generate for)或根據(jù)條件選擇性地進行編譯(generate if和generate case)等功能。接下來就一起看下這3個語句的應(yīng)用場景和應(yīng)用方法吧。

2022-12-28 15:21:43 1854

1854 )和連線(wire)息息相關(guān)。Verilog便具有將ASM圖表和電路框圖用計算機語言表達的能力,本文將講述Vivado綜合支持的Verilog硬件描述語言; Verilog提供了行為化和結(jié)構(gòu)化兩方面的語言結(jié)構(gòu),描述設(shè)計對象時可以選擇高層次或低層次的抽象等級。使用V

2022-12-29 10:30:09 3387

3387 最近在看verilog代碼時發(fā)現(xiàn)如下寫法a[x*2+:4]這樣的寫法,后來花了一點時間了解到,該寫法稱為向量的部分選擇,還語法在verilog-2001 LRM就有說明,只是在語法書中鮮少提及。

2023-04-25 16:03:42 1612

1612

描述的語言。這也就是說,無論描述電路功能行為的模塊或描述元器件或較大部件互連的模塊都可以用Verilog語言來建立電路模型。如果按照一定的規(guī)矩編寫,功能行為模塊可以通過工具自動地轉(zhuǎn)換為門級互連模塊。Verilog模型可以是實際電路的不同級別的抽象。這些抽象的級別和它們對應(yīng)的模型類型共有以下五種

2023-05-22 15:52:42 557

557

描述的語言。這也就是說,無論描述電路功能行為的模塊或描述元器件或較大部件互連的模塊都可以用Verilog語言來建立電路模型。如果按照一定的規(guī)矩編寫,功能行為模塊可以通過工具自動地轉(zhuǎn)換為門級互連模塊。Verilog模型可以是實際電路的不同級別的抽象。這些抽象的級別和它們對應(yīng)的模型類型共有以下五種

2023-05-22 15:53:23 531

531

要想深入理解Verilog就必須正視Verilog語言同時具備硬件特性和軟件特性。在當(dāng)下的教學(xué)過程中,教師和教材都過于強調(diào)Verilog語言的硬件特性和可綜合特性。將Verilog語言的行為級語法

2023-05-25 15:10:21 642

642

要想深入理解Verilog就必須正視Verilog語言同時具備硬件特性和軟件特性。在當(dāng)下的教學(xué)過程中,教師和教材都過于強調(diào)Verilog語言的硬件特性和可綜合特性。將Verilog語言的行為級語法

2023-05-25 15:10:44 576

576

Verilog 是一種用于數(shù)字邏輯電路設(shè)計的硬件描述語言,可以用來進行數(shù)字電路的仿真驗證、時序分析、邏輯綜合。

2023-06-10 10:04:44 786

786

在創(chuàng)建一個linux系統(tǒng)的時候,安裝完gvim,系統(tǒng)默認(rèn)的gvim的模式是白色背景,黑色字體,無語法亮亮。打開一個python腳本大概是下面這種效果。

2023-07-26 17:37:58 646

646

verilog極簡語法手冊

2023-10-23 09:28:46 0

0

電子發(fā)燒友App

電子發(fā)燒友App

評論