專用交換機過于強大專業的功能,以及昂貴的價格,并非小型建網的理想選擇;同時,傳統的PBX的模擬交換方式存在著失真大、欠靈活以及隨規模增大而復雜度劇增的不足。本文提出的方案,有別于常用PBX的模擬交換,是一種適用于一定規模局域網的數字交換機。FPGA的使用在保證了性能提高的同時,在復雜度和擴展性方面也有了明顯的改進。

一 、系統結構

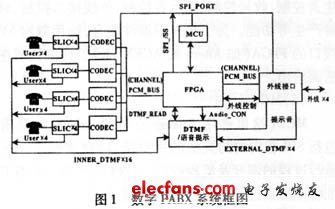

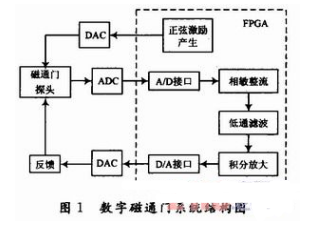

本系統實現了帶有16路內線電話、同時具備4路外線接口的數字交換機,系統結構如圖1。

?

(1)用戶接口及PCM編碼部分

用戶接口電路選用IDT公司的821611芯片,該芯片與編碼芯片IDT821034配合良好。用戶線各對應一片821611,四路用戶接入一片821034(可調增益的四路PCM編碼芯片),最終4片821034的PCM信號(16路)一起掛接在PCM總線上,送入FPGA。要注意的是, 821034采用的類似SPI (Serial Peripheral InteRFace)的串行控制接口,使我們能采用帶SPI的單片機(例如,Analog公司的Aduc812),很方便地實現對多片IDT821034的控制。

(2)外線接口

?

外線接口一部分負責外線的鈴流檢測和變壓器(僅通過語音)接入。鈴流檢測采用了SGS公司的LS1240。每當鈴流進入,向FPGA送出高電平,從而測知外線的呼入。另一部分為與內線中的SLIC和CODEC類似的語音編解碼部分,負責將交換后的數字信號轉為語音送到外線(或者將外線語音及DTMF編碼后送入FPGA)。

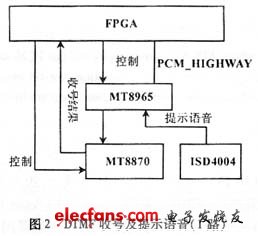

(3) DTMF接收及提示語音產生

系統中,20路電話(含4路外線)復用4路DTMF收號芯片進行收號。FPGA將待收號話路的PCM信號送到當前空閑的收號模塊。DTMF的接收由MT8870完成, FPGA與MT8870之間,有一片MT8965(單通道語音編解碼芯片),將FPGA送出數字信號轉為模擬信號由MT8870讀取。而交換過程的提示語音則選用ISD4004(語音錄放芯片,SPI控制),將其語音輸出接在MT8965的語音輸入端,再以PCM的編碼形式送入FPGA。每路DTMF接收和語音送出均為固定時隙,交換控制在FPGA中完成。

(4) FPGA

FPGA作為核心部分,負責數字交換、信號音產生及控制、收號控制、提示音控制、外線接口控制、時鐘產生等功能。為了與外圍器件配合,選用兼容5V接口的FPGA(如Altera的ACEX 1K)。詳細說明在后面給出。

(5)MCU

MCU(這里選用Analog公司的Aduc812,具有包括SPI在內的的靈活的用戶接口)負責整個系統運行過程的調度及流程控制。軟件設計的一些細節也將在后面進行說明。

?

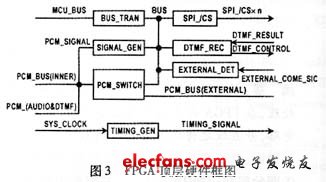

二、FPGA邏輯設計

系統內的PCM信號(用戶語音、外線語音、提示語音3種語音的PCM編碼信號)需要處理和交換;電話所需的信號音(撥號、提示、忙等)需要產生;MCU雖然負責整個系統的配置控制,但它與器件之間還需要控制邏輯;同時,系統還需要特定的時鐘和定時信號。上述的這些功能,都由FPGA來完成。圖3是FPGA的頂層硬件框圖。

?

MCU對各功能塊的相關操作均通過以總線讀寫寄存器的方式進行。

(1)總線控制(BUS-TRAN)

本功能塊將MCU的總線(高8位地址線和低8位數據地址復用線)轉換為分開的地址與數據總線(以BUS表示)。

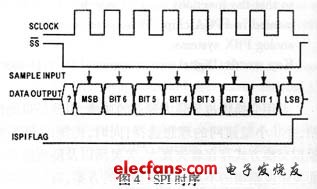

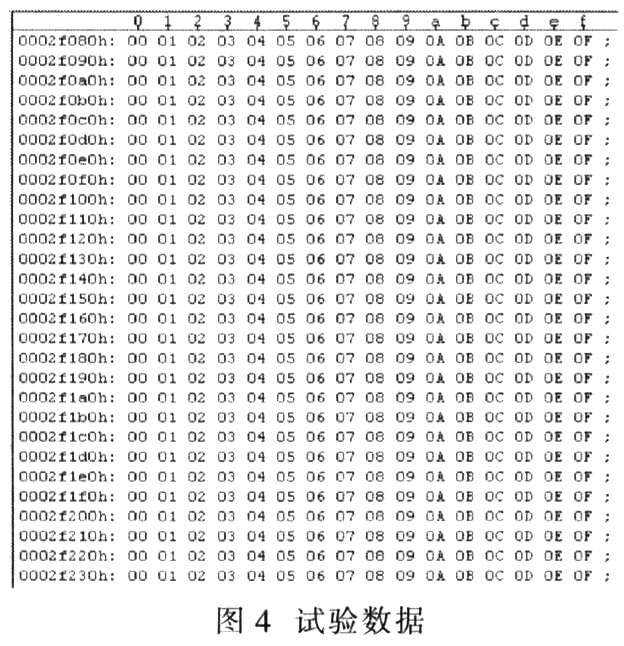

(2) SPI片選生成(SPI-/CS)

圖4中除/SS之外的信號均由MCU產生,只有/SS信號需要FPGA提供。通過對功能塊內寄存器的寫操作,生成外圍器件的SPI-/SS信號。

?

(3) DTMF收號(DTMF-REC)

FPGA與8870有DATA0-DATA3(數據)、StD(狀態線)、TOE(片選有效)等6線相連,FPGA在MCU控制下查詢StD狀態,有正脈沖時,通過TOE使8870輸出有效,再由DATA0-DATA3讀取收號結果。同時, 還要產生MT8965的控制線( CA,/F1i, CSTI)以配合收號和送提示音過程。

(4)外線檢測(EXTERNAL-DET)

這里只需要對外線接口送來的狀態線進行查詢(讀寄存器方式),以測知是否有外線呼入。

(5)時鐘產生(TIMING-GEN)

將系統時鐘分頻,得到PCM-FS、 PCM-Clock 、MCLK(For 821034)、OSC(For 8870)、C2i(For 8965)等時鐘信號。

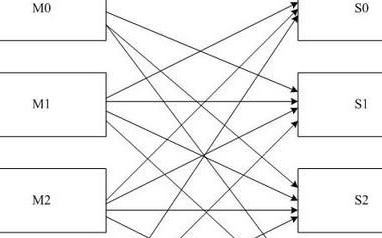

(6)數字交換(PCM-SWITCH)

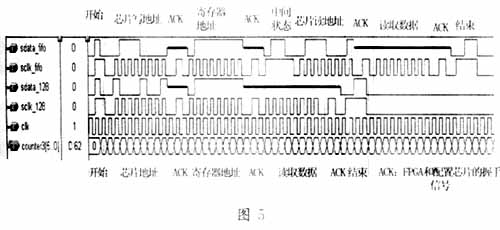

這是邏輯設計中的核心部分,其框圖如圖5所示。

?

圖5中INNER指內線用戶,EXTERNAL指外線用戶,DTMF指收號模塊,AUDIO指提示語音模塊。同時,RAM-D用來存放PCM數據,RAM-ADD用來存放控制RAM-D讀出的地址。

各路PCM信號在用來標識時隙的SLOT-CLOCK上升沿順序寫入對應的RAM-D內,RAM的大小均為32×2 byte(可容兩幀),確保送上一幀數據時,不影響當前幀寫入。RAM-ADD為32 byte的RAM,存放著對應通路的交換信息,例如,RAM-ADD(IN-IN)中的0地址處存放的是內線交換時希望0時隙內線用戶收到的時隙的標號,這些信息由MCU總線寫入。同時,在SLOT-CLOCK上升沿,FPGA將RAM-ADD順序讀出的輸出作為地址來讀取RAM-D,從而實現了交換功能。基于這樣的原理,系統實現了內線、外線、DTMF收號、提示語音這幾塊之間的靈活交換(DTMF和提示語音為單向信號,實際在同一PCM總線上)。

(7) 信號音產生(SIGNAL-GEN)

信號音頻率均為450 Hz,僅以通斷時間來區分。我們在FPGA中建立了一張450 Hz、8k采樣的正弦表(PCM編碼后),工作時循環讀出并進行并串轉換。利用定時器和三態門對其進行處理,從而形成了通斷時間不同的各種信號音。將各種信號音通過三態門掛接在用?

戶的PCM總線上,需要時只要打開對應的三態門,就可以將正確的信號音送到當前的時隙上。

三、工作流程及軟件設計

FPGA為MCU提供了與其他器件間的接口,使其能夠以簡短的指令實現原本復雜的底層操作。限于篇幅,這里只作簡要的介紹。

1. 內線通話

內線摘機:如果該用戶主叫,向該時隙送撥號音(到撥號為止),同時將主叫話路送到當前有閑的DTMF模塊(如果沒有,送忙音)的時隙上,收號完成再從DTMF時隙拿掉(或超時拆線),根據收號結果,看被叫用戶狀態,忙則將忙音送主叫時隙,否則向主叫時隙送回鈴音,同時令被叫振鈴;如果該用戶被叫,則切掉該用戶振鈴,同時取消主叫時隙的回鈴音,將這兩個時隙的話路交換,建立連接。

內線掛機:如果通話在連接狀態,則取消通話連接,送對端時隙忙音;如果無通話連接,則取消對方振鈴(如果存在的話),并拿掉本時隙上的所有信號。

2. 外線通話

外線呼入:當測知有外線呼入時,如果沒有空閑收號模塊,則等待直到出現空閑為止;否則,將呼入外線的編碼信號送至DTMF模塊的時隙,同時將提示撥分機號的提示語音編碼信號送至呼入外線的時隙,等待撥號完成(或超時拆線)。后面的過程與內線通話類似,唯一不同的是向外線送忙音只需拿掉送至呼入外線時隙的所有信號即可,而送給外線的回鈴音是由提示語音來替代的。

呼叫外線:在內線摘機后的收號過程中,當用戶撥號第一位為某特定數字(例如“0”),認為是呼叫外線,將該話路由收號時隙拿掉,并尋找一路空閑外線(若無則送忙音),將話路時隙與外線時隙進行交換,建立通話,后續過程與內線通話相似,但僅需處理內線端即可。

需要注意的是, 821034的串行控制接口與標準的SPI略有不同,在/SS有效前需要1個SCLK,拉高后需要2個SCLK,所以編程中在寫SPI的前后,各進行了一次偽寫(即在未拉低/SS的情況下,寫SPI)操作,以確保操作的正確。

四、結語

系統中,除語音至PCM編碼段外,其余話路部分實現了完全數字化,可以顯著提高內線通話質量(特別是內部網具一定規模的情況下)。同時,將原本IC實現的功能集成在單一的FPGA中實現,減小了系統復雜度,降低了成本,增加了系統的穩定性,并且這使系統的升級相較于傳統的PBX變得更為方便靈活,用戶可以根據要求在不改動硬件的情況下以編程方式實現較自由的功能擴展。特別地,隨著規模的增大,本方案的上述優勢會愈發明顯。

電子發燒友App

電子發燒友App

評論