?

以太網接口通信速度快,傳輸可靠,使用和配置方便,對于20 Mb/s以下的碼速率,100 Mb/s的網卡可以進行不丟包轉發,采用TCP包格式還可使設備小型化,便于數據的轉發,因此有必要擴展設備的以太網功能。

1 整體模塊設計

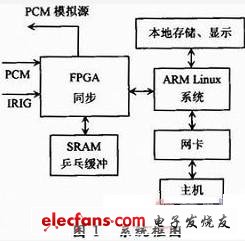

1.1 系統設計

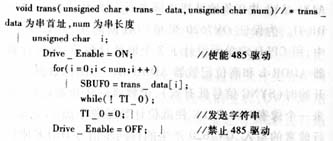

系統設計框圖如圖1所示。其中,采編器或接收機解調輸出的PCM信號及時鐘輸入到FPGA中進行幀同步,IRIG—B碼信息也送到FPGA中進行解調,得到時間信息。數據與時間一起存入SRAM乒乓緩沖區中,達到一定大小后,FPGA向ARM處理器發器中斷,ARM中運行的Linux系統,將數據取走,進行TCP/IP打包,發送給接收計算機。

?

在設備開始工作前,需要在計算機端進行參數設置,計算機TCP/IP包將參數發送給ARM處理器,由ARM處理器轉發給FPGA。幀同步器的設計中,碼速率為100b/s~10Mb/s,幀長為4~4 096Word,幀同步碼組為4~32,ARM網卡為100Mb/s。

1.2 硬件實現

PCB采用6層結構,相鄰布線層,水平垂直交叉,電路層與電源層單獨分開,提供良好的電磁兼容特性。

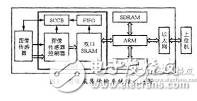

1.2.1 FPGA

FPGA選擇EP1C12,為實現乒乓緩沖結構,采用SRAM為IS61LV25616。輸入信號使用SMA線纜連接,在傳輸過程中會引入衰減,信號輸入輸出易出現阻抗不匹配的情況,選用AD8556構成射隨器,對輸入信號進行匹配,同時也增大模擬源的輸出能力。

1.2.2 ARM

在此采用S3C2440,內核為ARM920T,最高頻率為400 MHz,帶MMU支持操作系統。內存采用2×32 MB的SDRAM,存儲采用128 MB NAND FLASH,網卡采用DM9000A。

1.2.3 ARM與FPGA的接口連接

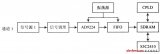

這里采用總線接口,將FPGA作為一個存儲設備掛在ARM的存儲器總線上,如圖2所示。

?

FPGA在ARM中起始地址為0x18000000,以4 B對齊,占用0x80個地址,地址范圍為0x18000000~Ox1800007C,中斷為EINT0。

在FPGA內部采用讀/寫指針來模擬FIFO,用一個地址來讀取FPGA數據,其余地址用于配置幀同步器與模擬源的參數。

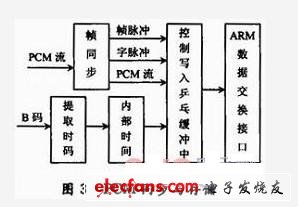

2 幀同步與B碼解調

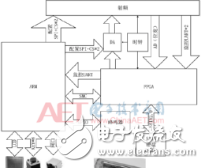

FPGA完成PCM數據的幀同步和解調B碼,寫入到乒乓SRAM緩沖區中,實現如圖3所示。

?

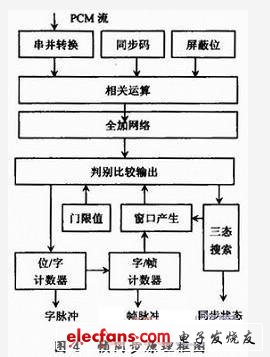

2.1 幀同步模塊

幀同步器根據幀同步碼組的相關性和周期性,經過相關運算將同步碼從PCM串行流中識別出來,原理框圖如圖4所示。

?

PCM數據按時鐘進行串/并轉換,與本地幀同步碼進行同或運算后再與上屏蔽位,由全加網絡將相關運算結果按位相加統計結果中1的個數,大于門限值則表示可能接收到了幀同步碼。

為避免虛警和漏檢,使幀同步器穩定可靠工作,采用搜索、校核、鎖定三態邏輯。

系統開始時處于搜索態,符合相關器輸出,由搜索態轉入校核態。在預期檢測窗口內沒有幀碼,從校核返回到搜索態。連續通過校核數α,進入鎖定態。為避免幀同步碼的漏檢,連續漏檢超過保護幀數β,幀同步才返回搜索態,否則保持在鎖定態,幀脈沖由本地產生。

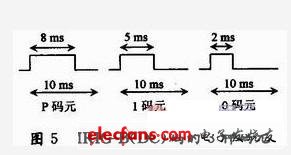

2.2 IRIG—B碼解調

IRIG時間序列碼是一種串行碼,共有3種碼元,如圖5所示。

?

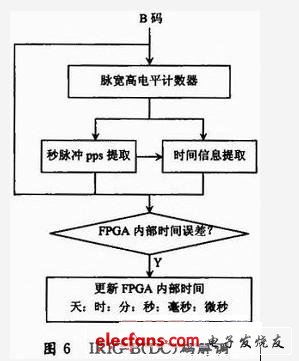

P碼元是位置碼元,連續2個P碼為一幀的開始,第1個P碼元定義為P0,第2個P碼元為秒脈沖pps,上升沿為該秒的準時刻,時間信息以BCD碼依次分布在其后的碼元中。解調時先進行pps的提取,再進行秒、分、時、天的信息提取,其流程如圖6所示。

?

時鐘頻率為1 MHz,用計數器對輸入信號的脈寬進行計數。8 ms,5 ms,2 ms脈寬計數為8 000,5 000,2 000。輸入B碼的脈寬會混有干擾,晶振時鐘也存在一定的誤差,計數器的計時判別應浮動一個范圍,設置門限為脈寬的85%~115%,當滿足一定范圍的數值時,分別輸出P碼,0碼,1碼信號。

FPGA中的時碼產生“天:時:分:秒:毫秒:微秒”信息。解調出B碼時,FPGA更新內部時間,B碼中不含毫秒與微秒信息,由FPGA根據秒脈沖信息的準時刻來生成。

3 FPGA驅動程序開發

在Linux中,所有的硬件設備都像常規文件一樣進行打開、關閉和讀/寫。把FPGA當作字符設備進行設計,驅動由設備加載與卸載,以及文件操作file_operation結構體中成員函數組成。

3.1 加載與卸栽設備驅動

FPGA設備驅動程序初始化流程為動態獲得主設備號、字符設備注冊和申請中斷;卸載流程為注銷設備,釋放設備編號。

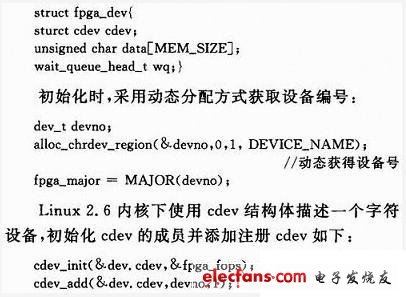

定義一個設備結構體來表示FPGA,如下:

?

當用戶程序讀FPGA設備時,數據還未準備好,此時驅動程序應該阻塞該進程,將其置入睡眠狀態直到條件滿足。此時需要初始化一個等待隊列頭,對讀進程的休眠和喚醒時使用:

?

在卸載函數中,刪除一個cdev,完成字符設備的注銷,然后釋放設備編號:

?

3.2 文件接口操作

Linux為所有的設備文件都提供了統一的操作函數,FPGA設備驅動。file_operations包含打開函fpga_open、讀函數fpga_read、設置參數函數fpga_ioctl和關閉設備函數fpga_release。

3.2.1 打開與關閉FPGA設備

在打開設備與關閉設備時會調用open函數與release函數,在open函數中,要對設備進行I/O內存資源映射及中斷申請。

設備驅動程序中,需通過內存管理單元MMU將設備的虛擬地址映射到物理地址。根據FPGA在S3C2440中的物理地址,定義如下宏:

?

使用ioremap()對FPGA的I/O內存資源進行映射,把物理內存地址映射為一個內核指針:

?

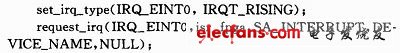

數據交換采用中斷,需先設置硬件中斷方式,然后向系統注冊中斷函數,實現如下:

?

FPGA連接在ARM的EINT0上,isr_fpga為中斷處理函數指針。當關閉FPGA設備時,需釋放I/O內存,釋放中斷:

3.2.2 驅動程序控制接口Ioctl

Ioctl用來設置FPGA中幀同步器和模擬源的參數,部分設置命令如表1所示。

?

在此,采用統一的命令碼方式,包含幻數、序數、傳輸方向、數據長度,使用宏_IO(),_IOR(),_IOW()和IOWR()輔助生成,如命令0設置如下:

?

在Ioctl中,采用switeh(cmd)來實現對FPGA參數的設置及FPGA狀態的讀取。

3.2.3 中斷函數及讀函數

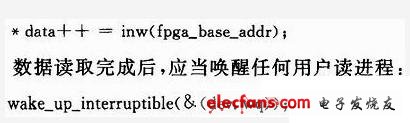

當FPGA產生中斷時,根據緩沖區的大小,中斷函數循環對FPGA映射后的地址讀取數據。ARM與FPGA接口為16位,使用inw讀取,數據存放在驅動程序的緩沖區中:

?

應用程序讀取數據時,調用read函數,參數buffer為用戶空間緩沖區的指針,利用copy_to_user函數將數據從內核空間拷貝到用戶空間,當設備中暫時沒有數據時,讀進程應當被休眠:

flag為一個標志位,當flag被中斷函數設置為1時表示設備中有數據,此時讀進程可被換醒。

3.2.4 用戶程序及測試

設備驅動實現后,需編寫相應的用戶程序來進行測試驅動程序和實現數據的網絡轉發。在用戶程序中,讀/寫FPGA設備使用與普通文件一樣的操作函數。移植Linux時配置好網卡的地址,然后使用Socket編程實現數據的TCP/IP轉發,用遙測軟件接收到的數據測試如圖7所示。

?

通過測試可以看到,同步碼FDB18450被正確識別,IRIG-B解碼為當前時間。

4 結語

在此,基于FPGA與ARM進行遙測數據的幀同步遙測數據的網絡轉發,充分地利用了FPGA與ARM各自的特點,它可使FPGA+ARM在數據接收處理中得到廣泛應用。

電子發燒友App

電子發燒友App

評論