您的位置:電子發燒友網 > 電子技術應用 > 嵌入式技術 > FPGA/ASIC技術 >

PLD設計速成(6)-編譯和布線(2)

2012年05月18日 17:08 來源:本站整理 作者:秩名 我要評論(0)

Node namepinPin type

SW244input

SW145input

L110output

L29output

在加完L2后點OK(編譯后可以看到IO在芯片上的分布:MAX plusII-> Froorplan Editor,具體見在編譯后面的講解)

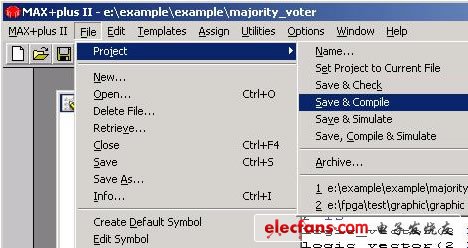

編譯文件

File->Project->save&Compile

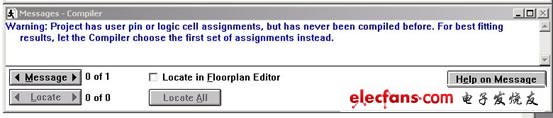

此時可能彈出下圖WARNING窗口,提示“project has user pin or logic cell assignments, but never been compiled before. For best fitting results, let the compiler choose the first set of assignments instead”,這是因為在管腳指定之前沒有compile,你只要再點save & compile就可以了

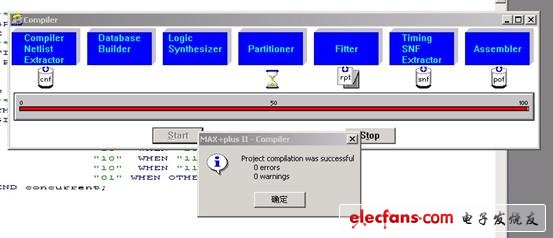

MAX PLUS II 編譯器將檢查項目是否有錯,并對項目進行邏輯綜合,然后對設計進行布局布線,放到一個Altera 器件中,同時將產生報告文件、編程文件和用于時間仿真用的輸出文件

邏輯綜合:就是把HDL語言或原理圖翻譯成最基本的與或非門的連接關系

布局布線:把這種與或非門的連接關系用芯片的內部的可編程結構和連線來實現

如果設計正確,將下圖所示,點確認

本文導航

- 第 1 頁:PLD設計速成(6)-編譯和布線(1)

- 第 2 頁:指定以下管腳

- 第 3 頁:編譯后