電子發燒友網:PLD設計,相信對很多人而言都不陌生。當然也有對它不是那么了解的人,那么即使你沒有深入接觸過PLD,我們也可以讓你可以在短短的幾十分鐘內初步學會PLD設計! 通過對本文的學習,你將迅速走進PLD世界。不信嗎? 那我們就慢慢往下看。本文主要通過分別采用VHDL、Verilog-HDL和原理圖輸入方式設計一個簡單的三人表決器,并下載到PLD實驗板進行仿真、運行。

三人表決器的主要功能介紹:三個人分別撥動開關SW1、SW2、SW3來表達自己的觀點(如果對某決議同意,各人就把自己的指撥開關撥到高電平(上方),不同意就把自己的指撥開關撥到低電平(下方))。表決結果用LED(高電平亮)顯示,如果決議通過那么實驗板上L2(黃燈)亮;如果不通過那么實驗板上L1(紅燈)亮;如果對某個決議有任意二到三人同意,那么此決議通過,L2亮;如果對某個決議只有一個人或沒人同意,那么此決議不通過,L1亮。功能雖然簡單,但是大家可以從這個實驗中學習到PLD的設計輸入,仿真,下載等一系列完整的過程。

本次設計采用的軟件:Max plusII 10.2 軟件;硬件設施:PC機一臺,JX002B型實驗板,電源,下載電纜。

軟硬件均準備好以后,就可以開始我們的設計了。下面是我們的具體實施過程:

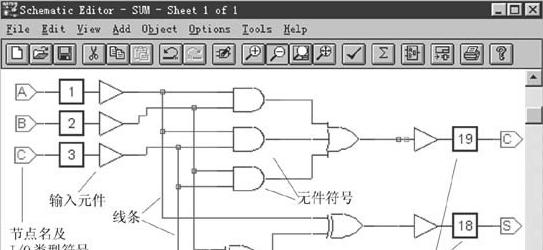

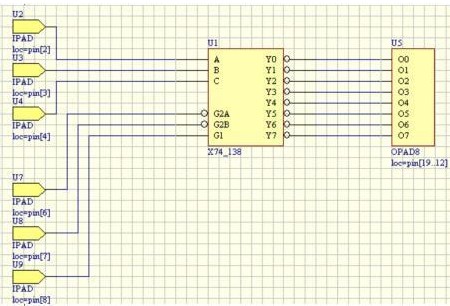

一.采用原理圖設計輸入三人表決器

我們根據三人表決器的直值表,可以通過卡諾圖化簡可以得到:

L2=SW1SW2 SW1SW3 SW2SW3

L1=_L2

那么我們可以在MAX plusII中用原理圖實現上面的三人表決器

下面僅把和VHDL不同的詳細寫下,相同或基本相同的就一帶而過:

(1)打開MAX plusII

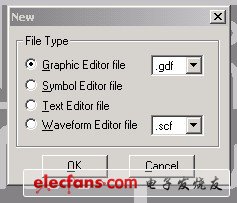

(2)新建一個圖形文件:File菜單>new

新建文件時選擇Graphic Editor file

?

點OK

(3)輸入設計文件

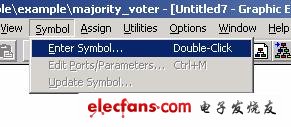

我們現在在圖形文件中輸入電路,我們這個電路需要AND2、OR3、NOT三個邏輯門電路和輸入輸出端,你可以

Symbol ->Enter Symbol(或者雙擊空白處)

?

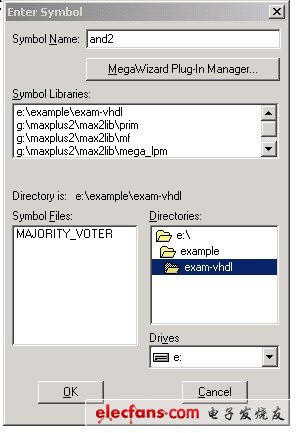

彈出窗口:

?

在Symbol Name中輸入and2,點OK

同樣可以加入or3、input、output、not

對input、output,鼠標左鍵雙擊PIN_NAME,那么PIN_NAME被選中,并且變黑,然后輸入你要改的名字,如SW1

?

【關于“采用原理圖設計輸入三人表決器”詳細部分請參考:PLD設計速成(2)-采用原理圖設計三人表決器】

二.采用VHDL設計輸入三人表決器

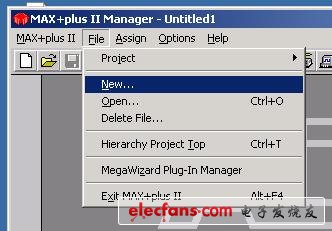

打開MAX plusII,在開始菜單內選擇MAX PLUS II 項,開始運行MAX PLUS II(如下圖)

?

你最好把圖標放到桌面上,以后直接雙擊MAX PLUS II圖標就可以運行軟件了

在MAX PLUSII上點右鍵,選擇發送到->桌面快捷方式(如下圖),那么你桌面上就看到MAX PLUS II了。

?

3.2 新建VHDL文檔

(圖形和verilog-HDL設計的過程見后面的部分)

FILE->NEW

?

【關于“采用VHDL設計輸入三人表決器”詳細部分請參考:PLD設計速成(3)-采用VHDL設計輸入三人表決器】

三.采用VerilogHDL輸入三人表決器

下面僅把和VHDL不同的詳細寫下,相同或基本相同的就一帶而過:

(1)打開MAX plusII

(2)新建

新建一個verilog-HDL文件(Text Editor File類型)

(3)輸入設計文件

其中SW12,SW13,SW23為中間變量

module majority_voter(SW1,SW2,SW3,L1,L2);

output L1,L2;

input SW1,SW2,SW3;

and(SW12,SW1,SW2);

and(SW13,SW1,SW3);

and(SW23,SW2,SW3);

or(L2,SW12,SW13,SW23);

//SW12、SW23、SW13是中間變量

not(L1,L2);

endmodule

(4)保存文件

保存為majority_voter.v,注意Automatic Extension選.v

?

并把文件設為當前工程(同前)

四.波形仿真

此過程主要是用軟件來仿真你的設計,看看結果是否符合你的設計要求

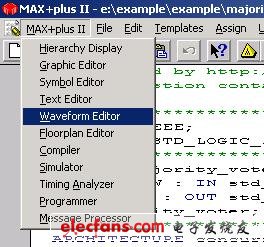

編譯好以后,打開波形編輯器,MAX PLUSII->Waveform Editor

?

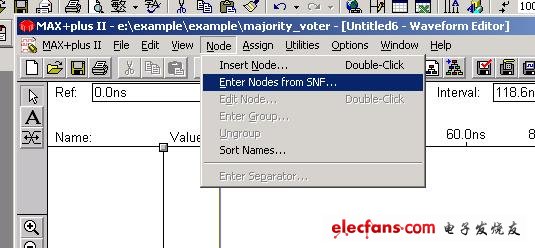

載入端口,Node->Enter Nodes from SNF

?

將彈出下面窗口,你按下面步驟操作:

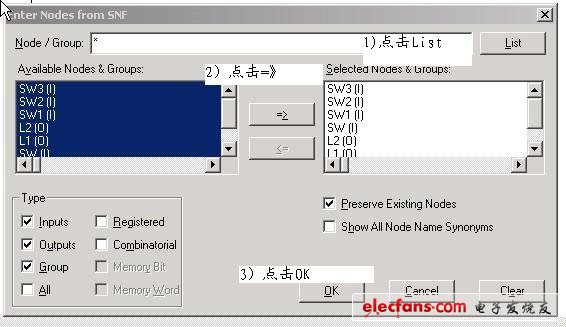

?

點List,將出現端口列表,你默認是選擇全部,你也可以通過左鍵和Ctrl組合來選擇你想要的信號。

點=>將你的信號加入SNF文件中

點OK

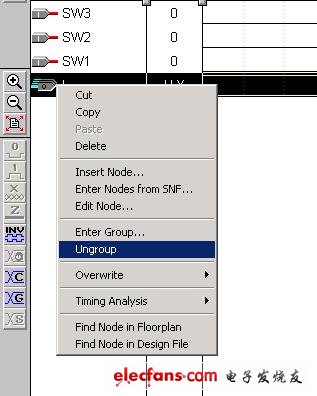

為了方便觀察,我們把信號展開

?

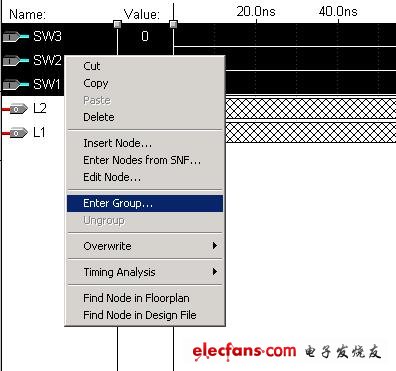

如果需要再次合并可以按住SHIFT鍵,用鼠標左鍵選上要合并的信號,再點右鍵->Enter Group

?

【關于“波形仿真”詳細部分請參考:PLD設計速成(5)-波形仿真】

五.編譯和布線

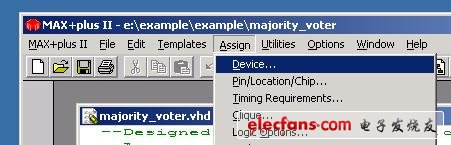

我們先要指定所用芯片的型號,

菜單:Assign->Device

如下圖

?

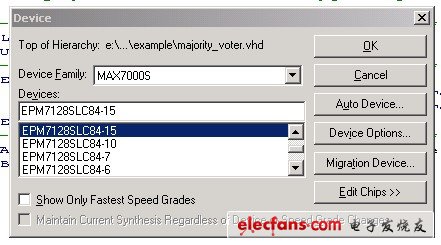

將彈出一窗口

(注意把show only fastest speed grades前的鉤去掉,否則看不到EPM7128SLC84-15)

?

在Debice Family 中選擇MAX7000S

DEVICE選擇EPM7128SLC84-15

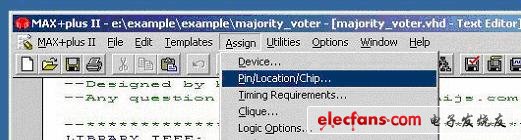

再指定芯片的管腳(也就是把你設計的IO口如L1,L2指定到芯片對應的管腳上如10,9)

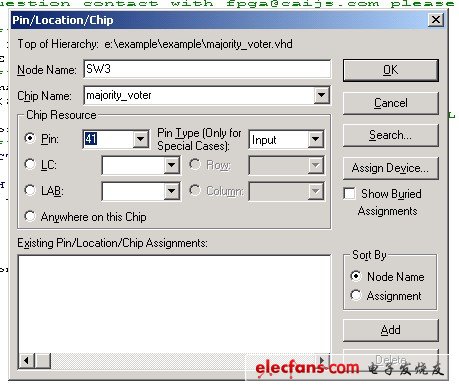

Assign->Pin/Location/Chip(也可以在空白處點右鍵,選Assign->Pin/Location/Chip)

?

將彈出下圖窗口:

?

【關于“編譯和布線”詳細部分請參考:PLD設計速成(6)-編譯和布線】

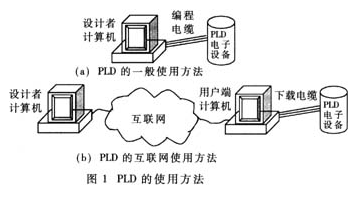

六.安裝下載電纜的驅動程序

MAX plusII 軟件的驅動設置

在Win98下運行MAX plusII可以自動檢測到ByteBlasterMV(ByteBlaster)下載電纜,但在WIN2000、WINXP下無法自動檢測到它的存在。如何在WIN2000和WINXP平臺下安裝使用ByteBlasterMV并口下載電纜呢?

WIN2000

1)在控制面板中選擇“添加/刪除硬件”

?

2)選擇“添加/排除設備故障”,下一步

?

3)選擇“添加新設備”,下一步

?

【關于“安裝下載電纜的驅動程序”詳細部分請參考:PLD設計速成(7)-安裝下載電纜的驅動程序】

七.下載驗證

( 注意:本次實驗采用的JX002B實驗板已經將下載電纜的電路都做在了實驗板上,所以只需要一根并口延長線即可,實際使用中一般都使用標準的下載電纜(ByteblasterMV、ByteblasterII)和并口相連,下載電纜再和PLD芯片相連)

在下載前,還要進行以下步驟:

A:將JX002B實驗板的電源開關撥到OFF(上方)

?

B:將并口下載電纜母端插到JX002B實驗的25針下載口上,并口電纜公端插到電腦的打印口上,參考下面四張圖(不可能插錯,否則插不上)

并口電纜母端

?

并口電纜公端

?

JX002B實驗的25針下載口

?

【關于“下載驗證”詳細部分請參考:PLD設計速成(8)-下載驗證】

??????? 關于三人表決器的整個設計、仿真及運行過程就到此結束了。想要了解更多的話,繼續關注我們電子發燒友網,更多精彩內容等著你!

電子發燒友App

電子發燒友App

評論