練習(xí)十. 通過模塊之間的調(diào)用實(shí)現(xiàn)自頂向下的設(shè)計(jì)目的:學(xué)習(xí)狀態(tài)機(jī)的嵌套使用實(shí)現(xiàn)層次化、結(jié)構(gòu)化設(shè)計(jì)。

現(xiàn)代硬件系統(tǒng)的設(shè)計(jì)過程與軟件系統(tǒng)的開發(fā)相似,設(shè)計(jì)一個(gè)大規(guī)模的集成電路的往往由模塊多層次的引用和組合構(gòu)成。層次化、結(jié)構(gòu)化的設(shè)計(jì)過程,能使復(fù)雜的系統(tǒng)容易控制和調(diào)試。 在Verilog HDL中,上層模塊引用下層模塊與C語言中程序調(diào)用有些類似,被引用的子模塊在綜合時(shí)作為其父模塊的一部分被綜合,形成相應(yīng)的電路結(jié)構(gòu)。在進(jìn)行模塊實(shí)例引用時(shí),必須注意的是模塊之間對(duì)應(yīng)的端口,即子模塊的端口與父模塊的內(nèi)部信號(hào)必須明確無誤地一一對(duì)應(yīng),否則容易產(chǎn)生意想不到的后果。

下面給出的例子是設(shè)計(jì)中遇到的一個(gè)實(shí)例,其功能是將并行數(shù)據(jù)轉(zhuǎn)化為串行數(shù)據(jù)送交外部電路編碼,并將解碼后得到的串行數(shù)據(jù)轉(zhuǎn)化為并行數(shù)據(jù)交由CPU處理。顯而易見,這實(shí)際上是兩個(gè)獨(dú)立的邏輯功能,分別設(shè)計(jì)為獨(dú)立的模塊,然后再合并為一個(gè)模塊顯得目的明確、層次清晰。

// ----------------?? p_to_s.v ---------------------------------

module? p_to_s(D_in,T0,data,SEND,ESC,ADD_100);

??? output??????? D_in,T0;??????????? // D_in是串行輸出,T0是移位時(shí)鐘并給

????????????????????????????????????? // CPU中斷,以確定何時(shí)給出下個(gè)數(shù)據(jù)。

??? input?? [7:0] data;?????????????? //并行輸入的數(shù)據(jù)。

??? input???????? SEND,ESC,ADD_100;?? //SEND、ESC共同決定是否進(jìn)行并到串

????????????????????????????????????? //的數(shù)據(jù)轉(zhuǎn)化。ADD_100決定何時(shí)置數(shù)。

??? wire????????? D_in,T0;

??? reg [7:0] DATA_Q,DATA_Q_buf;

?

??? assign??????? T0 = ! (SEND & ESC);????? //形成移位時(shí)鐘。.

??? assign??????? D_in = DATA_Q[7];???????? //給出串行數(shù)據(jù)。

?

??? always @(posedge T0 or negedge ADD_100)? //ADD_100下沿置數(shù),T0上沿移位。

????? begin

??????? if(!ADD_100)

????????? DATA_Q = data;

??????? else

????????? begin

????????? DATA_Q_buf = DATA_Q<<1;??????? //DATA_Q_buf作為中介,以令綜合器

????????? DATA_Q??? = DATA_Q_buf;?????????? //能辨明。

????????? end

????? end

endmodule

在p_to_s.v中,由于移位運(yùn)算雖然可綜合,但是不是簡單的RTL級(jí)描述,直接用DATA_Q<=DATA_Q<<1的寫法在綜合時(shí)會(huì)令綜合器產(chǎn)生誤解。另外,在該設(shè)計(jì)中,由于時(shí)鐘T0的頻率較低,所以沒有象以往那樣采用低電平置數(shù),而是采用ADD_100的下降沿置數(shù)。

//--------------------- s_to_p.v ---------------------------

module s_to_p(T1, data, D_out,DSC,TAKE,ADD_101);

?????? output?????? T1;???????????????????? //給CPU中斷,以確定CPU何時(shí)取轉(zhuǎn)化

??????????????????????????????????????????? //得到的并行數(shù)據(jù)。?????????????

?????? output [7:0] data;????????????????

?????? input?? D_out, DSC, TAKE, ADD_101;? //D_out提供輸入串行數(shù)據(jù)。DSC、TAKE

?????????????????????????????????????????? //共同決定何時(shí)取數(shù)。??????????

?????? wire?? [7:0] data;

?????? wire???????? T1,clk2;

?????? reg??? [7:0] data_latch, data_latch_buf;

??????

?????? assign?????? clk2 = DSC? & TAKE ;?? //提供移位時(shí)鐘。??????

?????? assign?????? T1 = !clk2;

??????

?????? assign?????? data =? (!ADD_101) ? data_latch : 8'bz;???

?????? always@(posedge clk2)

??????????? begin

?????????????? data_latch_buf = data_latch << 1;?? //data_latch_buf作緩沖

?????????????? data_latch???? = data_latch_buf;?? //,以令綜合器能辯明。

??????????????? data_latch[0] = D_out;

?????????? end

endmodule

將上面的兩個(gè)模塊合并起來的sys.v的源代碼:

//------------------- sys.v ---------------------------

`include "./p_to_s.v"

`include "./s_to_p.v"

module sys(D_in,T0,T1, data, D_out,SEND,ESC,DSC,TAKE,ADD_100,ADD_101);

? input???????? D_out,SEND,ESC,DSC,TAKE,ADD_100,ADD_101;

? inout? [7:0]? data;

? output??????? D_in,T0,T1;

?

? p_to_s?? p_to_s(.D_in(D_in),.T0(T0),.data(data),

??????????????? .SEND(SEND),.ESC(ESC),.ADD_100(ADD_100));

? s_to_p?? s_to_p(.T1(T1),.data(data),.D_out(D_out),

????????? .DSC(DSC),.TAKE(TAKE),.ADD_101(ADD_101));

?

endmodule

測(cè)試模塊源代碼:

//-------------Top test file for sys.v ------------------

`timescale 1ns/100ps

`include "./sys.v"

module Top;

?reg D_out,SEND,ESC,DSC,TAKE,ADD_100,ADD_101;

?reg[7:0] data_buf;

?wire [7:0] data;

?wire clk2;

?assign? data = (ADD_101) ? data_buf : 8'bz;??

???????????????????????????????? //data在sys中是inout型變量,ADD_101

???????????????????????????????? //控制data是作為輸入還是進(jìn)行輸出。

assign? clk2 =DSC && TAKE;

initial?

? begin

???? SEND = 0;

???? ESC = 0;

???? DSC = 1;

???? TAKE = 1;

???? ADD_100 = 1;

???? ADD_101 = 1;

? end

initial

? begin

??? data_buf = 8'b10000001;

??? #90 ADD_100 = 0;

??? #100 ADD_100 = 1;

? end

always

? begin

??? #50;

??? SEND = ~SEND;

??? ESC = ~ESC;

? end

initial

? begin

??? #1500 ;

??? SEND = 0;

??? ESC? = 0;

??? DSC? = 1;

??? TAKE = 1;

??? ADD_100 = 1;

??? ADD_101 = 1;

??? D_out = 0;???

??? #1150 ADD_101 = 0;

??? #100 ADD_101 =1;

??? #100 $stop;

? end

always

? begin

??? #50 ;

??? DSC = ~DSC;

??? TAKE = ~TAKE;

? end

always @(negedge clk2) D_out = ~D_out;

sys??? sys(.D_in(D_in),.T0(T0),.T1(T1),.data(data),.D_out(D_out),

????????????? .ADD_101(ADD_101), .SEND(SEND),.ESC(ESC),.DSC(DSC),

?????????????????????????????????? .TAKE(TAKE),.ADD_100(ADD_100));?

endmodule

仿真波形:[[wysiwyg_imageupload:255:]]

練習(xí):設(shè)計(jì)一個(gè)序列發(fā)生器。要求根據(jù)輸入的8位并行數(shù)據(jù)輸出串行數(shù)據(jù),如果輸入數(shù)據(jù)在0—127之間則輸出一位0,如果輸入數(shù)據(jù)在128—255之間則輸出一位1,同步時(shí)鐘觸發(fā);并且和范例8的序列檢測(cè)器搭接,形成一個(gè)封閉系統(tǒng)。編寫測(cè)試模塊,并給出仿真波形。

通過模塊之間的調(diào)用實(shí)現(xiàn)自頂向下的設(shè)計(jì)

- 模塊(46367)

- 狀態(tài)機(jī)(27117)

相關(guān)推薦

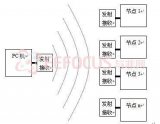

通過無線通信收發(fā)模塊實(shí)現(xiàn)單片機(jī)之間通信的解決方案

與有線數(shù)據(jù)傳輸相比,無線數(shù)據(jù)傳輸以成本低廉、適應(yīng)性好、擴(kuò)展性好、組網(wǎng)簡單方便、設(shè)備維護(hù)簡單等特點(diǎn)在工業(yè)生產(chǎn)、抄表系統(tǒng)、離散環(huán)境下的監(jiān)控系統(tǒng)、點(diǎn)菜系統(tǒng)等眾多領(lǐng)域得到廣泛的運(yùn)用。下面通過無線通信收發(fā)模塊D21DL來實(shí)現(xiàn)兩個(gè)單片機(jī)之間的通信。

2018-02-28 09:01:04 8762

8762

8762

8762

匯編語言模塊調(diào)用C++函數(shù)實(shí)例

現(xiàn)在編寫一個(gè)簡單的應(yīng)用程序,提示用戶輸入整數(shù),通過移位的方式將其與 2 的幕 (21?2?) 相乘,并用填充前導(dǎo)空格的形式再次顯示每個(gè)乘積。輸入-輸出使用 C++。匯編模塊將調(diào)用 3 個(gè) C++ 編寫的函數(shù)。程序?qū)⒂?C++ 模塊啟動(dòng)。

2022-10-11 09:52:20 672

672

672

672CanTrcv_SetOpMode被哪個(gè)模塊調(diào)用?在什么場(chǎng)景下調(diào)用?

CanTrcv模塊在上電后的初始狀態(tài)配置,一般配置初始狀態(tài)為SLEEP狀態(tài)。而后,CanTrcv模塊的狀態(tài)通過其他模塊調(diào)用CanTrcv_SetOpMode來切換。

2022-10-31 10:58:09 1693

1693

1693

1693Linux系統(tǒng)調(diào)用的實(shí)現(xiàn)與應(yīng)用

在計(jì)算機(jī)科學(xué)中,系統(tǒng)調(diào)用(System Call)是一種操作系統(tǒng)提供的服務(wù),它允許應(yīng)用程序通過軟件中斷的方式訪問操作系統(tǒng)內(nèi)核中的函數(shù)。這些函數(shù)提供了一系列與硬件相關(guān)的服務(wù),例如文件系統(tǒng)訪問、進(jìn)程管理、網(wǎng)絡(luò)通信等。應(yīng)用程序通過系統(tǒng)調(diào)用接口來調(diào)用這些函數(shù),以便實(shí)現(xiàn)各種功能。

2023-06-14 11:46:37 338

338

338

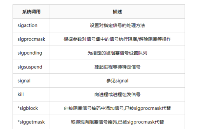

338Linux內(nèi)核中系統(tǒng)調(diào)用詳解

Linux內(nèi)核中設(shè)置了一組用于實(shí)現(xiàn)各種系統(tǒng)功能的子程序,稱為系統(tǒng)調(diào)用。用戶可以通過系統(tǒng)調(diào)用命令在自己的應(yīng)用程序中調(diào)用它們。從某種角度來看,系統(tǒng)調(diào)用和普通的函數(shù)調(diào)用非常相似。區(qū)別僅僅在于,系統(tǒng)調(diào)用由操作系統(tǒng)核心提供,運(yùn)行于核心態(tài);而普通的函數(shù)調(diào)用由函數(shù)庫或用戶自己提供,運(yùn)行于用戶態(tài)。

2023-08-23 10:37:22 577

577

577

577

通過CALL命令調(diào)用cmd腳本實(shí)現(xiàn)NVM讀取

和具體使用方法1.4 save命令詳解2. 通過CALL命令調(diào)用cmd腳本實(shí)現(xiàn)NVM讀取2.1 CMD命令腳本和CALL命令詳解2.2 讀取S12G128的片上NVM數(shù)...

2021-11-04 07:52:57

通過LabVIEW調(diào)用DLL文件,實(shí)現(xiàn)USB HID的雙向通信

通過LabVIEW調(diào)用DLL文件,實(shí)現(xiàn)USB HID的雙向通信。(說明:請(qǐng)不要向我索要LabVIEW源代碼,開發(fā)千般辛苦,況且是公司的代碼,我相信大家的水平都比我高,通過下面的入門介紹,相信大家可以

2011-11-30 11:22:57

通過LabVIEW與MATLAB設(shè)計(jì)模糊參數(shù)自整定PID

摘 要:探討在MATLAB中使用FIS編輯器與Simulink相結(jié)合的方法構(gòu)造模糊推理結(jié)構(gòu),并通過MATLAB Script Node實(shí)現(xiàn)LabVIEW與MATLAB的混合編程,設(shè)計(jì)出具有模糊自整定

2019-04-03 09:40:03

通過vi調(diào)用節(jié)點(diǎn),調(diào)用vi的問題

通過vi節(jié)點(diǎn),打開前面板,運(yùn)行vi等等。但是比如說我需要從用戶登錄界面,通過vi調(diào)用節(jié)點(diǎn),打開某個(gè)試驗(yàn)界面,同時(shí)希望是淡入淡出的效果,也就是通過設(shè)置透明度來實(shí)現(xiàn)。可是開運(yùn)行到節(jié)點(diǎn)的時(shí)候,會(huì)咔2、3

2013-08-23 21:41:58

DSP與FPGA之間的通信如何實(shí)現(xiàn)

大家好,我現(xiàn)在在畫一塊28335的板子,想實(shí)現(xiàn)與FPGA之間的通信,但是不知道該怎樣設(shè)計(jì),包括FPGA與DSP連接的引腳、通過內(nèi)部什么模塊實(shí)現(xiàn)數(shù)據(jù)通信,現(xiàn)在一頭霧水,請(qǐng)大家?guī)兔ΑVx謝。

2018-12-03 15:55:34

EDA技術(shù)有什么特征?

EDA代表了當(dāng)今電子設(shè)計(jì)技術(shù)的最新發(fā)展方向,它的基本特征是:設(shè)計(jì)人員按照“自頂向下”的設(shè)計(jì)方法,對(duì)整個(gè)系統(tǒng)進(jìn)行方案設(shè)計(jì)和功能劃分,系統(tǒng)的關(guān)鍵電路用一片或幾片專用集成電路(ASIC)實(shí)現(xiàn),然后采用硬件

2019-10-08 14:25:32

ESD設(shè)計(jì)與綜合

設(shè)計(jì)中的ESD分析。外圍和核心電路的I/O布局及其在ESD和Latchup下的應(yīng)用。在“自底向上”和“自頂向下”兩種方法下進(jìn)行保護(hù)環(huán)整合,將涵蓋I/O保護(hù)環(huán)、ESD保護(hù)環(huán)、I/O至I/O之間和I/O至

2013-09-04 09:17:26

LCD的通用驅(qū)動(dòng)電路IP核設(shè)計(jì)

本帖最后由 gk320830 于 2015-3-8 09:29 編輯

LCD的通用驅(qū)動(dòng)電路IP核設(shè)計(jì) 摘 要:本文介紹了一種新型的LCD驅(qū)動(dòng)電路IP核的總體設(shè)計(jì),采用自頂向下的設(shè)計(jì)方法將其

2012-08-12 12:28:42

Overlay的增加段代碼之間的調(diào)用關(guān)系功能

主要講其中的Overlay的增加段代碼之間的調(diào)用關(guān)系功能。keil編譯后可以在.m51文件中看到這樣的一段類似代碼:即所謂的call tree。keil編譯的時(shí)候會(huì)建立call tree,以適當(dāng)

2022-01-27 06:05:30

RTL8196C模塊/入墻式AP模塊/吸頂AP模塊/無線中繼模塊/AP模塊

`在RTL8196C的應(yīng)用設(shè)計(jì)十分豐富,我們所提及的RTL8196C模塊主要是指它作為無線網(wǎng)絡(luò)設(shè)備模塊的使用!供電方式:通過DIP排針插座;通過DC座子;通過RJ-45采用POE供電;通過焊盤直接

2013-03-29 13:40:40

labview通過調(diào)用7Z實(shí)現(xiàn)文件壓縮

7Z對(duì)大文件的壓縮率高,對(duì)于大文件存儲(chǔ)省空間。范例可實(shí)現(xiàn)labview對(duì)7Z的調(diào)用。如果調(diào)用失敗,請(qǐng)檢查電腦是否安裝了7Z。

2021-07-21 12:01:32

分享兩個(gè)組合邏輯模塊化設(shè)計(jì)實(shí)例以及仿真和上板演示過程

功能模塊同樣可以再繼續(xù)分解為多個(gè)更底層的模塊,這就是自頂向下的設(shè)計(jì)思想,也是目前主流的數(shù)字系統(tǒng)設(shè)計(jì)思想,而模塊化設(shè)計(jì)就是遵循這一設(shè)計(jì)思想的重要設(shè)計(jì)方法。事實(shí)上,無論多么復(fù)雜的系統(tǒng)總能夠逐步分解為多個(gè)

2022-07-22 15:12:19

基于自頂向下技術(shù)的工程機(jī)械Digital Prototyping設(shè)計(jì)方法及應(yīng)用

【作者】:劉雪冬【來源】:《華南理工大學(xué)》2009年【摘要】:自頂向下的設(shè)計(jì)方法及裝配建模技術(shù)是在消費(fèi)品行業(yè)應(yīng)用比較成熟的一種設(shè)計(jì)方法和理論;但是有鑒于通用機(jī)械設(shè)計(jì)的復(fù)雜性、多樣性和關(guān)聯(lián)性等特點(diǎn)

2010-04-24 09:20:57

基于自頂向下技術(shù)的工程機(jī)械Digital Prototyping設(shè)計(jì)方法及應(yīng)用

閱卷系統(tǒng);3.實(shí)施操作考試,收集考試文檔,用自行編寫的計(jì)算機(jī)自動(dòng)閱卷系統(tǒng)進(jìn)行評(píng)分并改進(jìn)這個(gè)系統(tǒng);4.通過團(tuán)體合作和積累,進(jìn)一步開發(fā)智能組卷、防作弊、學(xué)習(xí)情況分析等…【關(guān)鍵詞】:職業(yè)教育;;操作考試

2010-04-24 09:20:41

基于FPGA的直流電機(jī)調(diào)速系統(tǒng)設(shè)計(jì)資料分享

功能本設(shè)計(jì)主要分為三個(gè)主要部分:按鍵控制部分、數(shù)碼管轉(zhuǎn)速檔位顯示部分、PWM信號(hào)產(chǎn)生部分。分別采用verilog 語言完成底層模塊的設(shè)計(jì)和以原理圖的方法完成頂層模塊的設(shè)計(jì),采用自頂向下的設(shè)計(jì)方法

2022-02-17 06:57:54

大神們,我現(xiàn)在要用labview通過串口向下位機(jī)芯片燒程序

大神們,我現(xiàn)在要用labview通過串口向下位機(jī)芯片燒程序,目前我用一個(gè)燒程序的.exe可執(zhí)行文件,那我該如何實(shí)現(xiàn)呢?就是在上位機(jī)上一點(diǎn)下載程序的按鈕,程序就通過串口燒到芯片上去了?求指教

2015-11-13 15:01:49

如何實(shí)現(xiàn)擴(kuò)頻通信調(diào)制器自頂向下的設(shè)計(jì)?

如何實(shí)現(xiàn)擴(kuò)頻通信調(diào)制器自頂向下的設(shè)計(jì)?如何實(shí)現(xiàn)擴(kuò)頻通信調(diào)制器的仿真測(cè)試?

2021-04-29 06:46:04

如何通過調(diào)用mNfcTag寫入郵箱?

我們有一個(gè)問題,我們正在嘗試使用郵箱通過 NFC 上傳新的固件版本。我們的引導(dǎo)加載程序空間有限,因此我們?yōu)樗氤隽艘粋€(gè)簡單的協(xié)議;嘗試通過調(diào)用 mNfcTag 寫入郵箱

2023-01-05 06:24:02

如何利用cadenceVirtuoso實(shí)現(xiàn)一個(gè)完整的射頻芯片的設(shè)計(jì)?

本文詳細(xì)討論了基于cadenceVirtuoso設(shè)計(jì)平臺(tái)的單片射頻收發(fā)集成電路的設(shè)計(jì)過程。討論了利用VirtUOSO工具完成的自頂向下、從系統(tǒng)到模塊、從前端都后端的整個(gè)設(shè)計(jì)步驟,直到實(shí)現(xiàn)一個(gè)完整的射頻芯片。

2021-04-22 06:57:22

如何用EDA設(shè)計(jì)全數(shù)字三相昌閘管觸發(fā)器IP軟核?

本文利用先進(jìn)的EDA軟件,用VHDL硬件描述語言采用自頂向下的模塊化設(shè)計(jì)方法,完成了具有相序自適應(yīng)功能的雙脈沖數(shù)字移相觸發(fā)器的IP軟核設(shè)計(jì)。

2021-04-28 06:39:00

如何設(shè)計(jì)一種基于FPGA的AGWN信號(hào)生成器?

本文就是通過分析AGWN的性質(zhì),采用自頂向下的設(shè)計(jì)思路,將AGWN信號(hào)分成若干模塊,最終使用Verilog硬件描述語言,完成了通信系統(tǒng)中AGWN信號(hào)發(fā)生電路的設(shè)計(jì)和仿真,其實(shí)質(zhì)上是設(shè)計(jì)一個(gè)AGWN

2021-05-08 09:20:16

子vi之間實(shí)現(xiàn)如何數(shù)據(jù)同步

一個(gè)子vi調(diào)用了多次,只有一次和主vi實(shí)現(xiàn)數(shù)據(jù)傳輸,子vi之間實(shí)現(xiàn)如何數(shù)據(jù)同步?

2015-06-12 10:50:15

層次原理圖如何設(shè)計(jì)

中間的操作過程有些差異。 自頂向下的設(shè)計(jì)方法。 康龍思義,首項(xiàng)向下設(shè)計(jì)就是說先給制最上層的原理圍,然后再向下分別院光要個(gè)模塊的果理圖,此方法道用于開展一個(gè)全新的改計(jì), 從上往下一段一般光成

2019-01-17 16:55:16

嵌入式C語言程序設(shè)計(jì)基礎(chǔ)大匯總

是運(yùn)行速度快、編譯效率高、移植性好和可讀性強(qiáng)。C語言具有簡單的語法結(jié)構(gòu)和強(qiáng)大的處理功能,并可方便地實(shí)現(xiàn)對(duì)系統(tǒng)硬件的直接操作。C語言支持模塊化程序設(shè)計(jì)結(jié)構(gòu),支持自頂向下的結(jié)構(gòu)化程序設(shè)...

2021-11-09 07:13:02

怎么使用VHDL語言設(shè)計(jì)一個(gè)高效的微控制器內(nèi)核?

通過對(duì)傳統(tǒng)MCS-51單片機(jī)指令時(shí)序和體系結(jié)構(gòu)的分析,使用VHDL語言采用自頂向下的設(shè)計(jì)方法重新設(shè)計(jì)了一個(gè)高效的微控制器內(nèi)核。

2021-04-13 06:10:59

求一種基于FPGA的提取位同步時(shí)鐘DPLL設(shè)計(jì)

本文主要研究了一種基于FPGA、自頂向下、模塊化、用于提取位同步時(shí)鐘的全數(shù)字鎖相環(huán)設(shè)計(jì)方法。

2021-05-06 08:00:46

現(xiàn)代數(shù)字系統(tǒng)的設(shè)計(jì)方法有哪些

。最后一步是進(jìn)行 ASIC 的版圖設(shè)計(jì),即將電路轉(zhuǎn)換成版圖,或者用可編程ASIC 實(shí)現(xiàn)(CPLD/FPGA)。圖 1.3.1 是“自底向上”和“自頂向下”兩種設(shè)計(jì)方法的設(shè)計(jì)步驟。

2019-02-27 14:00:22

組合邏輯模塊化設(shè)計(jì)之靜態(tài)數(shù)碼管顯示一

同樣可以再繼續(xù)分解為多個(gè)更底層的模塊,這就是自頂向下的設(shè)計(jì)思想,也是目前主流的數(shù)字系統(tǒng)設(shè)計(jì)思想,而模塊化設(shè)計(jì)就是遵循這一設(shè)計(jì)思想的重要設(shè)計(jì)方法。事實(shí)上,無論多么復(fù)雜的系統(tǒng)總能夠逐步分解為多個(gè)

2022-07-29 15:50:16

能通過組件實(shí)現(xiàn)ec20模塊撥號(hào)的功能嗎

我想通過ec20模塊實(shí)現(xiàn)撥號(hào)的功能,能通過組件實(shí)現(xiàn)嗎?我沒有找到相應(yīng)的接口。

2022-08-15 10:07:01

計(jì)數(shù)器:運(yùn)行它就會(huì)在0和1之間跳轉(zhuǎn)不會(huì)實(shí)現(xiàn)自加,這是為什么?

這就是簡單的程序一運(yùn)行它就會(huì)在0和1之間跳轉(zhuǎn)不會(huì)實(shí)現(xiàn)自加,這是為什么求指導(dǎo)。

2018-02-22 14:28:29

請(qǐng)教一下,動(dòng)態(tài)調(diào)用時(shí)各個(gè)VI之間的數(shù)據(jù)交互是怎么實(shí)現(xiàn)的

想請(qǐng)問一下,一般編的大程序,如果是主界面程序采用動(dòng)態(tài)調(diào)用各個(gè)模塊的子VI面板時(shí)。如果現(xiàn)在主界面程序和各個(gè)子VI之間有數(shù)據(jù)交互的話,一般都是怎么實(shí)現(xiàn)的。我用全局變量可以很簡單實(shí)現(xiàn),但是如果數(shù)據(jù)一大的話

2016-04-20 17:41:01

請(qǐng)問單片機(jī)如何通過I/O口實(shí)現(xiàn)斷電自關(guān)機(jī)?

單片機(jī)如何通過I/O口實(shí)現(xiàn)斷電自關(guān)機(jī)

2021-04-02 06:46:21

請(qǐng)問如何實(shí)現(xiàn)單片機(jī)與315m或433m模塊之間的通訊 ?

如何實(shí)現(xiàn)單片機(jī)與315m或433m模塊之間的通訊 ?

2023-11-08 06:47:29

遠(yuǎn)距離射頻卡讀寫器數(shù)字處理模塊的設(shè)計(jì)怎么實(shí)現(xiàn)?

本文較系統(tǒng)地介紹了一類遠(yuǎn)距離射頻卡讀寫器數(shù)字處理模塊的設(shè)計(jì),特別在于采用單片CPLD實(shí)現(xiàn)了射頻卡讀寫器數(shù)字模塊功能,采用了原理圖和VHDL相結(jié)合自頂向下的設(shè)計(jì)方法,樣機(jī)PCB版面積小,開發(fā)周期短

2021-05-07 06:00:47

I2C總線串行數(shù)據(jù)接口的Verilog 實(shí)現(xiàn)

本文介紹了I2C總線規(guī)范,并根據(jù)該規(guī)范對(duì)I2C進(jìn)行模塊化設(shè)計(jì),用Verilog HDL 語言對(duì)每個(gè)模塊進(jìn)行具體描述,并通過模塊之間的調(diào)用,基本實(shí)現(xiàn)了I2C的主機(jī)從機(jī)的發(fā)送和接收功能。

2009-06-15 10:44:03 144

144

144

144VB控件使用大全 (VB6.0中通過MSChart控件調(diào)用數(shù)

VB控件使用大全:《 VB6.0中通過MSChart控件調(diào)用數(shù)據(jù)庫 》

02.txt 《 用VB6實(shí)現(xiàn)動(dòng)態(tài)增減控件 》

03.txt ActiveX控件的創(chuàng)建

04.txt ADO控件和DATA控

2009-09-13 15:34:35 1264

1264

1264

1264虛擬儀器調(diào)用MessageBox函數(shù)的實(shí)現(xiàn)

虛擬儀器軟件設(shè)計(jì)中以圖形化語言LABVIEW為主,但在遇到LABVIEW不易實(shí)現(xiàn)的功能時(shí),可通過在LABVIEW中調(diào)用其他函數(shù)來實(shí)現(xiàn)。本文介紹了在LABVIEW中調(diào)用Win32 APIMessageBox的方法和配置CLF

2009-09-14 15:07:36 23

23

23

23ASM51無參數(shù)化調(diào)用C51函數(shù)的實(shí)現(xiàn)

【摘 要】利用匯編模塊對(duì)C51模塊進(jìn)行“無參數(shù)”式調(diào)用,從根本上避開了傳統(tǒng)匯編模塊和C51模塊之間調(diào)用時(shí)的繁瑣接口編程問題,本文以實(shí)例驗(yàn)證了該方法的優(yōu)越性和有效性。

2009-05-18 22:01:00 1159

1159

1159

1159

ARM linux系統(tǒng)調(diào)用的實(shí)現(xiàn)原理

大家都知道linux的應(yīng)用程序要想訪問內(nèi)核必須使用系統(tǒng)調(diào)用從而實(shí)現(xiàn)從usr模式轉(zhuǎn)到svc模式。下面咱們看看它的實(shí)現(xiàn)過程。

2011-05-30 11:24:36 2158

2158

2158

2158調(diào)用DLL實(shí)現(xiàn)LabVIEW數(shù)據(jù)采集

介紹了在LabVIEW 中調(diào)用外部程序代碼的方法。詳細(xì)探討了DLL 文件的調(diào)用方法,并通過實(shí)例介紹了基于非NI 公司的數(shù)據(jù)采集卡的數(shù)據(jù)采集的實(shí)現(xiàn).

2012-03-26 15:30:05 152

152

152

152基于linux系統(tǒng)實(shí)現(xiàn)的vivado調(diào)用VCS仿真教程

VCS-MX的版本,可以混合編譯Verilog和VHDL語言 由于在linux系統(tǒng)中個(gè)人用戶各種權(quán)限被限制,導(dǎo)致很多地方無法正常使用軟件之間的協(xié)調(diào)工作。 為了以防萬一,在此以個(gè)人用戶去實(shí)現(xiàn)vivado調(diào)用VCS仿真。

2018-07-05 03:30:00 10733

10733

10733

10733

淺談C、C++ 和 ARM 匯編語言之間的調(diào)用

12.4 C target=_blank style=cursor:pointer;color:#D05C38;text-decoration:underline;》C、C++ 和 ARM 匯編語言之間

2017-10-19 09:24:28 2

2

2

2實(shí)現(xiàn)多ARM節(jié)點(diǎn)通過無線通信完成對(duì)批量節(jié)點(diǎn)的程序燒錄

項(xiàng)目旨在實(shí)現(xiàn)多ARM節(jié)點(diǎn)通過無線通信完成對(duì)批量節(jié)點(diǎn)的程序燒錄。系統(tǒng)分為上位機(jī)、發(fā)射接收模塊和待燒錄節(jié)點(diǎn)三個(gè)部分,上位機(jī)通過ID號(hào)選擇待燒錄節(jié)點(diǎn)并通過無線模塊向下廣播燒錄數(shù)據(jù),各被選擇節(jié)點(diǎn)通過無線模塊

2018-02-02 05:53:30 1105

1105

1105

1105

單模光模塊和多模光模塊之間的區(qū)別

隨著光通訊、數(shù)據(jù)中心的發(fā)展,光模塊的應(yīng)用越來越廣泛。而光模塊類型、傳輸數(shù)據(jù)也是越來越多樣化。40G光模塊、100G光模塊;單模光模塊、多模光模塊等等。今天,給大家介紹的是單模光模塊和多模光模塊,這兩者之間的區(qū)別是什么。

2018-05-03 10:36:00 29339

29339

29339

29339透了解系統(tǒng)調(diào)用助你成為Linux下編程高手

Linux內(nèi)核中設(shè)置了一組用于實(shí)現(xiàn)各種系統(tǒng)功能的子程序,稱為系統(tǒng)調(diào)用。用戶可以通過系統(tǒng)調(diào)用命令在自己的應(yīng)用程序中調(diào)用它們。

2018-05-11 11:27:42 3105

3105

3105

3105

LabVIEW不同VI之間相互調(diào)用的詳細(xì)資料說明

本文檔的主要內(nèi)容詳細(xì)介紹的是LabVIEW不同VI之間相互調(diào)用的詳細(xì)資料說明,有需要的拿去。

2018-12-17 08:00:00 28

28

28

28Linux內(nèi)核模塊間函數(shù)調(diào)用正確方法

模塊之間發(fā)生調(diào)用關(guān)系是常有的事情,下面以兩個(gè)模塊A、B,B使用A模塊提供的函數(shù)為例,講解正確使用的方法。

2019-04-28 17:00:01 2139

2139

2139

2139你知道Linux系統(tǒng)調(diào)用的原理

系統(tǒng)調(diào)用是應(yīng)用程序與操作系統(tǒng)內(nèi)核之間的接口,它決定了程序如何與內(nèi)核打交道的。無論程序是直接進(jìn)行系統(tǒng)調(diào)用,還是通過運(yùn)行庫,最終還是會(huì)到達(dá)系統(tǒng)調(diào)用這個(gè)層面上

2019-05-16 16:21:31 1304

1304

1304

1304

Linux下系統(tǒng)調(diào)用的技巧

。N取0~5之間的整數(shù)。 參數(shù)個(gè)數(shù)為N的系統(tǒng)調(diào)用由_syscallN()負(fù)責(zé)格式轉(zhuǎn)換和參數(shù)傳遞。系統(tǒng)調(diào)用號(hào)放入EAX寄存器,啟動(dòng)INT 0x80 后,規(guī)定返回值送EAX寄存器。 (3)系統(tǒng)調(diào)用功能模塊

2019-04-02 14:36:48 284

284

284

284實(shí)現(xiàn)原理圖模塊化調(diào)用原理圖的具體步驟

我們?nèi)绾卧韴D模塊實(shí)現(xiàn)模塊化調(diào)用原理圖,原理圖實(shí)現(xiàn)多通道的設(shè)計(jì)從而一次性影響到我們的 PCB 多通道,這樣比我們使用片段調(diào)用,拷貝 room 還有更加方便和便捷。

2019-09-02 16:47:06 10509

10509

10509

10509

S71200 CPU通過ETHERNET與S7300 PN口之間TCP通信的方式

S7-1200與S7-300PN口之間的以太網(wǎng)通信可以通過TCP協(xié)議來實(shí)現(xiàn),使用的通信指令是在雙方CPU 調(diào)用T-block(TSEND_C,TRCVC,TCON,TDISCON,TSEND,TRCV)指令來實(shí)現(xiàn)。

2019-12-02 08:00:00 4

4

4

4.NET應(yīng)用程序可以直接調(diào)用WebAssembly模塊了

WebAssembly Runtime現(xiàn)已添加.NET Core API,開發(fā)者可直接在.NET應(yīng)用程序中調(diào)用WebAssembly模塊。

2019-12-10 11:35:38 2196

2196

2196

2196Linux的系統(tǒng)調(diào)用是什么

所謂系統(tǒng)調(diào)用是指操作系統(tǒng)提供給用戶程序調(diào)用的一組“特殊”接口,用戶程序可以通過這組“特殊”接口獲得操作系統(tǒng)內(nèi)核提供的服務(wù)。例如,用戶可以通過進(jìn)程控制相關(guān)的系統(tǒng)調(diào)用來創(chuàng)建進(jìn)程、實(shí)現(xiàn)進(jìn)程之間的通信等。

2020-06-11 09:33:03 2120

2120

2120

2120系統(tǒng)調(diào)用是如何實(shí)現(xiàn)的?

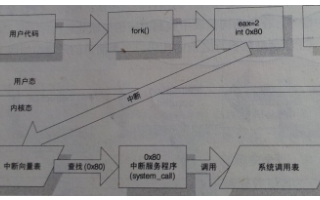

這張圖畫了挺久的,主要是想讓大家可以從全局角度,看下linux內(nèi)核中系統(tǒng)調(diào)用的實(shí)現(xiàn)。 在講具體的細(xì)節(jié)之前,我們先根據(jù)上圖,從整體上看一下系統(tǒng)調(diào)用的實(shí)現(xiàn)。 系統(tǒng)調(diào)用的實(shí)現(xiàn)基礎(chǔ),其實(shí)就是兩條匯編指令

2021-02-20 16:46:45 3583

3583

3583

3583

探討VHDL和Verilog模塊互相調(diào)用的問題

再 VHDL的模塊就是通過聲明一個(gè)元件(component)來調(diào)用這個(gè)Verilog模塊,將元件聲明提出來講,如下圖: 對(duì)比這個(gè)Veril

2021-04-30 14:06:04 8673

8673

8673

8673

系統(tǒng)調(diào)用具體是如何實(shí)現(xiàn)的

系統(tǒng)調(diào)用就是調(diào)用操作系統(tǒng)提供的一系列內(nèi)核功能函數(shù),因?yàn)閮?nèi)核總是對(duì)用戶程序持不信任的態(tài)度,一些核心功能不能直接交由用戶程序來實(shí)現(xiàn)執(zhí)行。用戶程序只能發(fā)出請(qǐng)求,然后內(nèi)核調(diào)用相應(yīng)的內(nèi)核函數(shù)來幫著處理,將結(jié)果

2021-09-29 11:10:56 3274

3274

3274

3274如何實(shí)現(xiàn)模塊與模塊之間點(diǎn)對(duì)點(diǎn)的通信

ESP8266有三種模式可以選擇,AP/STA/AP+STA,下面我們要實(shí)現(xiàn)的是模塊與模塊之間點(diǎn)對(duì)點(diǎn)的通信。

2022-02-28 10:48:36 3269

3269

3269

3269Linux內(nèi)核系統(tǒng)調(diào)用概述及實(shí)現(xiàn)原理

本文介紹了系統(tǒng)調(diào)用的一些實(shí)現(xiàn)細(xì)節(jié)。首先分析了系統(tǒng)調(diào)用的意義,它們與庫函數(shù)和應(yīng)用程序接口(API)有怎樣的關(guān)系。然后,我們考察了Linux內(nèi)核如何實(shí)現(xiàn)系統(tǒng)調(diào)用,以及執(zhí)行系統(tǒng)調(diào)用的連鎖反應(yīng):陷入

2022-05-14 14:11:46 1874

1874

1874

1874

Quartus II中通過調(diào)用IP核實(shí)現(xiàn)RS編解碼

的,特別是在短的中等碼長下,性能接近香農(nóng)限。本文是基于課題的要求,在Quartus II軟件中通過調(diào)用IP核的方式實(shí)現(xiàn)RS編譯碼過程,并通過Modelsim進(jìn)行仿真驗(yàn)證。

2022-09-28 10:02:21 2

2

2

2系統(tǒng)調(diào)用與普通的函數(shù)調(diào)用之間的區(qū)別

函數(shù)之間是可以相互調(diào)用的,這很簡單很happy有沒有。

要知道是代碼、是函數(shù)就可以相互調(diào)用,不管你用什么語言寫的。

2023-02-15 11:47:57 2968

2968

2968

2968

eda自頂向下的設(shè)計(jì)方法 eda自頂向下設(shè)計(jì)優(yōu)點(diǎn)

EDA(Electronic Design Automation,電子設(shè)計(jì)自動(dòng)化)自頂向下的設(shè)計(jì)方法是一種常見的電子電路設(shè)計(jì)方法。該方法將電路設(shè)計(jì)分為多個(gè)模塊,從系統(tǒng)級(jí)別出發(fā),逐步分解成較低層次的模塊,直到達(dá)到設(shè)計(jì)細(xì)節(jié)的層次,最終將每個(gè)模塊進(jìn)行詳細(xì)的設(shè)計(jì)。

2023-04-10 16:49:22 2371

2371

2371

2371Verilog中跨模塊調(diào)用的兩種不同方式的優(yōu)缺點(diǎn)討論

在寫Verilog TestBench,為了更方便更抽象地對(duì)底層模塊內(nèi)部的信號(hào)進(jìn)行控制,經(jīng)常會(huì)使用到跨模塊調(diào)用的方式,這個(gè)就叫做Cross Module Reference,縮寫為XMR。

2023-06-06 16:00:56 3121

3121

3121

3121

干貨分享 | TSMaster標(biāo)定模塊自動(dòng)化控制應(yīng)用指南

二、標(biāo)定自動(dòng)化控制場(chǎng)景與TSMaster實(shí)例2.1C腳本實(shí)現(xiàn)控制標(biāo)定模塊的啟動(dòng)與關(guān)閉的設(shè)計(jì)2.2C腳本代碼實(shí)現(xiàn)2.3測(cè)試與驗(yàn)證C腳本的標(biāo)定功能三、通過python調(diào)用

2023-06-21 17:45:40 482

482

482

482

調(diào)用HLS的FFT庫實(shí)現(xiàn)N點(diǎn)FFT

在HLS中用C語言實(shí)現(xiàn)8192點(diǎn)FFT,經(jīng)過測(cè)試,實(shí)驗(yàn)結(jié)果正確,但是時(shí)序約束不到100M的時(shí)鐘,應(yīng)該是設(shè)計(jì)上的延時(shí)之類的比較大,暫時(shí)放棄這個(gè)方案,調(diào)用HLS中自帶的FFT庫(hls:fft

2023-07-11 10:05:35 580

580

580

580

系統(tǒng)調(diào)用:用戶棧與內(nèi)核棧的切換(上)

當(dāng)發(fā)生系統(tǒng)調(diào)用、產(chǎn)生異常,外設(shè)發(fā)生中斷等事件時(shí),會(huì)發(fā)生用戶棧和內(nèi)核棧之間的切換, 本文從系統(tǒng)調(diào)用角度分析用戶棧與內(nèi)核棧的切換。 系統(tǒng)調(diào)用的演變 x86 的系統(tǒng)調(diào)用經(jīng)歷了 int / iret

2023-07-31 11:27:45 560

560

560

560

Linux系統(tǒng)調(diào)用的具體實(shí)現(xiàn)原理

文我將基于 ARM 體系結(jié)構(gòu)角度,從 Linux 應(yīng)用層例子到內(nèi)核系統(tǒng)調(diào)用函數(shù)的整個(gè)過程來梳理一遍,講清楚linux系統(tǒng)調(diào)用實(shí)現(xiàn)原理,這里我們以open系統(tǒng)調(diào)用為例來講解。

2023-09-05 17:16:46 719

719

719

719

python函數(shù)與函數(shù)之間的調(diào)用

函數(shù)與函數(shù)之間的調(diào)用 3.1 第一種情況 程序代碼如下: def x ( f ): def y (): print ( 1 ) return y def f (): print

2023-10-04 17:17:00 306

306

306

306CWDM光模塊與DWDM光模塊它們之間究竟有何區(qū)別呢?

的工作原理、優(yōu)缺點(diǎn)以及應(yīng)用領(lǐng)域。 1. 工作原理: CWDM通過將不同的光信號(hào)通過多個(gè)不同的波長進(jìn)行編碼來實(shí)現(xiàn)信號(hào)的復(fù)用。CWDM系統(tǒng)通常在波長范圍在1270nm到1610nm之間的固定波長

2023-12-07 09:07:29 326

326

326

326電口模塊SFP-GE-T:實(shí)現(xiàn)光口與電口之間的轉(zhuǎn)換

電口模塊是一種用于實(shí)現(xiàn)光口轉(zhuǎn)電口功能的設(shè)備,在網(wǎng)絡(luò)通信中起到重要作用。電口模塊沒有光電轉(zhuǎn)換的過程,只是傳輸電信號(hào)。本文介紹電口模塊的作用、分類、以及使用方法。

2024-01-08 13:38:47 271

271

271

271

verilog如何調(diào)用其他module

。 1.2 為什么要調(diào)用其他模塊? 在復(fù)雜的設(shè)計(jì)中,我們通常需要實(shí)現(xiàn)各種不同的功能,并且這些功能往往可以通過不同的模塊來實(shí)現(xiàn)。通過調(diào)用其他模塊,我們可以將問題分解為更小的子問題,并且可以更方便地實(shí)現(xiàn)和維護(hù)我們的設(shè)計(jì)。 1.3 調(diào)用模塊的基本語法

2024-02-22 15:56:25 325

325

325

325 電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論