2.1.6 SelectIO資源

Spartan-6有豐富的I/O資源,包括SelectIO和RocketIO。

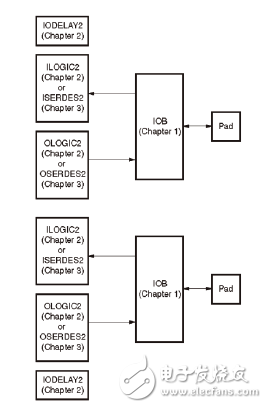

Spartan-6每個(gè)I/O片(Tile)包含兩個(gè)IOB、兩個(gè)ILOGIC2、兩個(gè)OLOGIC2和兩個(gè)IODELAY2,見圖2-37。

在這一小節(jié)里,分以下幾個(gè)方面介紹Spartan-6的SelectIO資源。

SelectIO的電氣特性。

SelectIO的邏輯資源(ILOGIC2、OLOGIC2)。

SelectIO的高級(jí)邏輯資源(ISERDES、OSERDES、Bitslip)。

圖2-37 I/O片結(jié)構(gòu)圖

一、 SelectIO IOB的電氣特性

所有的Spartan-6 FPGA有高性能的可配置SelectIO驅(qū)動(dòng)器與接收器,支持非常廣泛的接口標(biāo)準(zhǔn)。可以通過編程控制I/O的輸出強(qiáng)度、斜率以及片上終端OCT。

每個(gè)IOB包含輸入、輸出和三態(tài)SelectIO驅(qū)動(dòng)器。這些驅(qū)動(dòng)器可以按照各種I/O標(biāo)準(zhǔn)配置。

單端I/O標(biāo)準(zhǔn)(LVCMOS、LVTTL、HSTL、SSTL、PCI)。

差分I/O標(biāo)準(zhǔn)(LVDS、RSDS、TMDS、差分HSTL和SSTL)。

注意:差分輸入和VREF相關(guān)輸入是由VCCAUX供電。

Xilinx軟件庫(kù)提供了很多Spartan-6 I/O的原語(yǔ),包括用于單端信號(hào)的IBUF(輸入緩沖器)、IBUFG(時(shí)鐘輸入緩沖器)、OBUF(輸出緩沖器)、OBUFT(三態(tài)輸出緩沖器)和IOBUF(輸入/輸出緩沖器);以及用于差分信號(hào)的IBUFDS(輸入緩沖器)、IBUFGDS(時(shí)鐘輸入緩沖器)、OBUFDS(輸出緩沖器)、OBUFTDS(三態(tài)輸出緩沖器)和IOBUFDS(輸入/輸出緩沖器)。

二、 SelectIO的邏輯資源

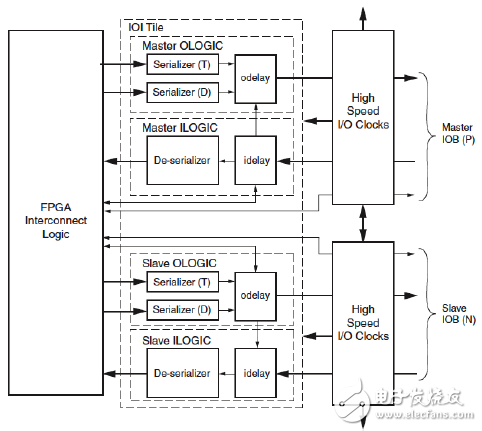

SelectIO的邏輯資源是指I/O驅(qū)動(dòng)器與接收器之后的邏輯,包含了Spartan-6 FPGA的所有基本I/O邏輯資源,如圖2-38所示。其中包括的資源如下。

組合輸入/輸出。

三態(tài)輸出控制。

寄存器輸入/輸出。

寄存器三態(tài)輸出控制。

雙倍數(shù)據(jù)速率(DDR)輸入/輸出。

DDR輸出三態(tài)控制。

IODELAY2提供對(duì)高分辨率可調(diào)延遲單元的控制。

支持NONE、C0和C1三種對(duì)齊模式的DDR輸出。

支持NONE、C0和C1三種對(duì)齊模式的DDR輸入。

ISERDES。

OSERDES。

圖2-38 I/O片內(nèi)的SelectIO邏輯資源

一個(gè)I/O片(IOI)管理兩個(gè)IOB。IOI包含兩個(gè)單端輸入/輸出,或者一個(gè)差分輸入/輸出的完整電路和一個(gè)內(nèi)部互聯(lián)模塊。兩個(gè)IOB組合在一起是為支持高速的差分接口。

在單端模式下,主IOB驅(qū)動(dòng)引腳P,從IOB驅(qū)動(dòng)引腳N。在差分模式下,主從IOB組合在一起可以實(shí)現(xiàn)串并轉(zhuǎn)換,其數(shù)據(jù)速率是單端模式下的1~2倍。每個(gè)I/O支持3種配置模式:鎖存型I/O、非鎖型I/O和寄存器型I/O。I/O還可以配置為2:1/3:1/4:1的SERDES。鎖存/寄存器時(shí)鐘來自GCLK驅(qū)動(dòng)的全局時(shí)鐘網(wǎng)絡(luò)或者高速I/O時(shí)鐘網(wǎng)絡(luò)。

IODELAY2是一種可選資源,設(shè)計(jì)者可以根據(jù)需要在輸入/輸出路徑上加入此延時(shí)模塊,IODELAY2的延時(shí)是可編程的,可以通過DRP指定或者通過例化IODELAY2原語(yǔ)指定。此延時(shí)可以是固定延時(shí),也可以是可變延時(shí)。

三、 ILOGIC2資源

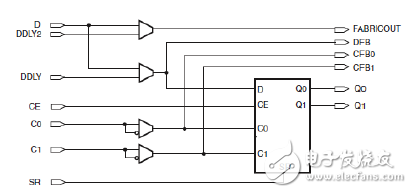

圖2-39所示為ILOGIC2邏輯框圖,它可支持以下功能。

邊沿觸發(fā)D型觸發(fā)器。

IDDR(NONE、C0或C1)模式。

鎖存器。

異步/組合邏輯。

圖2-39 ILOGIC2邏輯框圖

(1) 異步/組合邏輯。

當(dāng)有下列情況之一時(shí),軟件會(huì)自動(dòng)生成組合通路,使輸入驅(qū)動(dòng)器與FPGA內(nèi)部邏輯資源直接連接。

FPGA的輸入數(shù)據(jù)與內(nèi)部邏輯直接相連,而沒有用寄存器。

“打包I/O寄存器/鎖存器到IOB中”的屬性設(shè)置為OFF。

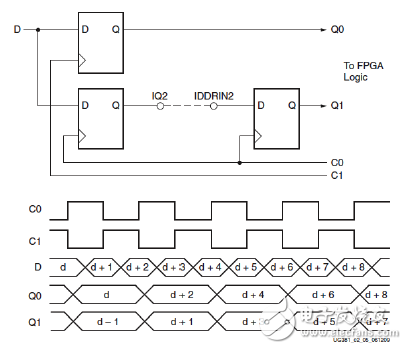

(2) IDDR模式。

Spartan-6器件的ILOGIC2中有專用寄存器來實(shí)現(xiàn)輸入雙倍數(shù)據(jù)速率(DDR)寄存器。可以通過例化IDDR2的原語(yǔ)來使用此功能。

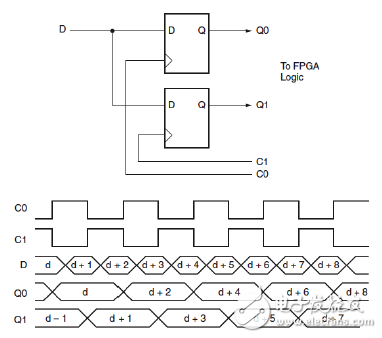

IDDR2的屬性DDR_ALIGNMENT有3種模式:NONE、C0和C1。

在NONE模式下,輸入DDR時(shí)序如圖2-40所示。寄存器在C0上升沿將輸入數(shù)據(jù)D寄存到Q0,C1上升沿將下一輸入數(shù)據(jù)D寄存到Q1。

圖2-40 DDR_ALIGNMENT=NONE時(shí)輸入DDR時(shí)序示意圖

在某些情況下,輸入數(shù)據(jù)必須同步到一個(gè)時(shí)鐘域里,通常C0同步。但是在頻率比較高的情況下,這種同步相對(duì)比較困難,因?yàn)橛行r(shí)間僅為時(shí)鐘周期的一半(50%占空比的情況下)。Spartan-6器件中的IDDR2包含了專用的邏輯,可以在ILOGIC2內(nèi)部進(jìn)行時(shí)鐘域的同步。

當(dāng)DDR_ALIGNMENT為C0(或C1),信號(hào)Q0(Q1)在C1(C0)再次寄存,通過內(nèi)部互聯(lián)將輸入數(shù)據(jù)同步到同一時(shí)鐘域。時(shí)序圖如圖2-41所示。

圖2-41 DDR_ALIGNMENT=C0\C1 的輸入DDR

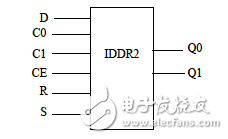

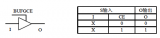

IDDR 的原語(yǔ)如圖2-42 所示。

圖2-42 IDDR2 的原語(yǔ)

四、 OLOGIC2 資源

如圖2-43所示,OLOGIC2主要由兩部分組成,分別是輸出數(shù)據(jù)路徑和三態(tài)控制路徑。

這兩個(gè)部分可以配置成以下模式。

邊沿觸發(fā)D 型觸發(fā)器。

DDR 模式(NONE、C0 或C1 同步方式)。

電平敏感鎖存器。

異步/組合邏輯。

圖2-43 OLOGIC2 邏輯模塊

(1) 組合數(shù)據(jù)輸出和三態(tài)控制路徑。

當(dāng)有下列情況之一時(shí),軟件會(huì)自動(dòng)生成組合通路,將FPGA 內(nèi)部數(shù)據(jù)直接輸出到輸出驅(qū)動(dòng)器或驅(qū)動(dòng)器的控制端。

FPGA 內(nèi)部邏輯數(shù)據(jù)直接輸出到輸出驅(qū)動(dòng)器或驅(qū)動(dòng)器的三態(tài)控制端,而沒有經(jīng)過寄存器。

“打包I/O 寄存器/鎖存器到IOB 中”的屬性設(shè)置為OFF。

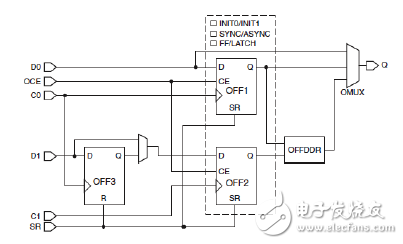

(2) ODDR模式。

Spartan-6器件的OLOGIC2中具有專用寄存器,用來實(shí)現(xiàn)DDR輸出寄存器。例化ODDR2原語(yǔ)可以使用此功能。當(dāng)使用OLOGIC2時(shí),會(huì)自動(dòng)使用多路復(fù)用器,多路復(fù)用器的控制端產(chǎn)生于時(shí)鐘信號(hào),不需要手動(dòng)控制。ODDR2 有兩個(gè)時(shí)鐘輸入,相位差180°。

ODDR2 支持以下操作模式。

NONE 模式:允許設(shè)計(jì)人員在C0 和C1 時(shí)鐘的上升沿將兩個(gè)數(shù)據(jù)通過DDR多路復(fù)用器送至輸出引腳,如圖2-44所示。

圖2-44 DDR_ALIGNMENT=NONE 下的ODDR2

C0模式:在時(shí)鐘C0上升沿時(shí),將兩個(gè)數(shù)據(jù)通過DDR多路復(fù)用器送至輸出引腳。

C1模式:在時(shí)鐘C1上升沿時(shí),將兩個(gè)數(shù)據(jù)通過DDR多路復(fù)用器送至輸出引腳。

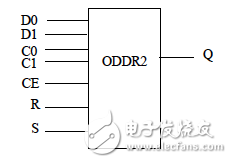

ODDR原語(yǔ)如圖2-45所示。

圖2-45 ODDR原語(yǔ)

五、 可編程延遲單元IODELAY2

每個(gè)IOB包含一個(gè)延時(shí)單元,可以配置成輸入延時(shí)或者輸出延時(shí),當(dāng)引腳用作雙向口時(shí),還可以通過T端來控制輸入/輸出延時(shí)的切換。Spartan-6中IODELAY2的延時(shí)不會(huì)自動(dòng)補(bǔ)償溫度或電壓帶來的延時(shí)差異,但是用戶可以通過精確計(jì)算,來設(shè)置IODELAY2的具體延時(shí)值。

圖2-46所示為延時(shí)單元的結(jié)構(gòu)圖。8位延時(shí)值對(duì)應(yīng)0~255個(gè)延時(shí)Tap,該延時(shí)值最低三位控制RING晶振的起始點(diǎn)。該晶振由輸入信號(hào)觸發(fā),經(jīng)過0~7個(gè)Tap的延時(shí)之后,其輸出作為時(shí)鐘,用來鐘控5位計(jì)數(shù)器。5位計(jì)數(shù)器中裝載了延時(shí)值的高5位,它會(huì)一直在0~31循環(huán),直到它的輸出翻轉(zhuǎn)到最初輸入到該模塊時(shí)的輸入值Data Input。延時(shí)精度范圍為1~255TAP。

圖2-46 延時(shí)單元的結(jié)構(gòu)圖

此延時(shí)單元有兩個(gè)局限,第一,延時(shí)最大值為1個(gè)位周期,超過此限制,接收數(shù)據(jù)會(huì)出錯(cuò);第二,在下一個(gè)邊沿到來之前,必須完成對(duì)第一個(gè)邊沿的處理,這種情況會(huì)發(fā)生在接收高速數(shù)據(jù)流時(shí)。

如何避免上述兩個(gè)局限呢?

對(duì)于第一個(gè)限制,通過確保延時(shí)值小于一個(gè)輸入數(shù)據(jù)的位周期(1UI)就可以避免,通常設(shè)置為0.5UI,使數(shù)據(jù)采樣點(diǎn)位于眼圖的中心。

對(duì)于第二個(gè)限制,可以通過圖2-47所示的兩個(gè)延時(shí)鏈解決。一個(gè)延遲鏈延時(shí)輸入數(shù)據(jù)的正值部分,另一個(gè)延時(shí)鏈延時(shí)輸入數(shù)據(jù)的負(fù)值部分,這個(gè)處理機(jī)制的價(jià)值在于:通過設(shè)置兩個(gè)延遲鏈的不同延時(shí)值,校正了輸入數(shù)據(jù)的占空比。讀者可以在設(shè)計(jì)中調(diào)用IODRP2原語(yǔ)使用此功能。

圖2-47 每個(gè)延時(shí)模塊使用兩個(gè)延時(shí)鏈

六、 SelectIO的高級(jí)特性

除了上述SelectIO資源之外,Spartan-6還提供了更高級(jí)的邏輯特性,介紹如下。

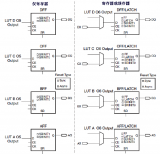

(1) 串并轉(zhuǎn)換器ISERDES2。

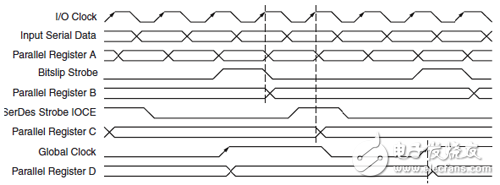

圖2-48和圖2-49分別為ISERDES2接收串行數(shù)據(jù)時(shí)的邏輯框圖和時(shí)序圖,利用ISERDES2將串行數(shù)據(jù)接收為4位并行數(shù)據(jù)。從時(shí)序圖中可以看到,Bitslip為4位數(shù)據(jù)的同步使能控制信號(hào)。

圖2-48 ISERDES2邏輯框圖

圖2-49 ISERDES2時(shí)序圖(1:4)

ISERDES2可以實(shí)現(xiàn)1:2、1:3或1:4串并轉(zhuǎn)換器功能,而且通過級(jí)聯(lián)的方式還可以實(shí)現(xiàn)1:5、1:6、1:7、1:8串并轉(zhuǎn)換器功能。

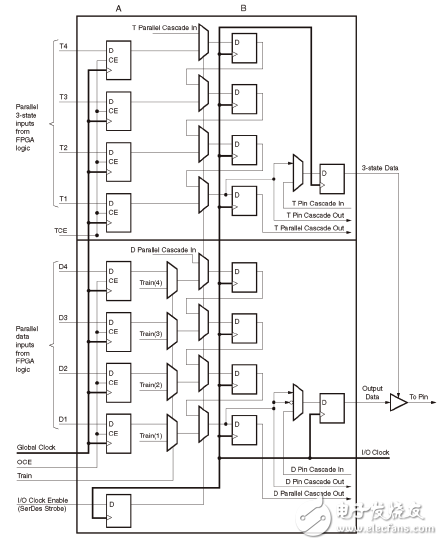

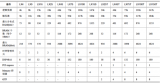

(2) 并串轉(zhuǎn)換器OSERDES2。

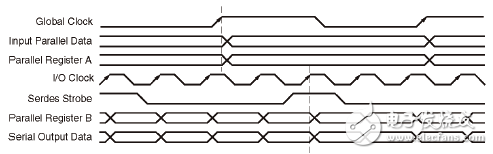

圖2-50與圖2-51分別為OSERDES2的邏輯框圖和時(shí)序圖,利用OSERDES2將4位并行數(shù)據(jù)轉(zhuǎn)換為串行數(shù)據(jù)輸出。

一個(gè)OSERDES2可以實(shí)現(xiàn)2:1、3:1、4:1并口轉(zhuǎn)換功能。當(dāng)用差分輸出時(shí),相關(guān)的2個(gè)IOB中的OSERDES2可以級(jí)聯(lián),從而可以實(shí)現(xiàn)5:1、6:1、7:1和8:1并串轉(zhuǎn)換功能。

設(shè)計(jì)者可以在HDL設(shè)計(jì)中,例化ISERDES2/OSERDES2原語(yǔ)來實(shí)現(xiàn)輸入數(shù)據(jù)解串和輸出數(shù)據(jù)串行化操作。

利用這些資源,可以很方便地實(shí)現(xiàn)高速串行數(shù)據(jù)的收發(fā),例如用它實(shí)現(xiàn)LVDS接口。

更多資料請(qǐng)參考附帶光盤中的《Spartan-6 IO資源用戶手冊(cè)》。

圖2-50 OSERDES2邏輯框圖

圖2-51 OSERDES2時(shí)序圖(4:1)

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論