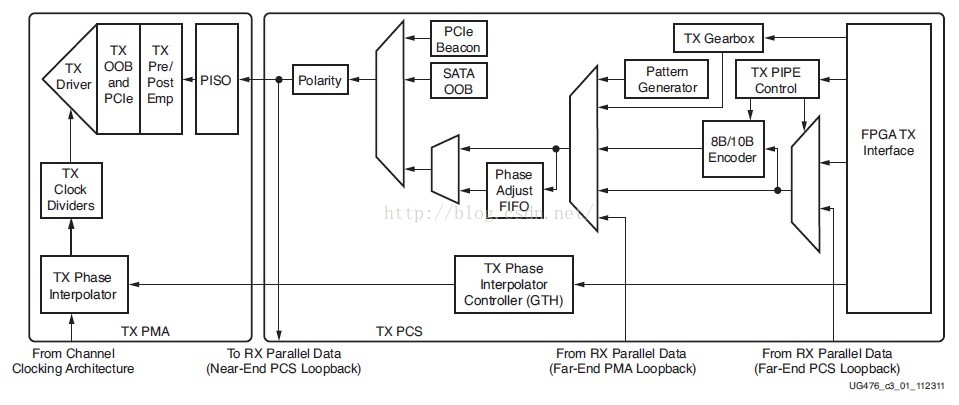

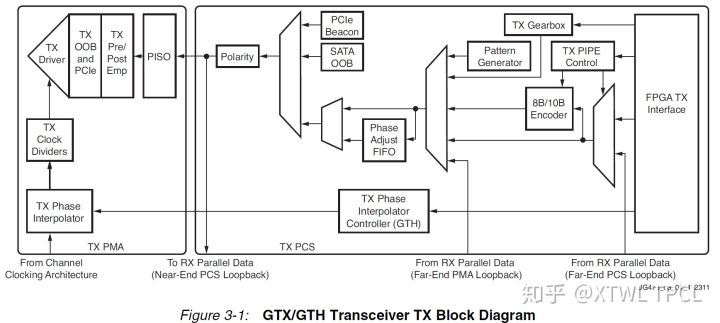

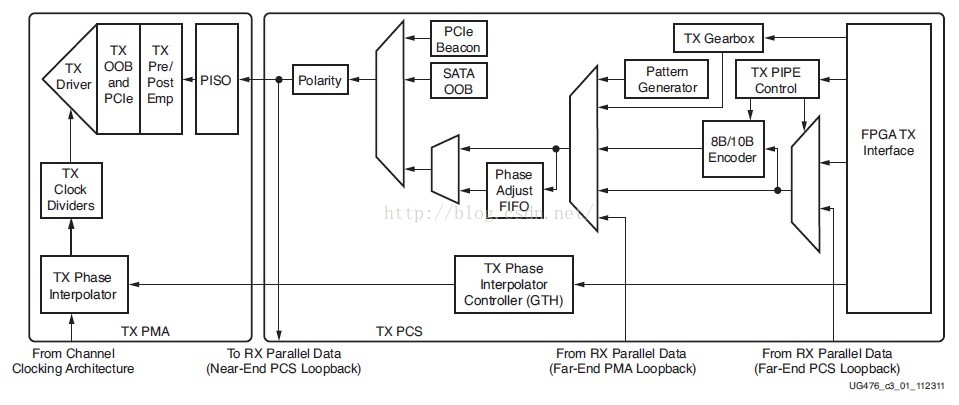

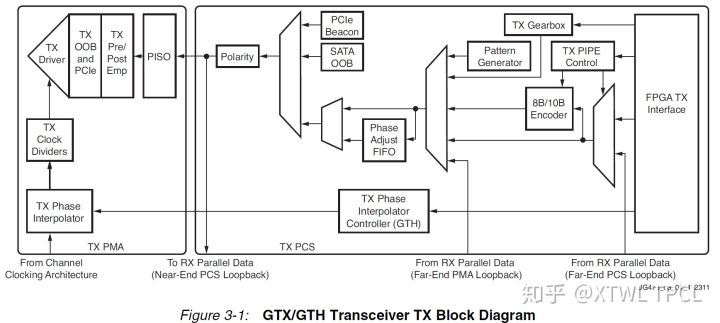

每一個收發器擁有一個獨立的發送端,發送端有PMA(Physical Media Attachment,物理媒介適配層)和PCS(PhysicalCoding Sublayer,物理編碼子層)組成

2020-11-20 11:27:39 5566

5566

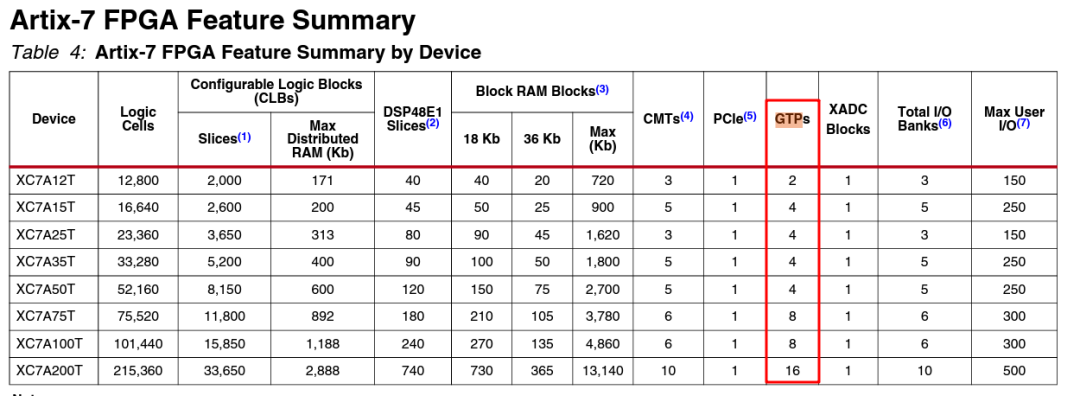

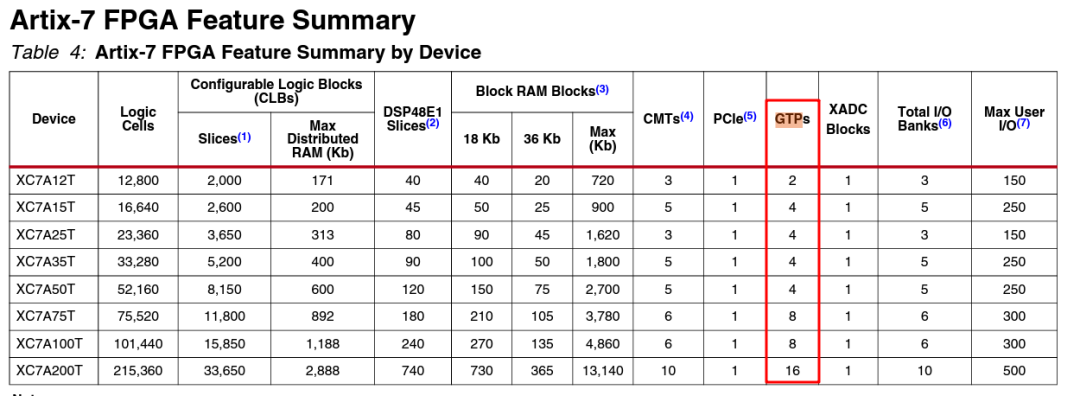

xilinx的7系列FPGA根據不同的器件類型,集成了GTP、GTX、GTH以及GTZ四種串行高速收發器,四種收發器主要區別是支持的線速率不同,圖一可以說明在7系列里面器件類型和支持的收發器類型以及

2020-11-20 12:08:15 17712

17712

本文介紹Xilinx GT的一些概念,對GT沒有概念但是有時間的童鞋推薦先看一下此文(Xilinx 7系列FPGA 高速收發器GTX/GTH的一些基本概念),補充一些基礎概念。 隨著高速數據傳輸

2020-12-15 15:54:09 8902

8902 本來寫了一篇關于高速收發器的初步調試方案的介紹,給出一些遇到問題時初步的調試建議。但是發現其中涉及到很多概念。逐一解釋會導致文章過于冗長。所以單獨寫一篇基本概念的介紹,基于Xilinx 7系列

2020-12-15 17:18:16 4531

4531

FPGA收發器GTX/GTH參考時鐘接口提供兩種連接方式:LVDS(如圖1所示)和LVPECL(如圖2所示)。我們在選擇晶振時,至少要支持其中一種接口輸出電平標準。圖2所示的電阻值為一般推薦值,實際

2022-08-09 12:28:24 1703

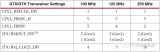

1703 嗨。在我的項目中,我使用Virtex 7和4 GTH接收40G流。我使用收發器向導為10GBASE-R生成GTH核心并從中復制GTH設置。這是正確的方式還是我需要使用GTH的特殊設置(RXCDR_CFG等...)?

2020-07-31 10:27:14

你好我嘗試使用xilinx 7系列收發器IP生成器示例(Vivdao提供)Thegt0_qplllock_in,gt0_qplloutclk_in,gt0_qplloutrefclk_in

2018-11-05 11:34:22

嗨,我想了解7系列收發器的Kintex xc7k325tffg900-2 FPGA。https://www.xilinx.com/support/documentation/user_guides

2020-05-11 08:09:08

你好我將生成一個7系列收發器的示例設計,在我的設計中有20位計數器發生器數據到7系列GTX。但運行工具流程,報告時間違規。怎么解決?時間約束:create_clock -name

2018-11-01 16:12:04

你好我將使用7系列trasnceiver IP來生成我的測試用例。在7系列收發器IP向導中,設置逗號對齊11_0111_1100。在下面,當txdata_in [19:0] = 5'h0037C

2020-08-24 10:07:29

嗨,對于7系列設備中的GTX收發器,為了獲得最佳功耗,我需要關閉未使用的收發器(Iam尋找類似于ug196 / ug198的數據,用于V-5系列,其中列的部分省電將多個情況)。請分享以下數據:關閉 - 一個GTX四核關閉 - GTX quad中的一個收發器問候,瑪尼

2020-07-19 07:27:37

FPGA高速收發器設計原則高速FPGA設計收發器選擇需要考慮的因素

2021-04-09 06:53:02

親愛的同事們,最近我從Vertex 6 ML605到Vertex 7 VC707板上升了一個固件。在代碼中,使用了GTX收發器的“同步丟失”輸出。但是在Vertex 7 GTX收發器中不再存在“失去

2020-06-16 09:32:28

描述與 Xilinx MGT 表征板結合使用時,PMP6577 是一套完整的電源解決方案,適用于 Xilinx 7 系列 GTX/GTH收發器。提供高達 12A (1V AVCC)、高達 8A

2018-09-11 08:56:59

Xilinx Virtex-6系列選型1 Xilinx公司Virtex-6 FPGA共有3個系列:Virtex-6 LXT – 高邏輯密度,高速串行收發器,高密度IOVirtex-6 HXT – 高

2012-02-28 14:56:59

你好我想用7系列收發器IP,但我不知道為什么GTX可以高速運行?為什么GTX收發器的速度比基本的IOB快?

2020-08-13 10:31:42

車道對齊過程中遇到問題。是否可以通過GTX通道綁定功能對齊通道?我可以簡單地將通道綁定序列設置為7系列FPGA收發器向導中的/ R /或/ A /來進行初始通道校準工作嗎?

2020-08-18 10:03:51

引言:本文我們介紹Xilinx 7系列FPGA收發器硬件設計主要注意的一些問題,指導硬件設計人員進行原理圖及PCB設計。本文介紹以下內容:GTX/GTH收發器管腳概述GTX/GTH收發器時鐘

2021-11-11 07:42:37

親愛的社區,我開始設計和使用在使用ISE 14.5實現ip-core時提供的GTX收發器示例。我使用帶有FM-S14適配器的Kintex Evalboard KC705(為我提供了4個額外的SFP

2020-07-15 09:10:15

嗨,我正在使用Virtex-6 FPGA GTX收發器向導,版本1.12。我使用Web包許可證進行模擬。device = xc6vlx75tdevicefamily = virtex6package

2020-06-17 13:58:20

嗨,我有2個靜態配置的GTX收發器用于HD-SDI操作。我可以使用一個收發器的Txoutclk為兩個收發器配備Txusrclock嗎?通過這種方式,我可以只用1個Txusrclock為FPGA邏輯

2020-08-19 07:43:50

一、概述

IBERT(集成誤碼率測試儀)是xilinx為7系列FPGA GTX收發器設計的,用于評估和監控GTX收發器。IBERT包括在FPGA邏輯中實現的模式生成器和檢查器,以及對端口的訪問

2023-06-21 11:23:12

你好,關于GTP / GTX收發器的JTAG實現,我有幾個問題。1. JTAG是否針對GTP / GTX收發器實現(因此可以驅動和讀取引腳以進行電路板驗證)2. JTAG組件放在GTP磁貼中的哪個

2020-06-18 14:41:02

嗨,我需要在XC7K325T FPGA中充分利用GTX資源。結果,我必須以這種方式使用一個四邊形,它的兩個頻道應該服務于10Gb / s鏈路和另外兩個--1Gb / s鏈路。這意味著,兩個通道必須

2020-07-22 13:25:20

穩定。給SERDES收發器的GTX/GTH參考時鐘應采用專用引腳,對用于FPGA邏輯的全局時鐘設計必須仔細的考慮,包括內部PLL、并行接口時鐘、JESD204邏輯核以及用戶邏輯時鐘。此外,必須 確保給

2018-10-16 06:02:44

高速差分IO信號的基礎知識: 1、初步認識GTX 當你接觸到FPGA的高速串行通信時,比如GTX收發器,一條TX發送線,一條RX接收線,這時候你肯定會聯想到UART串口,UART串口通信多么簡單

2018-08-16 09:59:19

,支持PCI Express Gen2(5Gbps/lane); ?支持64bit DDR3-1600,容量1GByte; ?該FPGA內嵌16個高速串行收發器RocketIO GTX; ?4個

2014-11-24 15:31:02

,pin_to_pin兼容FPGAXC7K410T-2FFG900,支持8-Lane PCIe、64bit DDR3、四路SFP+連接器、四路SATA接口、內嵌16個高速串行收發器RocketIO GTX,軟件

2015-01-28 15:48:55

嗨,我正在使用7系列GTX收發器的極光接口。我試圖谷歌“為極光接口/ GTX收發器重新安裝PCB布局限制”,但沒有找到任何有用的信息。請向我提供極光接口/ GTX收發器所需的詳細PCB限制。提前致謝,Mihir K Patel

2020-07-16 08:59:26

的收發器而編寫的。現在,我想為6G配置收發器,如6G.jpg附件中的XC7k325t-2。在參考設計中,還有一個適用于6G的頂級包裝。但是當我使用這個時,沒有生成RX / TX收發器時鐘。我認為這是由于在

2020-08-14 10:05:53

你好!我試圖在xc7k355t FPGA中實例化20個GTX收發器。所有20 GTX的核心配置都相同。在實施階段發生以下錯誤:[放置30-640]放置檢查:此設計需要比目標設備中更多

2020-08-20 13:39:54

你好,我將在Kintex7板上測試GTX收發器的iBERT設計代碼。我想檢查一個簡單的環回。我沒有SMA電纜連接GTX trnasceiver模塊的SMA連接器。你能指導我有沒有辦法將GTX收發器的RX,TX引腳連接在一起?謝謝

2020-07-22 11:44:31

引腳上?!我知道向導GUI漂亮的四邊形圖片讓我從QUAD114中選擇了一個clk但是我該如何將Si570 clk綁定到哪里?我一直在閱讀UG476 7系列FPGA GTX / GTH收發器用戶指南,以

2019-09-24 07:33:04

我正在嘗試將Kintex 7 FPGA與CMOS輸入DAC連接。我相信這意味著我需要使用標準IO引腳而不是GTX收發器。標準IO引腳上的最大頻率和數據速率是多少?謝謝。

2020-05-14 09:31:31

“txpll_divsel”和“內部數據路徑”的值,我在收發器用戶指南(UG476)或Coregen生成的代碼中找不到對它們的任何引用。有誰知道這些值應該是什么?謝謝!http://www.xilinx.com

2019-03-11 10:21:38

大家好!我是Verilog和FPGA編程的新手。我正在嘗試使用以太網和sma收發器實現兩個kc705板之間的連接。對于以太網,我使用了Tri模式以太網mac IP核,對于板卡連接,我使用了7系列

2020-04-16 09:31:37

嗨,如何將一個7系列收發器轉移到另一個7系列收發器?我正在使用12G SDI視頻收發器,它在一個Transeiver銀行(在我的案例中為kintex xc7k325tffg900-3的Bank

2018-10-30 18:03:36

大家好 我正在嘗試在FPGA V6之間建立通信鏈接。我正在關注“LogiCORE IP Virtex-6FPGA GTX收發器向導v1.9”文檔。在測試示例中使用PCIeconnectors但我想

2020-05-19 07:35:21

嗨,我在使用Vivado 2013.4的7系列收發器向導生成示例測試平臺時遇到了麻煩。有一次,我能夠生成示例tb,但現在每當我創建一個新項目并生成一個收發器時,我都沒有看到示例tb文件(即框架gen

2020-07-22 10:36:26

你好當我將7系列收發器向導用于Kintex-7設備(XC7K70T)時,我無法將GTX速率設置為高于6.6 Gbps的值。 Kintex-7 GTX應該以11.3 Gbps的速度運行,但似乎只適用于

2019-03-06 09:49:16

有沒有辦法用7系列收發器接收數據并將這些數據保存到BRAM,同時在填充時將其讀出?如果是這樣,除了來自IP目錄的收發器IP和BRAM IP的收發器向導之外,還需要什么? AXI從BRAM讀出到PC

2019-04-26 11:18:18

你好我試圖在KC705板上使用收發器來生成比特流。我正在使用Vivado 2012.3和7系列FPGA收發器向導v2.3。我之前使用過具有不同傳輸者名稱的IBERT核心。IBERT收發器名稱類似于

2020-07-28 10:29:31

嗨,我的問題:GTH支持SATA 3.0嗎?我的FPGA器件是v7-690tffg1761,只有GTH可用。在xilinx

2020-07-26 17:41:45

大家好,我試圖在我自己的基于Kintex 7(XC7K325t-ffg900-1)的FPGA平臺上使用GTX收發器來啟動XAUI應用程序。為了生成GTX核心,我使用了Core Generator

2020-07-19 09:01:44

,有沒有提到上述信號規格的手冊?我使用以下工具.FPGA:Virtex7PCIe端點:用戶邏輯的Gen1 4lane(供應商IP)GTX:Vivado 2014.4,7系列FPGA收發器向導版本3.4感謝你的幫助。謝謝。Yoshioku

2020-05-04 09:05:44

)。數據寬度為4位。我需要先將數據從計算機上傳到FPGA的內部存儲器,然后以10GHz的時鐘頻率輸出數據。有可能這樣做嗎?我通過“7系列FPGA GTX / GTH收發器用戶指南”掃描,發現“7系列

2020-08-28 13:22:46

嗨,我已經實現了K7-410T的所有16個GTX收發器,實現了一組線速率為2.97Gbps的SMPTE SDI接口。在調試時,我發現RX15的接收質量很差。其BER太高,無法完成下游處理。有人可以給我一些指導來改善GTX收發器的RX功能嗎?我應該調整一些關鍵參數嗎?謝謝。

2020-08-12 06:01:35

Virtex-6 FPGA GTX收發 User Guide:This document shows how to use the GTX transceivers in Virtex®

2009-12-31 17:05:28 25

25 CTM系列隔離CAN收發器模塊選型指南

以CTM1050T為代表的隔離CAN收發器由廣州致遠電子有限公司提供,是目前唯一一家能提供DC2500V電器隔離的CAN收發器,本文將介紹

2010-03-26 18:05:55 75

75 TRF6900 射頻收發器評估板用戶指南

2016-08-16 19:07:48 0

0 千兆收發器用戶手冊V2.0

2016-12-23 01:56:36 0

0 F1非網管收發器用戶手冊V1.1.0

2016-12-23 01:42:28 0

0 10_100_1000M_千兆收發器用戶手冊V2.0

2016-12-23 01:43:30 0

0 Virtex-7 GTH 收發器與Altera Stratix V GX 收發器的功能對比情況

2018-06-06 01:45:00 3572

3572

賽靈思Virtex-7 GTX收發器演示

2018-05-24 13:49:00 4199

4199 設計人員呼吁提升10G+ 芯片到芯片和背板性能, 依賴接收機均衡來補償信號失真。觀看視頻, 并排比較 Xilinx? Virtex?-7 FPGA GTH 收發器 和 Altera Stratix V GX 收發器的均衡能力。

2018-05-23 15:47:00 3974

3974

本文主要介紹了PSMC設計器用戶指南及技巧。

2018-06-05 17:28:00 4

4 7系列FPGA GTH收發器實現了與10GBASE-KR標準100%的電氣一致性。

在本視頻中,您將看到Virtex?-7 FPGA通過24英寸背板的規范接收機干擾容限測試。

2018-11-20 06:01:00 5042

5042 首次演示新型Xilinx 7系列GTH收發器,通過背板以13.1 Gb / s的速度運行。

2019-01-03 13:25:38 4048

4048 Xilinx GTX(12.5 Gb / s)收發器與SFP +和10G背板一起運行。

2018-11-30 06:36:00 9807

9807 Virtex-7 GTH收發器與Altera Stratix-V GX器件Battle Kits Demo

2018-11-30 06:31:00 2787

2787 通過Virtex-7 2000T FPGA中的GTX收發器實現高速串行性能。

2018-11-22 06:27:00 3461

3461 了解現在能夠以12 Gb / s的速率運行的7系列Kintex-7和Virtex-7 FPGA系列中的GTX收發器。

2018-11-22 05:49:00 4129

4129 本章介紹virtex-6 FPGA GTH收發器向導,并提供相關信息,包括其他資源、技術支持和向xilinx提交反饋。向導自動執行創建HDL包裝器的任務,以配置virtex-6設備中的高速串行GTH收發器。

2019-02-20 09:35:45 4

4 Chipscope?Pro ibert Core for Kintex?-7 FPGA GTX收發器是可定制的,設計用于評估和監控Kintex-7 FPGA GTX收發器。該核心包括在FPGA邏輯

2019-02-26 11:02:48 6

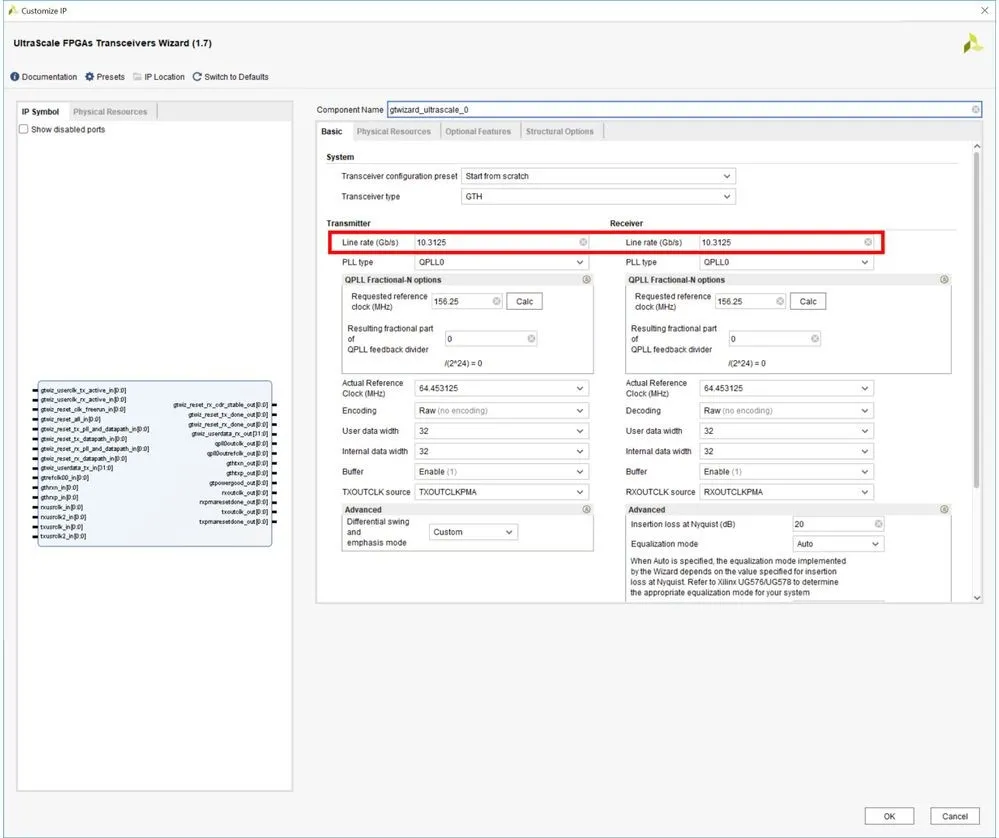

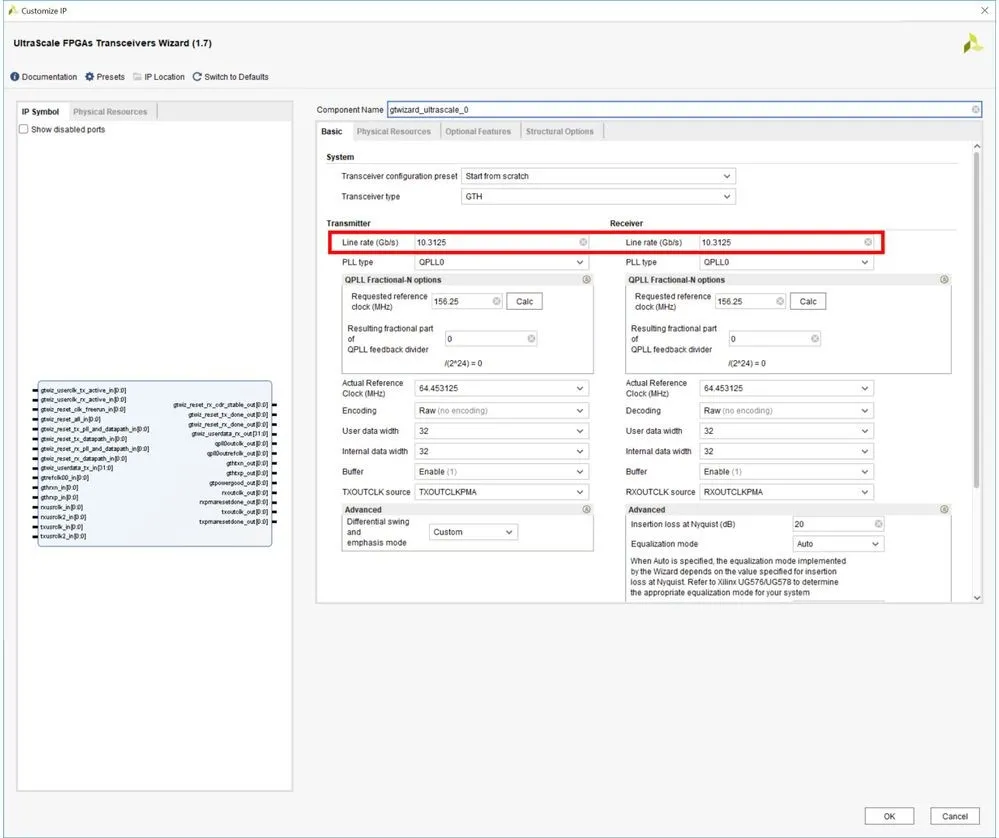

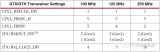

6 由于 UltraScale/UltraScale+ GTH/GTYTransceiver Wizard 不允許更改線速率設置,因此必須由收發器用戶手動執行更改。

2020-09-03 10:04:29 4583

4583

FPGAs TransceiversWizard 中僅含一項線速率設置。 由于 UltraScale/UltraScale+ GTH/GTYTransceiver Wizard 不允許更改線速率設置,因此必須由收發器用戶手動執行更改。 1. 如何通過

2020-11-04 14:48:20 7158

7158

FPGA 針對需要超高速串行連接的應用進行了優化,Virtex?-6HXT FPGA通過結合6.6 Gbps GTX收發器和11.18 Gbps GTH收發器,提供了業界最高的串行帶寬,以實現下一代分組和傳輸,交換結構。 ,視頻切換和成像設備。Virtex-6 FPGA系列

2021-04-14 11:53:31 4122

4122

IBERT(集成誤碼率測試儀)是xilinx為7系列FPGA GTX收發器設計的,用于評估和監控GTX收發器。IBERT包括在FPGA邏輯中實現的模式生成器和檢查器,以及對端口的訪問和GTX收發器的動態重新配置端口屬性,還包括通信邏輯,以允許設計在運行時通過JTAG進行訪問。

2021-05-02 22:10:00 5587

5587

引言:本文我們介紹GTX/GTH收發器時鐘架構應用,該文內容對進行PCIe和XAUI開發的FPGA邏輯設計人員具有實際參考價值,具體介紹: PCIe參考時鐘設計 XAUI參考時鐘設計 1.PCIe

2021-03-29 14:53:47 5441

5441

MPLAB PICkit 4在線調試器用戶指南說明。

2021-04-28 17:35:03 34

34 MPLAB Snap在線調試器用戶指南說明。

2021-04-29 09:48:50 18

18 引言:本文我們介紹Xilinx 7系列FPGA收發器硬件設計主要注意的一些問題,指導硬件設計人員進行原理圖及PCB設計。本文介紹以下內容:GTX/GTH收發器管腳概述 GTX/GTH收發器時鐘

2021-11-06 19:51:00 35

35 xilinx的7系列FPGA根據不同的器件類型,集成了GTP、GTX、GTH、GTZ四種串行高速收發器,可以支持多種協議如PCI Express,SATA,JESD204B等。

2022-03-01 17:17:20 3769

3769

不同芯片上使用的高速收發器也不同,而且同樣是GTX,不同系列芯片上的速率也可能不同。比如7系列的FPGA,GTP最高可以達到6.6Gb/s,GTX最高12.5Gb/s,GTH最高13.1Gb/s,GTZ最高28.05Gb/s

2022-08-02 09:05:57 5161

5161

電子發燒友網站提供《Logos系列FPGA高速串行收發器(HSST)用戶指南.pdf》資料免費下載

2022-09-26 10:25:17 22

22 Gigabit Transceiver(GTx),包括GTP、GTR、GTX、GTH、GTZ、GTY(傳輸速率不斷增加)等,不同系列的FPGA集成的GTx不同。

2023-03-27 14:24:40 1095

1095 R9A06G062GNP Sub-GHz 收發器用戶手冊:硬件

2023-05-19 18:40:39 0

0 R9A06G062GNP Sub-GHz 收發器用戶手冊:硬件

2023-06-29 19:33:32 0

0 電子發燒友網站提供《利用超大規模GTH收發器實現SMPTE SDI接口應用說明.pdf》資料免費下載

2023-09-13 11:09:30 2

2 電子發燒友網站提供《7系列FPGA配置用戶指南.pdf》資料免費下載

2023-09-15 10:19:57 1

1 電子發燒友網站提供《UltraScale架構GTH收發器用戶指南.pdf》資料免費下載

2023-09-15 10:15:17 0

0

電子發燒友App

電子發燒友App

評論