為了能夠實時地采集、處理、顯示視頻,設計并實現了一種基于雙PowerPC硬核架構的實時視頻處理平臺;用硬件實現視頻的預處理算法,并以用戶IP核的形式添加到硬件系統中,上層的視頻處理軟件程序則直接從存儲器中調用預處理后的圖像數據;重點介紹了在FPGA上構建雙PowerPC硬核架構的硬件系統;采用乒乓控制算法緩存一行圖像數據;用DMA的方式將圖像數據保存在存儲器中;以邊緣檢測作為視頻預處理算法的一個實例,在平臺上實現,實驗結果表明,用本平臺實現僅需40ms;本平臺能夠實時處理視頻,具有較高的實用價值。

0 引言

目前,視頻處理平臺大多使用DSP芯片進行圖像處理。實時視頻處理對系統性能提出了極高的要求,幾乎最簡單的功能也超出了單個通用DSP芯片的處理能力。一旦達到極限,通常只有增加額外的DSP芯片。2010年郭春輝提出一種基于多條帶、多DSP的并行視頻處理系統[1]。這種采用多處理器并行處理的方法雖然提高了處理速度,但增加了系統開發的復雜度,例如任務的合理分配,多處理器之間的通信、互斥等。當然,也增加了系統的功耗。DSP在性能方面的局限導致開發更為專用的芯片,如多媒體處理器,來克服這些問題。然而,事實證明這些器件除了在范圍極窄的一些應用中,都有不靈活的缺點,同時還存在性能瓶頸。基于處理器的方案,其局限在高分辨率視頻處理系統,如HDTV和醫療圖像系統中特別明顯。基本上,這種方案受限于多少個周期可以完成一次加法和乘法運算。

采用FPGA進行視頻處理使設計人員可以利用并行處理技術實現視頻信號處理算法。設計人員還可以在設計面積和速度之間進行折衷,并且可以用比DSP低得多的時鐘頻率完成給定的功能。更重要的是它的靈活性,能滿足固件升級及以后多媒體標準改進的要求。因此,本文提出一種基于FPGA 可重構的軟硬件協同設計的實時視頻處理平臺。平臺使用常規的FPGA開發工具,提供一個適應強、模塊化的架構,同時滿足高性能、低功耗的要求。

1 總體設計

視頻是一種連續變化的圖像信息。一般地,視頻處理大致可以分為底層處理(即預處理)和上層處理:底層處理的數據量大,算法實現比較簡單,且存在較大的并行性;上層處理的算法復雜,而數據量小。對于視頻處理的實現手段,在視頻的預處理階段,采用軟件實現是一個很耗時的過程,但采用硬件實現就可以對大量的視頻數據進行并行處理,能夠極大地提高視頻處理的速度;而在視頻上層處理階段,采用軟件實現則具有較高的性價比。

例如,Visicom公司發現對于中值濾波,DSP需要67個周期完成該算法。采用FPGA只需要運行在25MHz的時鐘頻率,因為FPGA可并行實現該功能。而DSP要達到同樣的性能則需要運行在超過1.5GHz的時鐘頻率。在這一特定的應用中,FPGA的方案比一個100MHz時鐘頻率的DSP的要強大約17倍[2]。

范圍廣泛的實時圖像和視頻預處理功能都適合采用FPGA硬件實現,它們包括實時:邊緣檢測、縮放、色彩和色差校正、陰影增強、圖像放置、直方圖功能、銳化、中值過濾、模糊分析等。

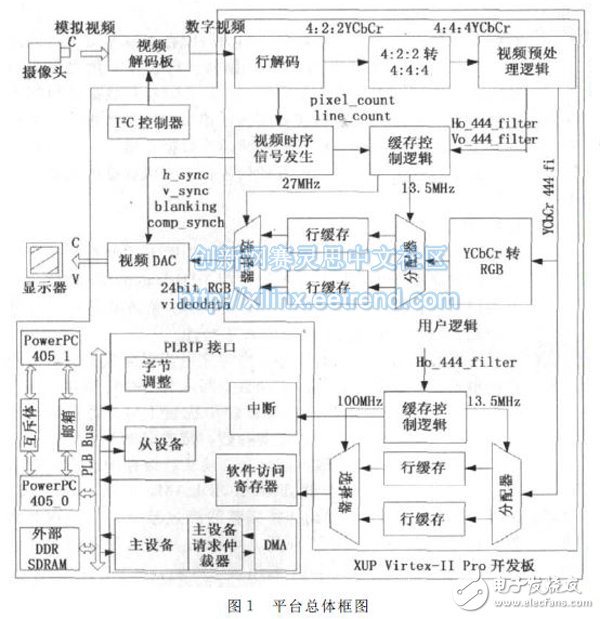

本設計的實時視頻處理平臺采用Xilinx公司大學計劃XUP Virtex-II Pro 開發板。它包括一個Virtex-II Pro XC2VP30FPGA,其內部有30816個邏輯單元,136個18位乘法器,2448kB塊RAM,兩個PowerPC 405處理器。還包括一根DDR SDRAM DIMM 插槽,可以支持高達2Gbytes的RAM,若干擴展接口和一個XSGA視頻接口。外接一塊視頻解碼板(支持ITU-R BT.656視頻標準),該開發板就能完成視頻的采集、處理和顯示。實時視頻處理平臺總體框圖如圖1所示。

視頻采集部分包括行解碼、4:2:2轉4:4:4、行緩存和緩存控制邏輯模塊、分配器、選擇器模塊等。測試部分包括YCbCr轉RGB、視頻時序信號發生模塊等。這兩部分是Xilinx公司提供的驗證設計,故本文只對其做簡單介紹。預處理部分包括視頻預處理邏輯模塊,下文將重點介紹該模塊。這三部分構成用戶邏輯。用戶邏輯和PLB IP接口構成一個完整的基于PLB總線的用戶IP核,可以方便地將其添加到視頻處理平臺的硬件系統中。

對于視頻信號源,可以是有線電視、DVD、VCR、CCD等。在對模擬視頻信號進行數字化處理時,先通過視頻解碼板把它轉換成符合ITU-R BT.656標準的數字視頻流。在FPGA芯片內,對該數字視頻流進行采集及預處理。經處理后的視頻流,一方面通過YCbCr轉RGB模塊、行緩存、及視頻DAC轉換成RGB信號,供顯示器顯示,作為測試用;另一方面,該視頻流還以DMA 的方式通過PLB總線保存到片外的DDR SDRAM 中。這樣,在PowerPC處理器上運行的應用程序就可以直接從DDR SDRAM 中調用已經過視頻預處理模塊處理的視頻數據,完成上層的視頻處理算法。

1.1 雙PowerPC硬核結構

IBM PowerPC 405處理器核是32位的RISC CPU 硬核,它嵌入到FPGA內用于實現高性能嵌入式應用。它包括標量5級流水線、獨立指令和數據緩存、1 個JTAG 端口、跡線FIFO (trace FIFO)、多個定時器和1個內存管理單元。它最高可以工作在300MHz頻率下,具有600+DMIPS的運行速度。

使用Xilinx公司提供的嵌入式開發套件EDK,在FPGA上構建視頻處理平臺的硬件系統,包括雙PowePC處理器、PLB總線、DDR SDRAM 存儲器、互斥體、郵箱、用戶IP核(包括視頻預處理邏輯模塊)和其它外設。

實現PowerPC雙核架構的難點是數據的并行處理和共享存儲器的訪問競爭。因此,在硬件系統中添加互斥體,它包括數量可配置的互斥信號量,每個互斥信號量包括一個32bit用戶配置寄存器(存儲專用數據),用來解決多核環境下訪問共享存儲器。在多核環境下,一個處理器可以用郵箱與另一個處理器通信,這樣就能實現視頻處理算法的并行執行。

1.2 行解碼模塊

經視頻解碼板轉換后的數字視頻流,符合ITU-RBT.656標準,通過9根信號線(1根27MHz時鐘線LLC_CLOCK和8根YCbCr視頻數據線)接入FPGA。行解碼模塊完成從數字視頻流中提取所需的視頻信息,包括場標識位F (處于奇場或偶場)、場狀態標識位V(處于場正程階段或場消隱階段)、行狀態標識位H (有效視頻起始信號或有效視頻結束信號),以及YCbCr視頻數據。視頻數據是以27M 字/秒的速率傳輸的,其順序是:Cb0,Y0,Cr0,Y1,Cb2,Y2,Cr2,…… 其中,Cb0,Y0,Cr0這3個字指的是同一像素的亮度和色差信號采樣,后面的Y1對應于下一個像素的亮度采樣。

1.3 4:2:2轉4:4:4模塊

為了數據傳輸和存儲的需要,ITU-R BT.656標準采用YCbCr4:2:2采樣格式,就是每采樣4個亮度信號,只采樣2對色差信號,因此在對視頻數據進行處理之前,必須重建YCbCr4:2:2采樣中丟失的Cb、Cr色差信號。在該模塊中,采用復制前一像素的Cb、Cr色差信號的方法,把YCbCr4:2:2采樣格式的視頻流轉換成YCbCr4:4:4采樣格式的視頻流。因此,模塊輸出的數字視頻流的頻率為輸入Y信號的頻率,即像素時鐘頻率,等于13.5MHz。

1.4 視頻預處理邏輯模塊

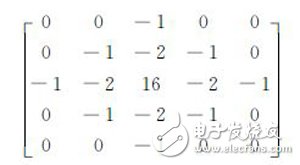

邊緣檢測是圖像處理中的重要內容。邊緣在邊界檢測、圖像分割、模式識別、機器視覺等中有很重要的作用。因此,本設計以邊緣檢測作為視頻預處理算法的一個實例。在邊緣檢測算法中,采用LOG算子,它通過求二階導數中的零交叉點來檢測邊緣,檢測出的邊緣寬度較細,有利于邊緣的精確定位。LOG算子使用的5×5模板為:

當然,工程師可以根據不同的需要,在該模塊中用硬件邏輯實現不同的視頻預處理算法,例如:縮放、色彩和色差校正、中值過濾等。

1.5 YCbCr轉RGB模塊

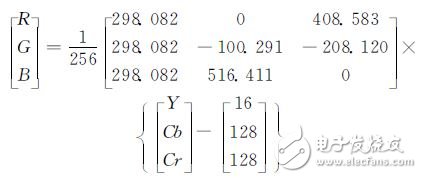

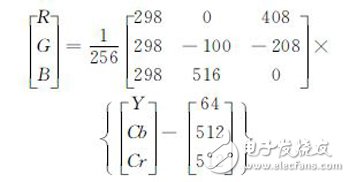

YCbCr和RGB是視頻圖像中常用的兩種色彩空間,用YCbCr色彩空間表示顏色易于實現壓縮和方便傳輸,但現有顯示設備大多采用RGB信號驅動,因此,對于視頻的顯示,需要將YCbCr信號轉換為RGB信號。YCbCr轉RGB的公式:

式中,Y、Cb、Cr 信號值的范圍是16~235,均為8比特。考慮到兼容性,在設計中,Y、Cb、Cr 信號均采用10比特位。結合FPGA器件的特點,及在用硬件邏輯實現浮點運算時,滿足精度和浮點的要求,將以上公式改為:

在RGB信號輸出時,取其高8位即可。對于公式中的運算“1/256”,在代碼設計時采用截數的方法實現。

1.6 行緩存

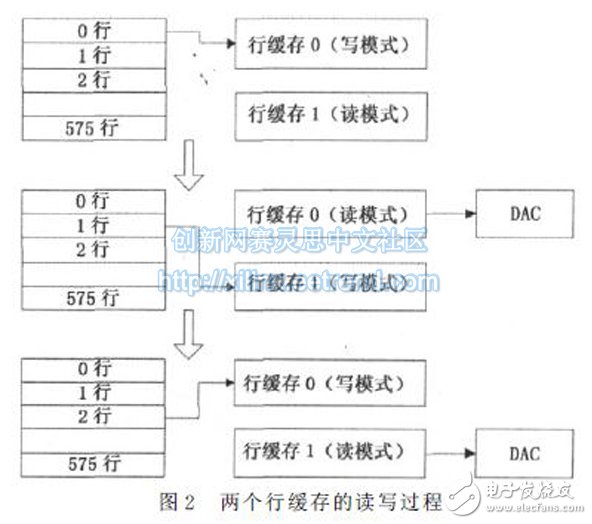

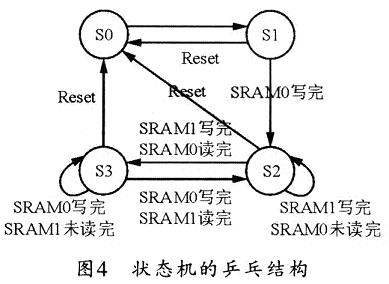

本設計采集的視頻分辨率為720×576,采用24位色(R、G、B各為8位),因此保存一幀圖像需要720×576×24=9.4921875Mbit的存儲空間。可見,一幀圖像數據所需的存儲空間是比較大的,不適合直接保存在FPGA 片內的塊RAM中。有幾種方案可以選擇,一是采用雙口RAM 作為幀緩存,但這種容量的雙口RAM 芯片較貴,勢必增加成本;二是采用兩片DDR SDRAM,通過乒乓控制算法構成雙端口的幀緩存,這種方法需另外制板,增加了設計的復雜度;三是在FPGA片內構建兩個行緩存,并采用乒乓控制算法,每次只存儲一行視頻數據,然后通過DMA的方式把576行視頻數據逐一存儲到DDR SDRAM 中。這樣,僅需兩行視頻數據的存儲空間,即720×2×24=33.75kbit,大幅減少系統對存儲資源的需求,一方面節約了成本,另一方面也充分利用FPGA 片內的塊RAM。圖2顯示了采用乒乓控制算法控制兩個行緩存讀寫視頻數據的過程。

對于分辨率為720×576的視頻圖像,第0行視頻數據首先寫入行緩存0,此時,行緩存0處于寫狀態,行緩存1處于讀狀態。當向行緩存0寫完第0行最后一個像素時,產生Ho_444信號。行緩存0隨之變為讀狀態,行緩存1變為寫狀態。接著,第1行視頻數據開始寫入行緩存1,同時,DAC從行緩存0讀出第0行視頻數據。當向行緩存1寫完第1行最后一個像素時,再次產生Ho_444信號。行緩存0隨之變為寫狀態,行緩存1變為讀狀態。然后,第2行視頻數據開始寫入行緩存0,DAC同時從行緩存1讀出第1行視頻數據。如此循環反復。因此,從整個控制模塊兩端看數據,輸入數據流和輸出數據流是連續不斷的,沒有任何停頓,完成數據的無縫緩沖與處理[3]。

1.7 PLB IP接口

PLB IP接口用于在PLB總線及用戶IP核之間提供一個快速實現且高度適應的接口。通過使用VHDL generics語句,根據用戶需求提供多樣的服務及可選的特性。在本設計中,選擇了中斷、軟件訪問寄存器和DMA等特性。

視頻數據自動寫入行緩存,當寫完一行視頻數據后,由用戶邏輯產生中斷信號,同時視頻數據寫入另一個行緩存,接著CPU響應中斷,并在中斷服務程序中配置DMA 寄存器,如源地址、目的地址、傳輸長度等參數,接著啟動DMA。然后,DMA申請得到PLB總線控制權,自動從行緩存中讀出視頻數據,并通過PLB總線存儲到DDR SDRAM,這樣循環反復,就在DDR SDRAM 中得到一幀完整的經過預處理后的視頻數據。這樣,在PowerPC處理器上運行的上層視頻處理程序就可以直接從DDR SDRAM 中調用這些數據。

2 實驗結果

通過示波器測量輸出的像素時鐘信號(PIXEL_CLOCK信號,該信號連接到視頻DAC),得到頻率瞬態值為27.03MHz,根據ITU-R BT.656 標準,1 行視頻流包括1728個字,一幀圖像包含兩場,共625行,則輸出一幀圖像所需時間為

,即FPGA對一幀圖像進行邊緣檢測的時間。注意到本設計所用的模擬攝像頭為PAL制式,也是40ms/幀圖像,所以,證明本設計實現了實時處理視頻。另外,視頻信號的測量必須注意終端匹配的問題[4]。

3 結論

本文提出一種高性能的實時視頻處理平臺,并在Virtex-II Pro XC2VP30FPGA上實現。相對于別的以硬件邏輯的形式實現圖像處理算法[5-6],該平臺采用雙PowerPC硬核架構,以用戶IP核的形式,為工程師在片上系統中實現各種視頻處理算法提供了最大的靈活性。實驗結果證明該平臺能夠實時處理視頻,具有較高的實用價值,將廣泛應用于消費類電子、視頻監控、遠程醫療和視頻會議等領域。

電子發燒友App

電子發燒友App

評論