3、2 采樣法

由于冒險多出現在信號發生電平跳變的時刻, 即在輸出信號的建立時間內會產生毛刺, 而在保持時間內不會出現, 因此, 在輸出信號的保持時間內對其進行采樣, 就可以消除毛刺信號的影響, 常用的采樣方法有2 種: 一種使用一定寬度的高電平脈沖與輸出相與, 從而避開了毛刺信號, 取得輸出信號的電平值。這種方法必須保證采樣信號在合適的時間產生, 并且只適用于對輸出信號時序和脈沖寬度要求不嚴的情況。另一種更常見的方法叫鎖存法, 是利用D 觸發器的輸入端D 對毛刺信號不敏感的特點, 在輸出信號的保持時間內, 用觸發器讀取組合邏輯的輸出信號。由于在時鐘的上升沿時刻, 輸出端Q = D , 當輸入的信號有毛刺時, 只要不發生在時鐘的上升沿時刻, 輸出就不會有毛刺。這種方法類似于將異步電路轉化為同步電路, 實現簡單, 但同樣會涉及到時序問題。

3、3 吸收法

由于產生的毛刺實際上是高頻窄脈沖, 故增加輸出濾波, 在輸出端接上小電容C 就可以濾除毛刺。但輸出波形的前后沿將變壞, 在對波形要求較嚴格時, 應再加整形電路, 該方法不宜在中間級使用。

3、4 延遲法

因為毛刺最終是由于延遲造成的, 所以可以找出產生延遲的支路。對于相對延遲小的支路, 加上毛刺寬度的延遲可以消除毛刺。但有時隨著負載增加, 毛刺會繼續出現,而且, 當溫度變化, 所加的電壓變化或要增加邏輯門時, 所加的延遲是不同的, 必須重新設計延遲線, 因而這種方法也是有局限性的。而且采用延遲線的方法產生延遲會由于環境溫度的變化而使系統可靠性變差。

3、5 硬件描述語言法

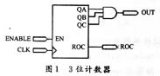

這種方法是從硬件描述語言入手, 找出毛刺產生的根本原因, 改變語言設計, 產生滿足要求的功能模塊, 來代替原來的邏輯功能塊。在圖1 電路中, 一個3 位計數器可能會在011 到100 和101 到110 發生跳變時產生毛刺, 究其原因是因為一次有2位發生跳變, 可以采用VHDL 語言對計數器編寫如下, 產生的計數模塊代替原來普通的計數器。

subdesign modcount

(clk, reset: input; q[2110 ]: output; )

variable

counter3

:MACH IN E O F B ITS ( r [2110 ])

W ITH STA TES ( r0= B"101" ,

r1= B"100" ,

r2= B"000" ,

r3= B"001" ,

r4= B"011" ,

r5= B"010" ,

r6= B"110" ,

r7= B"111") ;

begin

q[ ]= rr [ ];

counter31reset= reset;

counter31clk= clk;

CA SE counter3 IS

w hen r0= > counter3= r1;

w hen r1= > counter3= r2;

w hen r2= > counter3= r3;

w hen r3= > counter3= r4;

w hen r4= > counter3= r5;

w hen r5= > counter3= r6;

w hen r6= > counter3= r7;

w hen r7= > counter3= r0;

END CA SE;

end;

注意在新的計數器中, 每次狀態發生改變時Q 0, Q 1,Q 2 只有1 位發生跳變, 從根本上消除了毛刺。但計數器的輸出狀態沒有規律, 不便于其他電路利用。如果希望計數器的輸出狀態有規律變化以便其他電路使用, 可以考慮采用雙輸出電路, 一路是單信號輸出, 一路是正常計數輸出。這種方法從根本上消除了毛刺產生的根源, 具有普遍的意義, 對系統也不會產生影響, 是最為可靠的方法, 其不利之處是這種方法對VHDL 語言要求比較高, 必須對電路的工作狀態及其轉變有全面的分析和掌握, 而隨著電路的復雜度提高, 毛刺產生的來源繁雜, 實現起來比較困難。

對于一般情況下產生的毛刺, 可以嘗試用D 觸發器來消除。但用D 觸發器消除時, 有時會影響到時序, 需要考慮很多問題。所以應根據不同情況, 仔細地分析毛刺產生的來源和毛刺的性質, 結合系統資源選擇具體辦法, 消除毛刺的影響。

4 具體實例

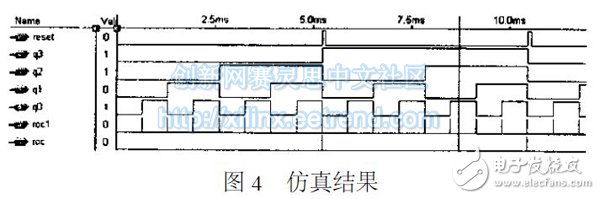

在實際應用中要對一個周期同步脈沖信號進行檢測,要求若在給定的時間內沒有檢測到同步信號則給出一定脈沖寬度的高電平, 作為復位信號。設計思想是采用一個計數器, 當有同步信號時對其清零, 并同時開始計數, 根據給定時間和系統時鐘周期設定計數器的模數, 經過給定的時間后輸出高電平, 滿足寬度后再置低。

實際要求檢測時間大約1 s, 脈沖寬度保持在20ms左右, 采用5 片74161 級聯, 第5 片計數器的ROC 接D 觸發器的使能端。同步信號輸入后, 清零并開始計數, 若不再出現同步脈沖, 經16^5 個時鐘周期后, 第5 片的RCO端輸出一個高電平, 使觸發器的Q 輸出D (高電平) , 再過16^33 2個時鐘周期后使第4 片的QA , QB, QC, QD 接組合門電路輸出低電平, 接到D 觸發器的計數器預制端,使Q 輸出為零。這樣就實現經一定延時后的一定寬度的脈沖。經仿真結果如圖4 所示。

電子發燒友App

電子發燒友App

評論