1 引言

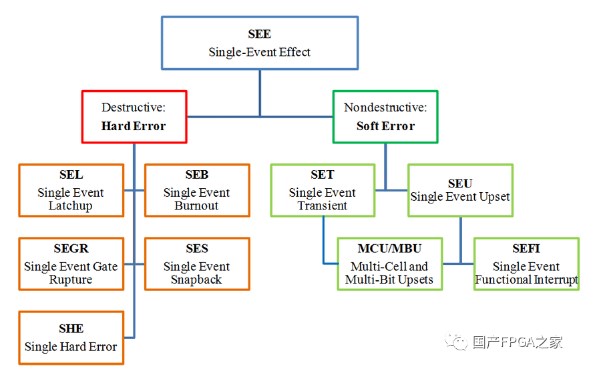

隨著現場可編程門陣列( FPGA) 芯片在商業、軍事、航空航天等領域越來越廣泛的應用, 其可靠性和可測試性也顯得尤為重要。對設計人員來說,FPGA 的使用相當靈活。然而, 正是這種應用的不確定性和重復可編程性, 增加了芯片測試的難度。目前, 已有較多工作集中于基于SRAM 結構的FPGA 測試方法研究[ 1-7] 。其核心問題是建立什么樣的測試模型, 以及施加什么樣的測試激勵, 使故障激活, 同時, 還能在可及端測量出來。因此, 還要確定在什么地方施加激勵, 在什么地方進行測量。

根據需求, FPGA 的測試大體可分為面向制造的測試過程( MT P) 和面向應用的測試過程( AT P)兩類。MT P 主要是從制造商的角度來測試, 測試成本主要體現在測試向量集長度所決定的測試時間的費用上。MTP 主要針對可編程邏輯塊( CLB) 、輸入輸出單元( IOB ) 、可編程連線( PI ) 及編程用的SRAM 等進行測試。AT P 是在應用級上的測試,也就是把FPGA 配置為特定的功能進行測試, 具有很強的針對性, 測試過程相對簡單。但是, 不管是MTP 還是AT P, 都至少有一個{ 測試配置( TC) , 向量實施( TS) } 的過程[ 6] 。完整的測試通常需要反復進行配置和測試。一般來說, 編程比較費時且編程后的配置速度較低。因此, FPGA 測試的關鍵在于如何在保證故障覆蓋率的前提下, 用最少的編程次數, 將FPGA 低速在線配置和高速測試有機地結合起來, 從而實現完整的測試。

本文介紹一種基于SRAM 結構FPGA 邏輯資源的測試編程方法, 并以Xilinx 公司的XC4000 系列[ 8] 為例, 在BC3192V50 數模混合集成電路測試系統上, 通過從串模式, 實現數據的配置和測試。

2 基于SRAM 結構的FPGA

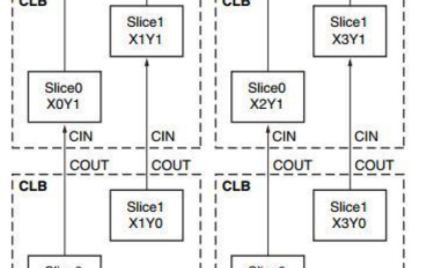

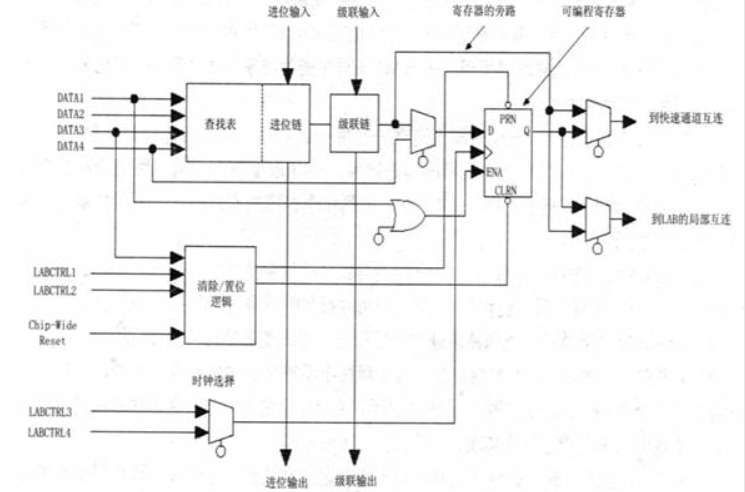

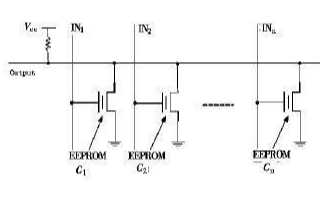

從編程原理來說, FPGA 主要有基于反熔絲( arrtifuse) 結構和基于SRAM 結構兩大類。XC4000 系列是基于SRAM 結構的, 其邏輯功能的配置基于內部陣列分布的SRAM 結構, 即通過對這些SRAM 進行不同的加電配置, 確定各個部分的邏輯功能; 也可通過加載不同的配置數據, 實現邏輯功能的不斷更新和反復改寫。實際上, 就是由加載于SRAM 上的配置數據決定和控制各個CLB、IOB 和PI 等的邏輯功能和相互之間的連接關系。基于SRAM 結構FPGA 的另一個重要特征, 在所謂的邏輯單元陣列( LCA) 結構。正是這個LCA 分布結構, 使之具備門陣列和可編程器件的雙重特征。LCA 像一個門陣列, 通過內部可編程連線, 把可編程邏輯塊按設計的要求連接起來, 實現陣列中的邏輯功能。

另外, 由于采用了先進的半導體工藝和改進的結構, XC4000E 系列能夠支持高達80 MHz 的系統時鐘頻率和超過150MHz 的內部性能。

3 測試編程

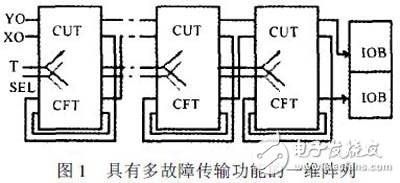

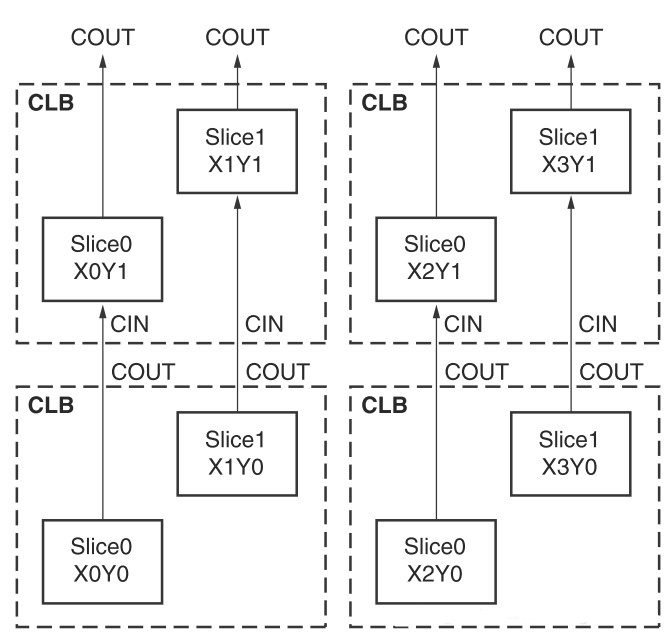

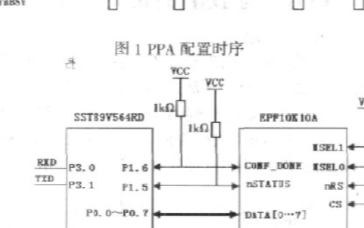

通過編程, 將每一行的CLB 連接起來, 形成一個一維陣列[ 1-2] ; 再將每個陣列作為整體進行測試,如圖1 所示。

?

故障模型采用多CLB 混合故障模型, 即一個FPGA 中可有多個邏輯單元發生故障, 而邏輯單元內的故障對不同的電路采用不同的故障模型。對于查找表結構, 假定其可有固定為"0"或"1"的固定故障; 而對于多路選擇器和觸發器, 則假定可發生各種功能故障[ 4-5] 。

每個陣列中的CLB 都按圖1 所示的連接方式進行編程, 前一個CLB 的輸出信號作為后一個CLB 的輸入信號, 只有左右兩端的CLB 與IOB 相連。所有CLB 都設計編程為相同的電路結構, 既是被測電路( CUT) , 也是故障傳遞電路( CFT) 。CLB 中的兩個查找表G 和F, 均設計為具有一個故障激活端( T) 、兩個故障傳遞端( Yn 和Xn) 和一個故障傳遞方式選擇端

( SEL) 的四輸入邏輯結構, 且使用相同的T 輸入和SEL 輸入。查找表F 的兩個輸入端( Yn 和Xn) 與此CLB 內兩個觸發器的輸出端( QYn 和QXn) 相連, 用于檢測和傳遞觸發器的故障信號。查找表G 和F 的兩個輸出信號( Yn 和Xn) 作為下一個CLB 中查找表G 的輸入信號( Yn+ 1 和Xn+ 1) 。

故障傳遞電路采用基于與門和或門的電路形式[ 4 ] 。用SEL 輸入控制是或門傳輸還是與門傳輸。此時, 如果有一個或多個CLB 的輸入輸出端有正常為1( 0) 、錯誤為0( 1) 的故障信息, 其輸出端總能觀察到故障信息0( 1) 。

對所有陣列并行地進行測試, 可以減少測試時間和所需要的IOB。同時, 因為所有CLB 都是同樣的編程結構, 因此, 可共用時鐘和垂直輸入, 不同陣列的輸入也可共用, 從而進一步減少了所需的IOB[ 1-2] 。

但是, 由于編程后的陣列是一個時序陣列, 故一定程度上增加了測試此陣列所需要的時間。另一方面, 由于每個CLB 在被測試的同時, 還要用來傳遞故障信息, 因此, 測試精度相對單獨用一行CLB 來傳遞故障信息的方法[ 3-5] 有所降低。

4 FPGA 的配置

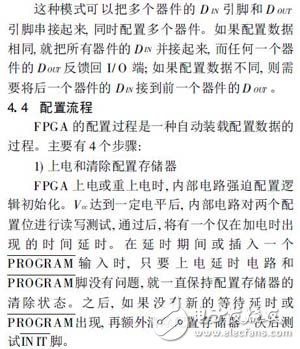

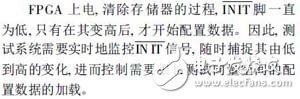

通常, 將配置數據存放于FPGA 外附的PROM或EPROM 中, 在系統加電或需要時, 自動載入SRAM 中; 亦可直接由微處理器控制, 載入數據, 且只要一直保持在加電狀態, 配置數據就不會丟失。FPGA 的在線配置, 就是把測試系統用作一個處理器, 再通過數字通道, 將配置數據裝載到LCA 器件, 從而確定其內部各部分功能和連線方式的過程。

4. 1 配置模式

XC4000 系列FPGA 根據配置模式管腳( M0、M1、M2) 的不同輸入, 產生三種是自裝載的主模式:主串模式( 000) 、主并向上模式( 100) 和主并向下模式( 110) ; 兩種外設模式: 同步外設模式( 011) 和異步外設模式( 101) ; 一種采用菊花鏈器件的串行從模式: 從串模式( 111) ; 以及一種附加的允許高速并行配置高容量XC4000EX 器件的從模式: 特快模式( 010) 。

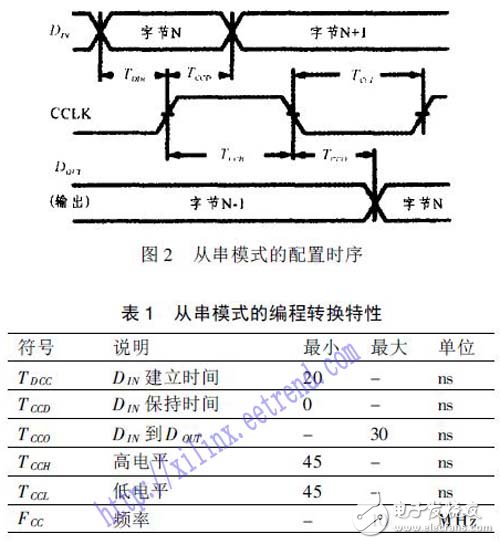

本文采用從串模式, 通過( 111) 模式管腳或缺省模式來選擇。此模式為系統加載FPGA 配置程序提供了最簡單的接口。串行數據DIN 和時鐘CCLK 可同時由一個微處理器的I/ O 口從外部提供。

4. 2 配置數據的格式

從串模式的配置數據以一個40 位的頭文件開始, 接著是一些實際的配置數據信息段, 每個信息段以一個0 起始、4 個錯誤校驗位結束, 長度和數目取決于器件的類型。在配置結束時, 提供啟動序列的4 個時鐘, 要求附加啟動的字節數據。具體來說,XC4006E 的配置文件長度為119, 840 位, 實際寫入119, 792 位。

4. 3 配置管腳和時序分析

?

?

?

?

5 系統的資源分配和測試實現

下面介紹如何用BC3192V50 測試系統實現FPGA 配置數據的加載和測試。該系統是由北京自動測試技術研究所開發研制的VXI 總線型數模混合集成電路測試系統。

5. 1 配置和測試資源

FPGA 的每個配置和測試過程, 需要兩個不同的測試程序{ TC, T S} 分別來完成。它們并存于系統內存里, 可隨時激活, 但所需要的時鐘頻率和存儲空間不同。

首先, 通過TC程序加載配置數據, 其速度比較低。配置后, 在持續供電的條件下, 通過TS 程序進行高速的功能測試和參數測試。

其次, 配置和測試過程使用的數字通道資源不同, 同一管腳在兩個過程的通道定義也有所不同。配置程序只用與配置相關的管腳; 測試程序要根據設計的邏輯功能確定管腳, 且不可以超過芯片的全部用戶可編程IOB 數。例如, 對于具體的芯片

XC4006E-4PC84C 來說, 其最大用戶可編程IOB 為61 個, 文中的編程方法使用了8 個輸入激勵數字通道和32 個輸出響應通道。

BC3192V50 測試系統最多可配置為8 塊通道板256 路高速數字測試通道, 最大測試速率為50MHz( 非復用) , 可選定配置后芯片電源控制方式( 掉電/ 不掉電) 。通過這種模塊化結構的系統設計,就可以實現配置和測試過程的多速率、多通道和持續上電等要求。

5. 2 配置程序自動生成

根據設計的邏輯電路結構、CLB 之間連線方式和測試向量等, 用Xilinx 公司ISE 集成綜合環境,對FPGA 進行Verilog 設計輸入和編譯, 生成所需要的位流文件。但由于該文件比較長, 按字節配置需要幾十萬甚至幾百萬條向量, 且內容隨編程信息的變化而變化。因此, 手工編制向量就顯得很不切實際。必須采用自動生成的方法, 實現配置數據的加載。為此, 專門開發了一個測試程序生成軟件, 用于將生成的位流文件轉化成系統可以識別的文本文件, 通過調用該文件, 實現數據的加載。

5. 3 配置數據加載

BC3192V50 測試系統采用了循環、跳轉、子程序調用和嵌套等指令, 數字通道具有歸零、歸一等激勵格式, 且分別有激勵、響應和記錄存儲區, 便于跟蹤、調試測試程序, 測試向量深度為256 k( 標準) / 1M( 擴展) / 4 M( 最大) , 內存中最多可以加載256 個測試程序, 等等。通過這些功能, 可以有效控制配置數據順利快速的加載。

5. 4 功能和參數測試

完成配置后的FPGA 就變成一個具有某種特定功能的器件, 可作為普通邏輯器件進行測試。所不同的是, FPGA 的I/ O 管腳非常多, 且可分別配置為TT L 或CMOS 兼容兩種類型。它們的直流參數能直接反映出FPGA 的性能。在功能測試通過后, 必須用精密測量單元( PMU ) , 對所有I/ O 管腳進行參數測試, 才比較完整。但參數測試往往比較費時。

BC3192V50 提供每16 管腳一個PMU 的并行進行參數測試能力, 通過采用這種多PMU 并行測試子系統, 非常有效地節省了測試時間。

綜上所述, 在測試系統BC3192V50 上測試FPGA, 實質上就是通過測試系統, 將FPGA 配置成所設計的邏輯結構, 然后施加測試向量, 完成配置后的功能和參數測試, 且根據需要, 可多次重復這種{ T C, T S} 的過程。

6 結束語

本文在國產數模混合集成電路測試系統BC3192V50 上, 實現了以XC4000 系列為例的基于SRAM 結構FPGA 可編程邏輯資源的測試。所闡述的測試系統的配置方法和實現過程具有很強的通用性。適用于支持串行配置, 并可通過{ T C, T S} 程序集, 完成測試過程的FPGA。但是, 當測試方法改變后, 所需要的測試程序集{ T C, T S} 的數量和內容也會改變。

電子發燒友App

電子發燒友App

評論