FPGA設計的基本原則

面積與速度折衷原則

面積和速度是ASIC芯片設計中一對相互制約、影響成本和性能的指標,貫穿FPGA設計的始終。在FPGA設計中,面積是指一個設計消耗的FPGA內 部邏輯資源的數量,可以用消耗的觸發器和查找表的個數或者是等效邏輯門數來衡量;速度是指一個設計在FPGA上穩定運行時所能 達到的最高頻率,由設計時序狀態決定。

關于面積和速度的折衷,應在滿足設計時序和工作頻率要求的前提下,占用最小的芯片面積;或者在所規定 的面積下,使得設計的時序余量最大,能夠在更高的頻率上穩定運行。通常,在資源足夠的情況下,更多是選擇速度的最優,這也是FPGA的 特點。在具體設計中,應根據具體性能指標要求,在保證系統功能和性能的同時,降低資源消耗從而降低功耗和成本。

硬件原則

第二個原則是硬件原則。

首先,要注意FPGA的邏輯設計所采用的硬件描述語言VHDL或Verilog與 軟件語言C和C++有本質區別,在使用硬件描述語言進行設計時,不應片面追求代碼的簡潔。

其次,要采用正確的編碼方法。要對所需實現的硬件電路的結構和相互連接有清晰的理解和構想,然后再用 適當的VHDL語言表達出來。實際上綜合軟件對所寫的代碼在進行推論的時候,得到的硬件結果會因編碼方式的不會而不同,直接影 響硬件的實現。

系統原則

第三個原則是系統原則。FPGA作為硬件系統設計,應該對設計全局進行宏 觀上的合理安排,包括邏輯功能模塊劃分、時鐘域信號的產生和驅動、模塊復用、時序或引腳約束、面積速度折衷等。這些系統上的考慮不僅關系到是否能夠最大程 度地發揮項目成員的協同設計能力,而且直接決定著設計的綜合、實現效果和相關的操作時間。

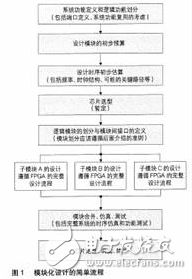

模塊化設計是系統原則的一個很好體現,它是自頂向下、模塊劃分、分工協作設計思路的集中體現,是大型 復雜系統的推薦設計方法。圖1是模塊化設計的簡單流程。

同步原則

在設計電路時,可以有異步電路和同步電路兩種實現方法。異步電路使用組合邏輯電路實現,沒有統一的時 鐘信號,容易產生毛刺和競爭冒險;同步時序電路使用組合邏輯和觸發器實現電路功能,主要信號和輸出信號都由時鐘驅動觸發器產生,能夠避免毛刺,信號穩定。

·從資源使用方面考慮,推薦使用同步設計。雖然在ASIC設計中同步電路 比異步電路占用的面積大,但是在FPGA中,是以邏輯單元衡量電路面積的,所以同步設計并不比異步設計浪費資源。

·從延遲設計方面考慮,異步電路的延時靠門延時來實現,比較難預測;同步電路使用計數器或觸發器實現 延時。

·同步設計時鐘信號的質量和穩定性決定了同步時序電路的性能,FPGA的 內部有專用的時鐘資源,如全局時鐘布線資源、專用的時鐘管理模塊DUL、PLL等。

·目前商用的FPGA都是面向同步的電路設計而優化的,同步時序電路可以 很好地避免毛刺,提倡在設計中全部使用同步邏輯電路。特別注意,不同的時鐘域的接口需要進行同步。

FPGA設計的技巧

乒乓操作

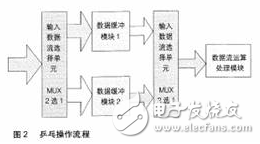

圖2是乒乓操作流程圖。從圖中可以看出,數據經過兩個緩沖模塊,在向緩沖 模塊1輸入數據的時候,緩沖模塊2的數據會送到下一級進行處理,從外部看數據流沒有停頓。所以乒乓 操作能夠提高處理速度。

實際上,乒乓操作是用一種低速模塊來處理高速數據流,即用兩個緩沖模塊實現了串并轉換,用兩個預處理 模塊并行,利用面積換速度。

串并轉換

串并轉換是FPGA設計的一個重要技巧,是數據流處理的常用手段,也是面 積與速度互換思想的直接體現。串并轉換的實現方法多種多樣,根據數據的排序和數量要求,可以選用以下方式:小的設計用寄存器、數據量比較大的用ROM、 復雜的串并轉換用狀態機,或者直接利用功能模塊來實現。

流水線操作

流水線操作是高速設計中一個經常用到的設計手段。如果某個數據的處理流程分為若干步驟,而且整個數據 處理是“單流向”的,即沒有反饋或者迭代運算,前一個步驟的輸出是下一個步驟的輸入,則可以采用流水線設計方法提高系統的工作頻率。

·流水線設計時,要對時序進行合理安排,每個操作步驟的劃分要合理,仔細考慮各個步驟間的數據流量。

·如果前級操作時間恰好等于后級操作時間,設計最為簡單,前級直接輸出到后級輸入就行了。

·如果前級操作時間大于后級操作時間,后級會經常空閑,可以對前級的數據進行適當緩存,再輸出到后級 的輸入端。

·如果前級操作時間小于后級操作時間,必須通過復制邏輯,將數據流分流和并行預處理,或者在前級對數 據采用存儲、后處理方式、否則會造成后級數據溢出。所以怎樣平衡各個模塊的處理時間,在設計中要給予適當的考慮。

數據接口的同步

·如果輸入數據的節拍和本系統處理時鐘同頻,可以直接用本系統的主時鐘對輸入數據寄存器進行采樣,完 成輸入數據的同步化。

·如果輸入數據和本系統的處理時鐘是異步的,要用處理時鐘對輸入的數據做兩次(或多次)寄存器采樣, 完成輸入數據的同步化。兩次(或多次)采樣的作用是抑制亞穩態的傳播,適用于對少量對錯誤不敏感的功能單元。

·為了避免異步的時鐘域產生錯誤的采樣電平,一般使用RAM、FIFO存 儲的方法完成異步時鐘域的數據轉換,在輸入端口使用上一級時鐘寫數據,在輸出端口使用本級時鐘來讀數據,能夠非常方便地完成異步時鐘域之間的數據交換。

時序電路設計

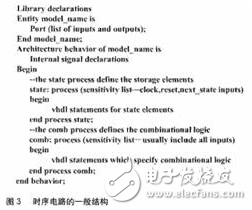

圖3給出了時序電路的一般結構。

首先是庫說明語句Library declarations。接著是實體 結構,給出實體模塊的名稱Entity,由Port引出的輸入輸出的清單。再后面是結構體,然后是 內部信號說明。接著設置了一個狀態進程,定義存儲元件,進程名稱為State process,敏感的清單一般是存儲元件,reset、next state、Input等信號,是存儲元件的輸入信號,在這些信號下,進程會激活。然后是狀態進程的Begin, 開始以后對狀態的元件進行VHDL描述,順序描述完以后,結束狀態進程。下面的設置是組合進程,這個進程的敏感清單通常包括所 有的輸入。接下來是進程的Begin,在Begin里頭給出了規定組合邏輯的VHDL描 述,最后是進程結束與結構體結束。

前面已經講過,FPGA設計盡量采用同步設計。這里要考慮同步硬件的RTL描 述。描述設計的寄存器到寄存器的功能,即描述寄存器之間組合邏輯的功能。

有效編碼方式和If-Then-Else比較

在組合進程和狀態進程中,都可能會用到If-Then-Else和case語 句,綜合出來的結果和組合邏輯情況一樣,都會有不同,case語句用一個模塊來實現,If-Then-Else用 帶有特權編碼的譯碼器實現。

在組合進程和狀態進程中,用If-Then-Else和case語 句帶來的問題

對Case語句的要求

一般情況下,如果不需要特權編碼,建議用Case語句。組合邏輯上,要求Case語 句對所有分支進行定義,如果有幾don't care輸出也可以利用,能夠節省描述方式。Case語 句能節省資源,減少延時。

Case語句在組合進程和時序進程中帶來的問題

·Case 語句在組合的進程(VHDL)或 在always語句(Verilog)中:

要求在case語句中,對所有分支中的所有輸出必須定義,才能防止出現鎖 存;如果不是所有的分支都定義了,可以在case語句之前利用一個缺省語句來防止鎖存的產生。

·C語句在時序進程(VHDL)或在always語 句(Verilog)中:

如果在Case語句的分支中有的輸出沒有定義,就會產生一個時鐘的使能信 號,這個信號并不出現錯誤,但是可能會產生一個很長的時鐘使能方程式,使設計不能實現。那么在case語句之前利用一個缺省語 句防止不必要的時鐘使能產生。

FPGA設計常用的一些模塊有:存儲單元、全局時鐘資源和鎖相環、全局復位/置位信號、高速串行收發器等,下 面做簡要介紹。

鎖存器與寄存器

鎖存是電平有效,在電平有效的情況下,輸入送到輸出;寄存器是時鐘沿有效,當時鐘到的時候才輸出。在 邏輯單元里頭除了查找表外都有寄存器,所以建議大家使用沿有效的寄存器,不要用增加組合邏輯來實現的鎖存器。

時鐘使能

VHDL程序的編碼方式將決定是不是利用時鐘使能信號,時鐘使能使得時序約束更容易控制。

鎖存與變量

推薦分配一個初始值或者信號給變量,就不會有反饋出現,如果一個變量沒有分配初始值,獲得一個信號鎖 存就要產生,可能引起設計功能不正確。鎖存的產生和變量的情況一樣,不要有不確定的條件產生。

DFF利用rising_edge

觸發器利用語句rising_edge(clk) 時鐘的上升沿,如果時鐘的上升沿來了,則數據給定,這是寄存。rising_edge是IEEE的 函數,是在1164的軟件包里定義的一個函數,規定了信號值必須是0和1,X、Z到1轉 換是不允許的,三態到1的轉換是不允許,必須是0到1。

DFF利用clk'event and clk=1

如果用clk'event and clk=十,clk就 是信號名稱,event是VHDL的一個屬性,規定了信號值的變化,那么CLK等 于1意味著正沿觸發。clk'event and clk=1,信號的名稱是clk,event表 示信號的數值需要有一個變化,等于1表示正沿觸發,是沿觸發的語句,綜合出來是觸發器、寄存器的推論。

移位寄存器

這里的描述是IF的異步清除CLK等于1的 時候,Q全置0,然后上升沿到達以后,如果使能等于1,Q等 于Q的低七位挪到高七位,補充一個入信號,是一個左移,移位寄存器是并行出,串行入,異步的清除和使能左移,如果增加和移去同 步控制,在這個方式出現移動,這個語句里頭信號只是表示高七位和進來的信號組合成一個八位的信號。

基本的計數器

基本的計數器主要有帶時鐘使能的計數器、帶同步清零的計數器、上/下計數器、帶同步加載的計數器、帶 同步加載和計數使能的計數器、帶同步加載和計數使能的計數器、帶同步加載的上/下計數器、模塊200計數器、使用整數的模塊200計 數器等,這里不再一一介紹,詳情可登錄查詢。

信號與變量

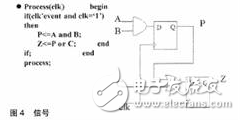

信號僅僅用做VHDL實體的連接口。信號僅可以在結構體內說明,它們可以 作為參數通過函數和過程。變量在進程塊、過程和函數內進行說明。信號賦值通過“<=”實現,變量的賦值通過“:=”實現,見圖4和 圖5。

三態Tri-states

IEEE的標準在STD_LOGIC軟件包中定義了三態的Z值, 仿真就是高阻態,綜合的時候轉換成三態緩沖器。

Altera器件只有I/0單元有三態緩沖器,其好處是消除了可能的總線連接,解決了 內部邏輯的位置問題。因為無需三態緩沖區,減少了器件的測試,節省了成本。其內部的三態必須轉換成組合邏輯,復雜的輸出使能容易引起錯誤和低效率邏輯,但 是在I/0單元里有三態緩沖器。

雙向管腳

當管腳被說明作為方向INOUT的時候,利用INOUT的 腳作為輸入或者是三態輸出,在程序中,設置了一個bi direction,作用雙向的INOUT信 號。當CE使能信號等于1的時候,來自核的from core信號送到 雙向腳,否則的話三態,這個時候雙向作為一個三態輸出,還有一個輸入賦給,來自信號送到三態,輸入送到內核。

存儲器

綜合工具有不同的能力來識別各種存儲器。為了識別各種存儲器,綜合工具對特定的譯碼類型非常敏感,通 常在綜合工具文件中有說明。綜合工具可能在結構實現上有一些限制,如只有同步寫、時鐘配置的限制、存儲器尺寸的限制等,必須說明一個陣列數據類型來保存存 儲器的值。存儲器有單端口Memory,單端口雙時鐘Memory,雙時鐘Memcry、ROM等。

電子發燒友App

電子發燒友App

評論