摘 要 :SATA作為一種高速串行, 點對點傳輸的硬盤接口, 已取代了IDE 硬盤接口。 目前在硬盤中使用較為普遍的是 SATAII 和SATAIII, 其線速率分別達到了3Gbit?s -1和6 Gbit?s-1。文中對 SATAII 協議進行了全面的分析,并利用 Xilinx公司的ISE開發(fā)工具和 ML507干估板完成了協議的軟 IP核編寫與調試。 所用 FPGA 型號為XC5VFX70T, 利用其中硬核Rocket IO GTX 實現了高速鏈路的功能,并使用多級流水線技術進行并行設計以提高整體速度。

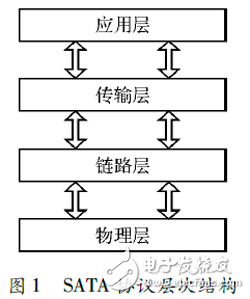

SATA作為一種高速串行鏈路已取代了 IDE作為 硬盤的標準接口。該高速差分鏈路使用吉比特傳輸和8B/10B 編碼技術, 其相比于IDE、 PATA 接口具有傳輸 速度更高、 設備升級更簡單和配置使用更便捷等優(yōu) 勢[1] 。 首先, 作為一種高速點對點的傳輸方式, SATA解決了直流偏置、 信號偏移、 碼間干擾等問題, 并提高 了傳輸的帶寬。 同時具備了更完善的查錯和糾錯能 力, 傳輸質量和傳輸可靠性得到了大幅提升。 其次,SATA接口相比于傳統(tǒng)的并行接口具有更少的引腳數 目, 更利于PCB板級的設計、 裝配和散熱。 最終,SATA 總線還支持熱捅拔并具有更低的功耗。SATA接口協 議具有層次化的結構[2-3] , 如圖1 所示, 從下到上分別 是物理層、 數據鏈路層、 傳輸層和應用層。 其中物理層 負責低壓差分信號的發(fā)送和接收, 并實現接口的初始 化過程和速率的自動協商。

1 物理層功能

在發(fā)送過程中, 物理層從鏈路層接收并行的數據將其轉為串行數據, 然后以3Gbit?s -1 的線速度向硬盤側發(fā)送LVDS NRZ高速比特流。在接收過程中, 將串 行數據轉化成并行數據, 在串行數據流中檢測其中的K28.5字符, 使得輸出的并行數據對齊[4] 。 物理層提供 的具體功能如下: ( 1) 發(fā)送側和接收側提供100Ω 電阻 進行內部端接, 以此來消除反射, 保證信號的完整性。

( 2) 向鏈路層提供不同位寬的接口。

( 3) 用 CDR技術 從高速的串行比特流內恢復出時鐘和數據。

( 4)K28.5字符檢測, 以此來對齊接收到的數據。

( 5) 發(fā)送和檢測OOB( Out-Of-Band) 信號, 進行硬盤和FPGA的同步 和協商。

( 6 ) 向上層報告物理層的工作狀態(tài)。

( 7 ) 提 供電源管理功能, 以此降低功耗。

( 8 ) 支持接收和發(fā) 送阻抗匹配。

( 9) 解決擴散頻譜時鐘引起的輸入數據 頻率波動。

( 10) 響應遠端發(fā)出的測試請求。

2 OOB 信號

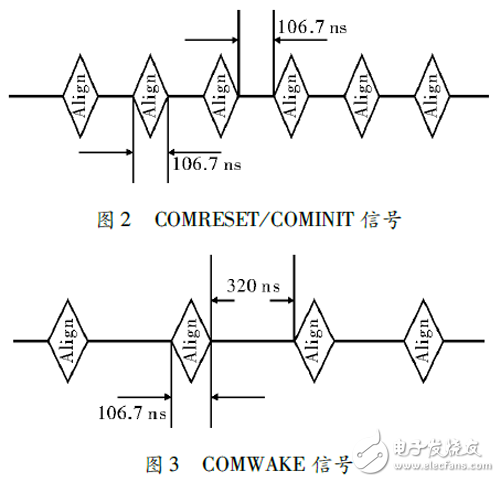

SATA 協議使用OOB信號來完成初始化過程和速 率協商過程。OOB信號不屬于數據信號, 所以稱之為 帶外信號。OOB是一種低頻信號, 具體含有3 種模 式: COMRESET、COMINIT和COMWAKE。 COMRESET, 如圖2所示, 由主機端發(fā)送, 用來設備復位和鏈 路的初始化, 其由突發(fā)長度為106.7ns 的Align 原語 和 320ns 的空閑共模電平分隔。COMINI, 如圖 2所 示, 格式與COMRESET相同, 與后者的區(qū)別在于, 其是 由設備側向主側發(fā)送的。COMWAKE, 如圖3 所示, 與 前兩者的區(qū)別在于其的空閑間隔為106.7ns, 且設備 側和主側均可以發(fā)送。

3 物理鏈路建立過程

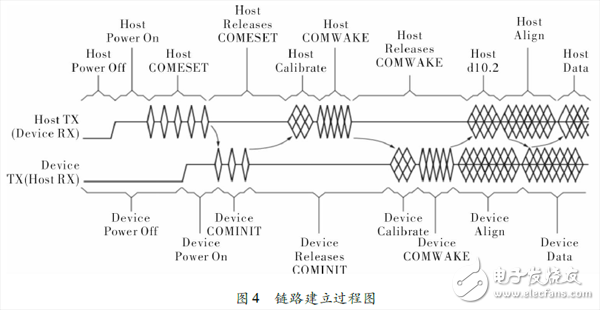

在上電和硬件復位期間, 主機通過OOB信號來建 立通行鏈路, 其中包括速度協商、時鐘恢復、阻抗校準和 自我診斷等。 具體上電過程如圖4所示, 由以下10個步驟組成:

( 1) 主側FPGA和設備側硬盤處于斷電狀態(tài)。

( 2) 系統(tǒng)上電, 主設備側將發(fā)送和接收差分對拉到共 模電壓。

( 3) 主設備側發(fā)送 COMRESET信號。

( 4) 當 上電復位結束后, 主設備側停止發(fā)送COMRESET 信號 并將 串 行 總 線 置 于 空 閑 狀 態(tài)。

( 5 ) 當硬盤檢測到COMRESET信號,其開始發(fā)送 COMINIT信號作為響應。 硬盤可在任何時間點通過發(fā)送COMINIT 信號來建立新 的 通 信 連 接。

( 6 ) 主設備側進行校準且發(fā)送COMWAKE信號。

( 7) 當硬盤在其的接收線上檢測到COMWAKE信號后, 其開始校準發(fā)送器。 完成校準后, 硬盤發(fā)送突發(fā)長度為6的COMWAKE信號然后連續(xù)發(fā) 送Align原語。 當連續(xù)發(fā)送 54.6μs的Align 原語后還 未收到來自主設備側的回應, 而硬盤側則進入錯誤狀 態(tài)。

( 8) 當主設備側檢測到COMWAKE信號后便以所 支持的最低速率開始發(fā)送D10.2字符。 于此同時, 主 設備側開始鎖定Align原語, 當準備好便以與接收到相 同的速度向硬盤側發(fā)送Align原語。 若在880μs內主 設備未接收到Align原語, 主設備便重新開始復位。

( 9) 硬盤鎖存到 Align原語序列, 并在準備就緒后, 發(fā)送SYNC原語表明可正常運行。

( 10) 當主機側接收到非Align原語, 鏈路建立完成, 則可進行正常的數據傳輸。

4 實現過程

SATA 協議物理層的實現由 3 部分組成, 分別是整體流程圖的設計、 時鐘部分和速率協商狀態(tài)轉移設計。

4.1 整體設計流程圖

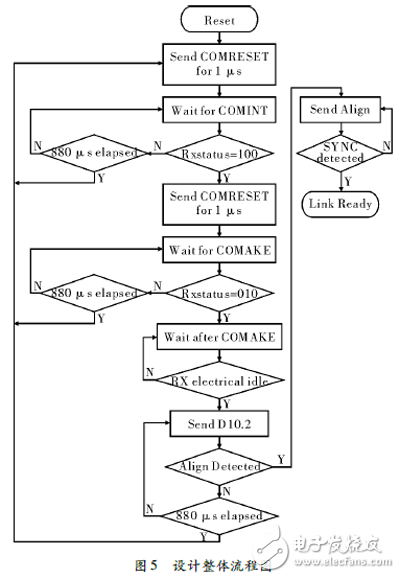

初始化的過程嚴格按照SATA 協議的規(guī)定。 整個過程流程如圖5所示。 主機端上電后首先發(fā)送持續(xù)時間為1μs 的 COMRESET 信號, 然后等待 COMINIT信號, 當SRxstatus等于100時, 再發(fā)送持續(xù)時間為1μs的COMWAKE信號。 在接收到COMWAKE信號后且線路處于 空閑的狀態(tài), 接著發(fā)送 D10.2字符。 若在 880μs 內接收 到了Align原語, 則發(fā)送Align原語且開始等待SYNC原語, 否則將重新開始發(fā)送COMRESET 信號[ 4-7] 。

4.2 時鐘控制設計

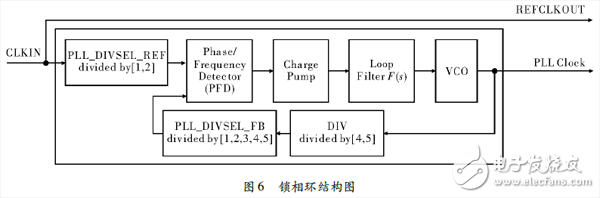

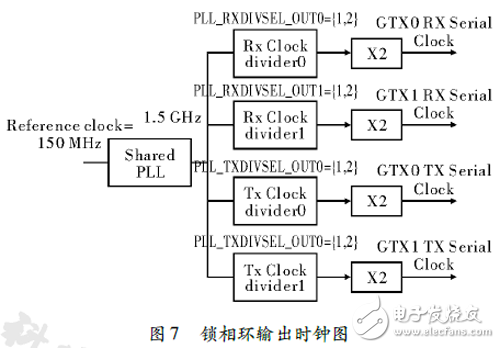

SATA 協 議 物 理 層 的 實 現 是 基 于Xilinx公 司 的FPGA, 利用FPGA內部提供的高速Serdes接口實現高 速比特流的發(fā)送、 接收和串并轉換。 其中一個高速串 行收發(fā)器GTX由兩個TILE組成, 為節(jié)省功耗, 兩個TILE由一個鎖相環(huán), 如圖6 所示提供時鐘。 由外部提 供給GTX 中鎖相環(huán)的參考時鐘頻率為 150MHz, 其中 鎖 相 環(huán) 的PLL_DIVSEL_FB參 數 設 置 為2,PLL_DIVSEL_REF參數設置為1,INTDATAWIDTH參數設 置為 1, 在 這 種 設 置 條 件 下 鎖 相 環(huán) 輸 出 的 倍 頻 時 鐘PLLCLK為1.5GHz, 如圖7所示。 該倍頻時鐘分別提 供給發(fā)送器和接收器。 提供給發(fā)送器的參考時鐘由參 數PLL_TXDIVSEL_OUT設定, 接收器則由參數PLL_RXDIVSEL_OUT 決定。 參 數PL_TXDIVSEL_OUT、

PLL_RXDIVSEL_OUT的可能取值為1和 2。 參數取值 由協商的速率決定, 可在協商的過程中通過DRP接口 動態(tài)地改變。 提供給 FPGA邏輯部分的時鐘由GTX提供給鏈路層的數據位寬決定[8-11] 。 鎖相環(huán)模塊對 外提供的接口信號如下:

( 1 )CLKIN信號用來向模塊 提供參考信號。

( 2 ) INTDATAWIDTH信號用來決定GTX串行收發(fā)器內部的數據寬度。

( 3 ) PLLDET信號 用來表示鎖相環(huán)內部的VCO壓控振蕩器的輸出范圍 是否在可接受的有效范圍內。

( 4 ) PLLDETEN信號用 來使能內部的鎖定功能。

( 5 ) REFCLKOUT頻率等于CLKIN,其可為上層的邏輯電路提供參考時鐘。

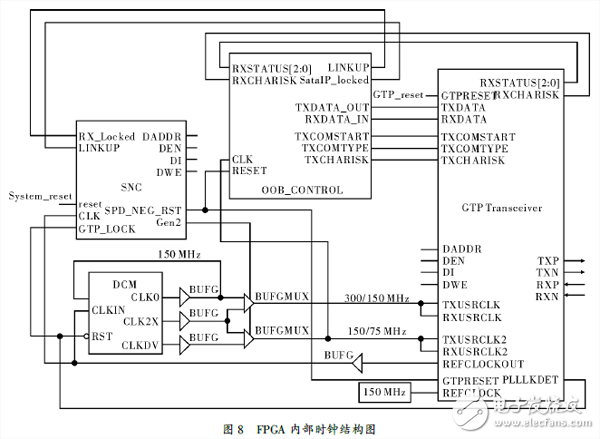

整個SATA物理的時鐘網絡結構, 如圖8 所示, 由4部分組成[8] , 分別是高速串行收發(fā)器部分OOB信號 控制部分、DCM 數字時鐘控制部分和 SNC 同步控制部 分, 其中高速串行收發(fā)器向邏輯控制部分提供 DRP動 態(tài)控制接口。GTPRESET 信號用來對整個收發(fā)器進行 全局的復位。TXDATA接口用來接收將要發(fā)送的并行 數據。 RXDATA接口用來將串并轉化后的并行數據提 供給上層。TXCOMSTART 用來指示收發(fā)器何時開始 發(fā)送 OOB信號, 并將其置 1 時開始發(fā)送OOB信號, 置0不發(fā)送OOB信號。TXCOMTYPE用來指示發(fā)送OOB信號的種類。TXCHARISK信號用來指示所發(fā)送的數據是否是K字符。 RXSTATUS 用來表示串行收發(fā)器的狀態(tài)。

REFCLKOUT時鐘信號由串行收發(fā)器模塊輸出, 經全局時鐘緩沖器BUFG進入FPGA的全局時鐘專用 網絡, 最 后 進 入DCM和SNC模 塊。 從 DCM輸 出CLK0時鐘和CLK2X時鐘, 分別通過BUFG后向收發(fā) 器提供并行的收發(fā)時鐘。SNC模塊可通過動態(tài)地改變 收發(fā)器的狀態(tài)達到速率自動協商的功能。OOB模塊 用來控制帶外信號的發(fā)送和接收。

4.3 速率協商設計

速率協商的狀態(tài)轉移過程如圖9所示。 該設計方 案可根據設備硬盤側掛載的硬盤型號, 自動的改變主FPGA這一側的線速率。 若硬盤支持I代接口, 則FPGA自動調整GTX線速率到1.5Gbit?s-1 , 若硬盤支持II代接口, 則FPGA自動調整線速率到 3Gbit?s-1 。

具體的調節(jié)過程如下:

( 1) 設備復位后, 改變接收器的線速率為3Gbit?s-1, 通過DRP動態(tài)接口讀取并修改地址為0X46寄存器的 值為 1。 ( 2) 等待 16 個時鐘周期。 ( 3 ) 改變發(fā)送器的 線速率為3Gbit?s-1, 通過DRP動態(tài)接口讀取并修改 地址為0X45 寄存器的值為1。 ( 4) 復位 OOB信號控 制模塊, 此時FPGA和硬盤進行速率協商。 ( 5) 等待鏈 接建立, 若在3.5ms時間內鏈接建立完成, 則物理層 準備好, 此時給上層一個PHYRDY的信號。 ( 6 ) 若未 建立好, 則改變接收器的線速率為1.5Gbit?s-1 。 通過DRP動態(tài)接口讀取并修改地址為0X46寄存器的值 為 0。 ( 7) 等待 16個時鐘周期。 ( 8 ) 改變發(fā)送器的線 速率為1.5Gbit?s-1 。 通過 DRP動態(tài)接口讀取并修 改地址為0X45寄存器的值為 0。 ( 9 ) 等待鏈接建立, 若3.5ms內鏈接建立, 則硬盤和主FPGA協商的速率 為1.5Gbit?s-1, 向上層報告鏈路建立可進行正常的 數據傳輸, 若未建立, 則從過程(1) 開始重新循環(huán), 直 至速率協商好為止。

5 結束語

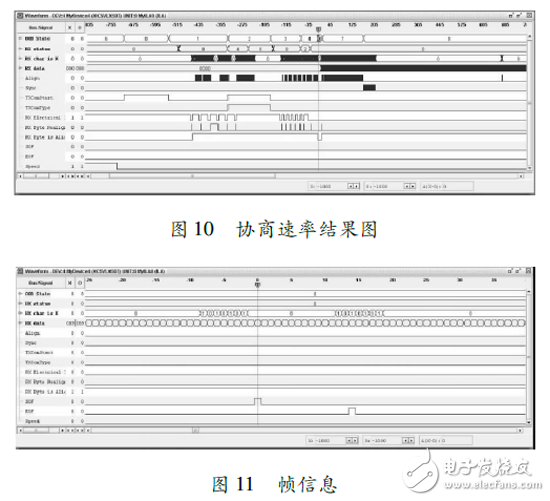

代碼調試完成后下載到Xilinx提供的ML507評 估板中, 利用 Chipscope工具抓取的波形如圖10和圖 11所示。 圖10中 speed信號為低, 表示速率協商到1.5Gbit?s-1 。 在圖11 中,SOF信號帶來一個高脈沖 后,RXDATA信號線上的數據是硬盤與FPGA建立連 接后由硬盤發(fā)送的一幀報告硬盤狀態(tài)信息的寄存器類 型幀。 幀的有效長度介于SOF的高脈沖和EOF的高 脈沖之間。 幀的長度是6個雙字, 最后4Byte為CRC校驗值, 其中所有的數據均經擾碼加擾。 從圖中可看 出,物理層完成了速率協商和鏈接建立的過程。

電子發(fā)燒友App

電子發(fā)燒友App

評論