高頻PCB設(shè)計過程中的電源噪聲的分析及對策

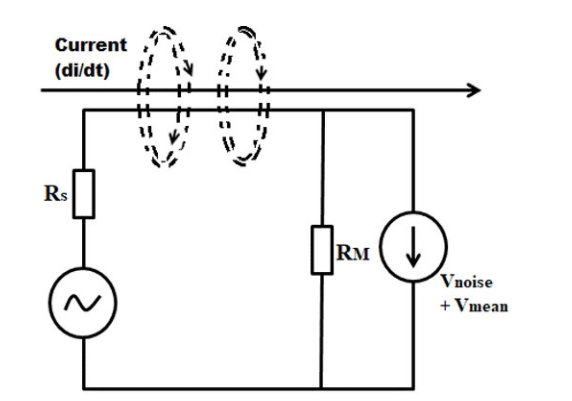

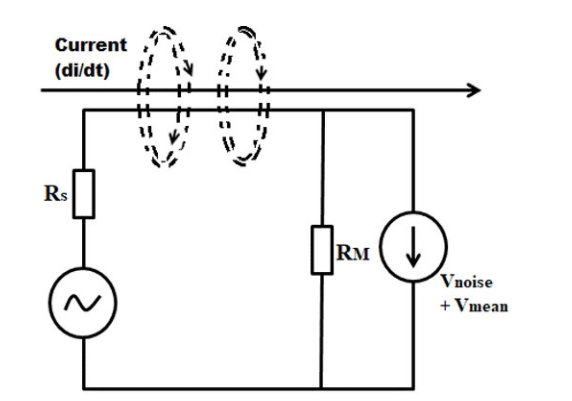

在高頻PCB板中,較重要的一類干擾便是電源噪聲。筆者通過對高頻PCB板上出現(xiàn)的電源噪聲特性和產(chǎn)生原因進行系統(tǒng)分析,并

2010-01-02 11:30:05 1001

1001

前面我們分析了EMI的產(chǎn)生情況,這節(jié)里我們將針對高速PCB設(shè)計,來分析如何進行EMI控制。

2012-03-31 11:07:14 1590

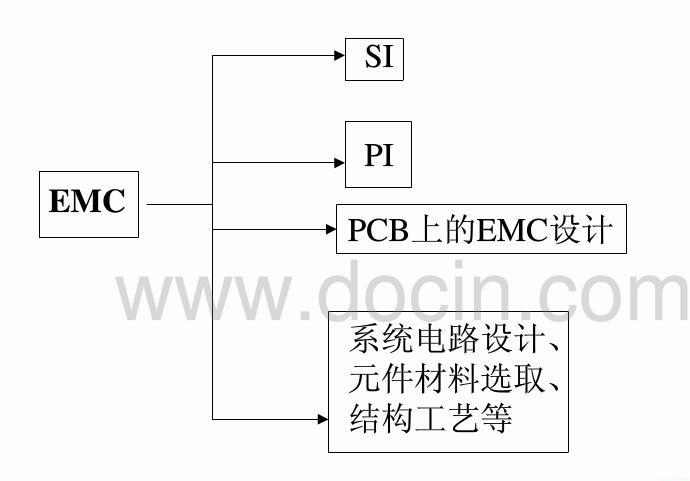

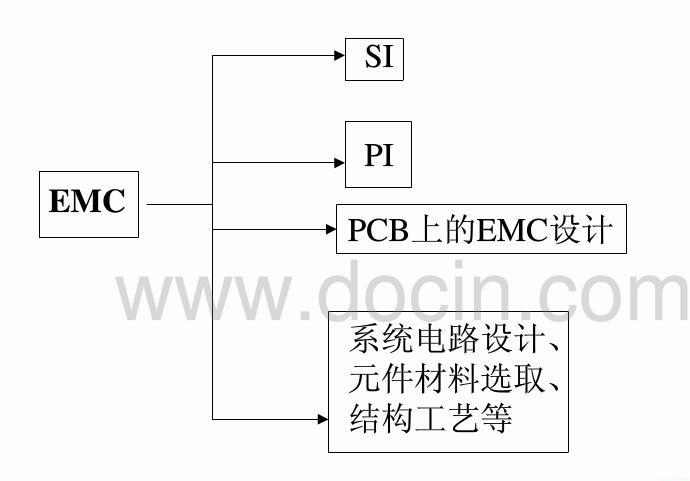

1590 隨著IC器件集成度的提高、設(shè)備的逐步小型化和器件的速度愈來愈高,電子產(chǎn)品中的EMI問題也更加嚴(yán)重。從系統(tǒng)設(shè)備EMC/EMI設(shè)計的觀點來看,在設(shè)備的PCB設(shè)計階段處理好EMC/EMI問題,是使系統(tǒng)設(shè)備達到電磁兼容標(biāo)準(zhǔn)最有效、成本最低的手段。本文介紹數(shù)字電路PCB設(shè)計中的EMI控制技術(shù)。

2022-09-19 09:27:24 1257

1257 ▼關(guān)注公眾號: 工程師看海▼ 分享一篇不錯的PCB與EMI問題文章,來自網(wǎng)絡(luò)。 電磁兼容性(EMC)及關(guān)聯(lián)的電磁干擾(EMI)歷來都需要系統(tǒng)設(shè)計工程師擦亮眼睛,在當(dāng)今電路板設(shè)計和元器件封裝不斷縮小

2023-06-14 08:46:16 1484

1484

EMC之PCB設(shè)計技巧

電磁兼容性(EMC)及關(guān)聯(lián)的電磁干擾(EMI)歷來都需要系統(tǒng)設(shè)計工程師擦亮眼睛,在當(dāng)今電路板設(shè)計和元器件封裝不斷縮小、OEM要求更高速系統(tǒng)的情況下,這兩大問題尤其令PCB布局

2023-12-19 09:53:34

的問題,是相互關(guān)聯(lián)的,如何在定義標(biāo)準(zhǔn)的過程中,平衡兩者?答:信號完整性和EMC還處于草案中不便于公開,至信號完整性和EMI兩者如何平衡,這不是測試規(guī)范的事,如果要達到二者平衡,最好是降低通信速度,但大家都不

2019-06-11 21:00:49

標(biāo)準(zhǔn)的過程中,平衡兩者?答:信號完整性和EMC還處于草案中不便于公開,至信號完整性和EMI兩者如何平衡,這不是測試規(guī)范的事,如果要達到二者平衡,最好是降低通信速度,但大家都不認(rèn)可。29、PCB設(shè)計中

2018-06-10 10:27:45

的問題,是相互關(guān)聯(lián)的,如何在定義標(biāo)準(zhǔn)的過程中,平衡兩者?答:信號完整性和EMC還處于草案中不便于公開,至信號完整性和EMI兩者如何平衡,這不是測試規(guī)范的事,如果要達到二者平衡,最好是降低通信速度,但大家都不

2015-12-17 12:50:37

)實在是威脅著電子設(shè)備的安全性、可靠性和穩(wěn)定性。我們在設(shè)計電子產(chǎn)品時,PCB板的設(shè)計對解決EMI問題至關(guān)重要。本文主要講解PCB設(shè)計時要注意的地方,從而減低PCB板中的電磁干擾問題。 電磁干擾(EMI

2018-09-17 17:37:27

本帖最后由 gk320830 于 2015-3-7 13:34 編輯

PCB過程中應(yīng)注意事項研發(fā)職員,考慮的是如何將最新的提高前輩技術(shù)集成到產(chǎn)品中。這些提高前輩技術(shù)既可以體現(xiàn)在卓越的產(chǎn)品功能上

2013-10-14 14:32:48

引言 隨著IC器件集成度的提高、設(shè)備的逐步小型化和器件的速度愈來愈高,電子產(chǎn)品中的EMI問題也更加嚴(yán)重。從系統(tǒng)設(shè)備EMC/EMI設(shè)計的觀點來看,在設(shè)備的PCB設(shè)計階段處理好EMC/EMI問題,是使

2011-11-09 20:22:16

時其結(jié)果仍然是相同的。印刷元器件技術(shù)使得從多芯片組件(MCM)和混合組件轉(zhuǎn)變到今天直接可以作為嵌入式無源元件的SiP和PCB。在轉(zhuǎn)變的過程中采用了最新的裝配技術(shù)。例如,在一個層狀結(jié)構(gòu)中包含了一個阻抗

2018-09-17 17:30:56

數(shù)年后已縮小得相當(dāng)可觀了,但在試圖獲得最大極限密度時其結(jié)果仍然是相同的。印刷元器件技術(shù)使得從多芯片組件(MCM)和混合組件轉(zhuǎn)變到今天直接可以作為嵌入式無源元件的SiP和PCB。在轉(zhuǎn)變的過程中采用

2018-11-26 17:01:07

PCB評估過程中需要關(guān)注哪些因素?對于PCB技術(shù)的文章來說,作者可闡述近段時間來PCB設(shè)計工程師們所面臨的挑戰(zhàn),因為這已成為評估PCB設(shè)計不可或缺的方面。在文章中,可以探討如何迎接這些挑戰(zhàn)及潛在

2013-08-23 14:58:01

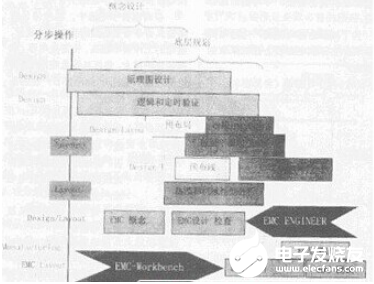

應(yīng)用就非常重要了。但目前國內(nèi)國際的普遍情況是,與IC設(shè)計相比,PCB設(shè)計過程中的EMC分析和模擬仿真是一個薄弱環(huán)節(jié)。同時,EMC仿真分析目前在PCB設(shè)計中逐漸占據(jù)越來越重要的角色。 PCB設(shè)計中的對EMC

2014-12-22 11:52:49

EMI問題是很多工程師在PCB設(shè)計遇到的最大挑戰(zhàn),由于電子產(chǎn)品信號處理頻率越來越高,EMI問題日益顯著,雖然有很多書籍對EMI問題進行了探討,但是都不夠深入,《PCB設(shè)計中EMI控制原理與實戰(zhàn)

2011-05-19 15:58:44

連續(xù)的PCB走線上傳送,電路就會出現(xiàn)功能性問題和EMI干擾,這包括電壓下降、沖擊激勵產(chǎn)生的振蕩等。在處理傳輸線效應(yīng)過程中,線路阻抗影響著產(chǎn)品的最終性能,當(dāng)且僅當(dāng)電路終接的負載等于線路的特性阻抗時,在

2012-11-05 13:30:04

PCB設(shè)計過程中布線效率的提升方法現(xiàn)在市面上流行的EDA工具軟件很多,但這些pcb設(shè)計軟件除了使用的術(shù)語和功能鍵的位置不一樣外都大同小異,如何用這些工具更好地實現(xiàn)PCB的設(shè)計呢?在開始布線之前

2018-07-09 17:23:05

PCB設(shè)計應(yīng)遵循什么原則?PCB布線的原則是什么?

2021-04-23 06:32:10

,不可避免地會引入EMC(電磁兼容)和EMI(電磁干擾)的問題,所以對電子產(chǎn)品的電磁兼容分析顯得特別重要。與IC設(shè)計相比,PCB設(shè)計過程中的EMC分析和模擬仿真是一個薄弱環(huán)節(jié)。

2019-07-22 06:45:44

鏈接。FPGA/PCB集成的目的是為了提供雙向集成、數(shù)據(jù)治理和在FPGA與PCB之間執(zhí)行協(xié)同設(shè)計的能力。 在布局階段輸入了與設(shè)計定義期間相同的用于物理實現(xiàn)的約束規(guī)則。這就減少了從文件到布局過程中犯錯

2018-09-13 15:49:39

而非EMC專長的我們來說,其實也只能回答個大概,實話實說,在EMC領(lǐng)域我們也還在不斷的學(xué)習(xí)中,所以這篇文章也只是基于我們對EMC 的一些認(rèn)識,從PCB 設(shè)計中如何去盡量的避免問題的發(fā)生,其中說得

2016-07-29 18:37:23

(電磁兼容)和EMI(電磁干擾)的問題,所以對電子產(chǎn)品的電磁兼容分析顯得特別重要。與IC設(shè)計相比,PCB設(shè)計過程中的EMC分析和模擬仿真是一個薄弱環(huán)節(jié)。

2019-06-21 06:28:33

通常,仿真軟件對于EMC/EMI類問題工程問題的處理過程為“建模->復(fù)現(xiàn)問題->改進設(shè)計”。然而,EMC/EMI問題具有隨機性和多變性的特點,因此,完整的“復(fù)現(xiàn)”一個實際工程中的EMC

2019-05-30 06:14:27

現(xiàn)在在畫PCB,新手,希望能和各大高手多多交流學(xué)習(xí),這是我在網(wǎng)上找的關(guān)于EMC/EMI的一些經(jīng),和大家分享一下,不足的地方希望大家補充。

2015-04-19 21:45:29

不影響同一環(huán)境中其他設(shè)備按預(yù)期運行的能力。評估設(shè)備在暴露于電磁能時如何反應(yīng)是其中的一個組成部分,稱為免疫(或敏感性)測試。測量設(shè)備內(nèi)部電氣系統(tǒng)產(chǎn)生的EMI量 - 另一種稱為排放測試的過程。 EMC

2021-08-20 17:11:57

EMI進行預(yù)測,定位開關(guān)電源傳導(dǎo)EMI傳播路徑的影響因素,在此基礎(chǔ)上給出開關(guān)電源PCB及其結(jié)構(gòu)設(shè)計的基本原則。對開關(guān)電源EMI預(yù)測過程中需要注意的問題以及降低開關(guān)電源傳導(dǎo)EMI的方法策略進行了分析

2016-05-04 14:03:26

EMI進行預(yù)測,定位開關(guān)電源傳導(dǎo)EMI傳播路徑的影響因素,在此基礎(chǔ)上給出開關(guān)電源PCB及其結(jié)構(gòu)設(shè)計的基本原則。對開關(guān)電源EMI預(yù)測過程中需要注意的問題以及降低開關(guān)電源傳導(dǎo)EMI的方法策略進行了分析和總結(jié)

2016-04-20 16:25:31

如何在高速PCB的設(shè)計過程中對EMI進行有效的控制呢?本文就將從傳輸線參數(shù)的角度來為大家進行分析。傳輸線RLC參數(shù)和EMI對于PCB板來說,PCB上的每一條走線都可以有用三個基本的分布參數(shù)來對它進行描述

2016-07-20 16:58:54

%-50%的成功率。本次給大家介紹在PCB設(shè)計過程中電源平面處理應(yīng)該考慮的基本要素。1、做電源處理時,首先應(yīng)該考慮的是其載流能力,其中包含 2 個方面。a)電源線寬或銅皮的...

2021-12-28 06:21:13

電源平面的處理,在PCB設(shè)計中占有很重要的地位。在一個完整的設(shè)計項目中,通常電源的處理情況能決定此次項目30%-50%的成功率,本次給大家介紹在PCB設(shè)計過程中電源平面處理應(yīng)該考慮的基本要素。 1

2021-12-31 07:17:08

引言 隨著IC器件集成度的提高、設(shè)備的逐步小型化和器件的速度愈來愈高,電子產(chǎn)品中的EMI問題也更加嚴(yán)重。從系統(tǒng)設(shè)備EMC/EMI設(shè)計的觀點來看,在設(shè)備的PCB設(shè)計階段處理好EMC/EMI問題,是使

2019-09-16 22:37:29

、目前市場上也很難找到高級的PCB設(shè)計工程師。從普通的工程師培育到高級PCB設(shè)計人才,至少需求2-3年的的時間,而且在培養(yǎng)的過程中,也很難避免人才的流失,陷入為他人做嫁衣的尷尬局面。 5、出于成本的考慮

2020-06-23 15:43:12

在PCB設(shè)計過程中,把PCB拉到最下面,現(xiàn)在不能整體弄不上來了?請問是什么原因?怎么解決呢?

2015-11-28 19:41:03

在PCB設(shè)計中,電磁兼容性(EMC)及關(guān)聯(lián)的電磁干擾(EMI)歷來是讓工程師們頭疼的兩大問題,特別是在當(dāng)今電路板設(shè)計和元器件封裝不斷縮小、OEM要求更高速系統(tǒng)的情況下。本文給大家分享如何在PCB設(shè)計中避免出現(xiàn)電磁問題。

2021-02-01 07:42:30

如何在PCB設(shè)計階段處理好EMC及其EMI的問題呢?有什么解決辦法嗎?

2023-04-06 15:52:59

在高速PCB設(shè)計時為了防止反射就要考慮阻抗匹配,但由于PCB的加工工藝限制了阻抗的連續(xù)性而仿真又仿不到,在原理圖的設(shè)計時怎樣來考慮這個問題?另外關(guān)于IBIS模型,不知在那里能提供比較準(zhǔn)確的IBIS

2012-03-03 12:41:55

PCB及其結(jié)構(gòu)設(shè)計的基本原則。對開關(guān)電源EMI預(yù)測過程中需要注意的問題以及降低開關(guān)電源傳導(dǎo)EMI的方法策略進行了分析和總結(jié)。

2023-09-22 07:18:09

一個(如果不是這樣的話),確保板元件之間足夠間隙的主要原因是: 阻焊劑。這是一項基本的制造任務(wù),可以保護您的電路板并幫助隔離必須在焊接過程中焊接的電氣連接。印刷電路板。PCB設(shè)計步驟5:盡可能避免

2020-10-27 15:25:27

引言 隨著IC 器件集成度的提高、設(shè)備的逐步小型化和器件的速度愈來愈高,電子產(chǎn)品中的EMI問題也更加嚴(yán)重。從系統(tǒng)設(shè)備EMC /EMI設(shè)計的觀點來看,在設(shè)備的PCB設(shè)計階段處理好EMC/EMI

2018-09-14 16:32:58

布線技術(shù)實現(xiàn)信號串?dāng)_控制的設(shè)計策略EMC的PCB設(shè)計技術(shù)CADENCE PCB設(shè)計技術(shù)方案基于高速FPGA的PCB設(shè)計技術(shù)解析高速PCB設(shè)計中的時序分析及仿真策略闡述基于Proteus軟件的單片機仿真

2014-12-16 13:55:37

越來越高,不可避免地會引入EMC和EMI的問題,所以對電子產(chǎn)品的電磁兼容分析顯得特別重要。與IC設(shè)計相比,PCB設(shè)計過程中的EMC分析和模擬仿真是一個薄弱環(huán)節(jié)。

2009-10-12 15:55:33

。 EMC包括EMI(電磁干擾)及EMS(電磁耐受性)兩部份,所謂EMI電磁干擾,乃為機器本身在執(zhí)行應(yīng)有功能的過程中所產(chǎn)生不利于其它系統(tǒng)的電磁噪聲;而EMS乃指機器在執(zhí)行應(yīng)有功能的過程中不受周圍電磁環(huán)境

2016-01-19 09:32:14

PCB設(shè)計面臨的挑戰(zhàn)有哪些?在PCB評估過程中需要關(guān)注哪些因素?

2021-04-26 06:51:27

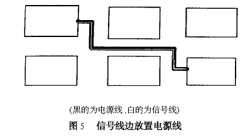

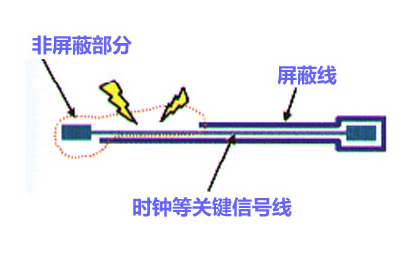

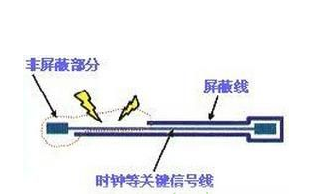

,很多PCB LAYOUT工程師在走線的過程中,很容易出現(xiàn)一種失誤,即時鐘信號等高速信號網(wǎng)絡(luò),在多層的PCB走線的時候產(chǎn)生了閉環(huán)的結(jié)果,這樣的閉環(huán)結(jié)果將產(chǎn)生環(huán)形天線,增加EMI的輻射強度。規(guī)則三:高速

2017-11-02 12:11:12

在pcb設(shè)計過程中,電源分配方式有兩種:總線方式和電源層方式,誰能告訴我這兩種方式的具體含義嗎?

2019-08-05 23:00:18

塊PCB傳到另一塊PCB能不能正確接收?這在前期就要評估,而評估這個問題其實并不是很難,懂一點信號完整性知識,會一點簡單的軟件操作就能做到。第2、在PCB設(shè)計過程中,使用仿真軟件評估具體走線,觀察信號

2014-12-22 11:22:13

從一塊PCB傳到另一塊PCB能不能正確接收?這在前期就要評估,而評估這個問題其實并不是很難,懂一點信號完整性知識,會一點簡單的軟件操作就能做到。第2、在PCB設(shè)計過程中,使用仿真軟件評估具體走線,觀察

2017-01-11 10:14:04

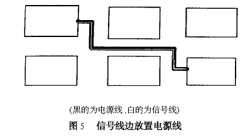

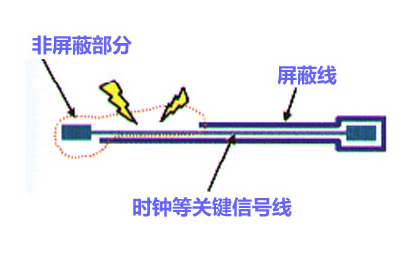

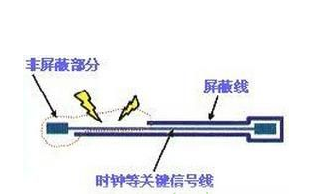

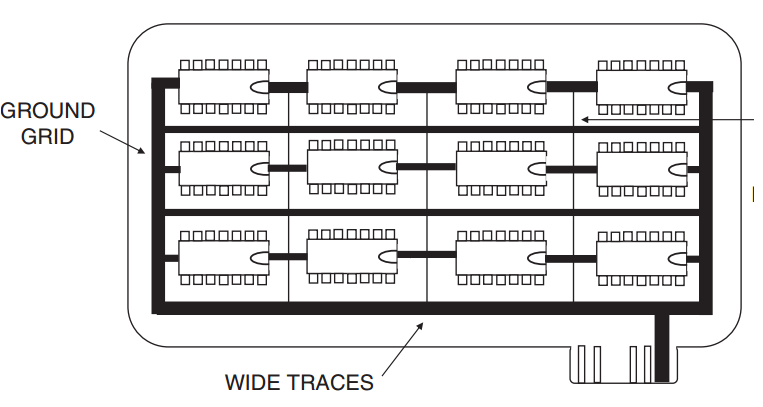

規(guī)則一:高速信號走線屏蔽規(guī)則 在高速的PCB設(shè)計中,時鐘等關(guān)鍵的高速信號線,走線需要進行屏蔽處理,如果沒有屏蔽或只屏蔽了部分,都會造成EMI的泄漏。建議屏蔽線,每1000mil,打孔接地

2016-01-19 22:50:31

、DSP系統(tǒng)的降噪技術(shù)2、POWERPCB在PCB設(shè)計中的應(yīng)用技術(shù)3、PCB互連設(shè)計過程中最大程度降低RF效應(yīng)的基本方法六、1、混合信號電路板的設(shè)計準(zhǔn)則2、分區(qū)設(shè)計3、RF產(chǎn)品設(shè)計過程中降低信號耦合

2012-07-13 16:18:40

本文針對高頻電路在PCB設(shè)計過程中的布局、布線兩個方面,以Protel 99SE軟件為例,來探討一下高頻電路在PCB 設(shè)計過程中的對策及設(shè)計技巧。

2021-04-25 07:36:27

華為的EMC設(shè)計資料:本書對PCB的EMC設(shè)計現(xiàn)有成果加以總結(jié),推廣,同時對一些未知的領(lǐng)域進行積極的探索。結(jié)合PCB設(shè)計過程中的經(jīng)驗教訓(xùn)以及產(chǎn)品的EMC測試數(shù)據(jù)。

2010-02-24 09:33:57 0

0 華為pcb的emc設(shè)計指南:本書對PCB的EMC設(shè)計現(xiàn)有成果加以總結(jié),推廣,同時對一些未知的領(lǐng)域進行積極的探索。結(jié)合PCB設(shè)計過程中的經(jīng)驗教訓(xùn)以及產(chǎn)品的EMC測試數(shù)據(jù)。

2010-02-24 09:34:38 0

0 高速PCB設(shè)計時應(yīng)從哪些方面考慮EMC、EMI的規(guī)則

一般EMI/EMC 設(shè)計時需要同時考慮輻射(radiated)與傳導(dǎo)(conducted)兩個方面,前者歸屬于頻率較高的

2009-03-20 14:05:36 1360

1360 關(guān)于PCB 生產(chǎn)過程中銅面防氧化的一些探討

摘要:本文主要論述了在PCB 生產(chǎn)過程中對銅面氧化的防范手段,探討引用一種新

2009-11-17 08:52:35 3476

3476 PCB設(shè)計考慮EMC的接地技巧

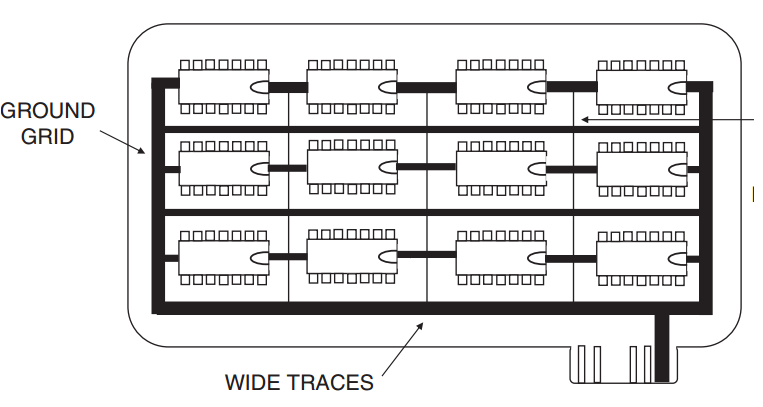

PCB設(shè)計中,接地是抑制噪聲和防止干擾的重要措施。根據(jù)電路的不同,有不同的接地方法,只有正確

2009-11-17 09:10:49 1326

1326 為了保證設(shè)計的PCB板具有高質(zhì)量和高可靠性,設(shè)計者通常要對PCB板進行熱溫分析,機械可靠性分析,與IC設(shè)計相比,PCB設(shè)計過程中的EMC分析和模擬仿真是一個薄弱環(huán)節(jié)

2011-04-29 11:51:25 2044

2044

PCB設(shè)計對EMC的改善是:在布線之前,先研究好回流路徑的設(shè)計方案,就有最好的成功機會,可以達成降低EMI輻射的目標(biāo)。而且在還沒有動手實際布線之前,變更布線層等都不必花費任何

2011-08-27 00:57:14 7728

7728

在pcb layout中EMC占有相當(dāng)?shù)牡匚唬粋€好的pcb設(shè)計工程師應(yīng)該掌握足夠的EMC的知識。產(chǎn)品必須要經(jīng)過3C, FCC, CE認(rèn)證這也是早被人們所孰知。

2011-11-23 10:23:00 2606

2606

EMC整改及PCB設(shè)計(培訓(xùn)資料),希望對你有幫助

2016-03-01 17:56:26 0

0 pcb設(shè)計考慮emc的接地技巧,有需要的下來看看。

2016-03-29 16:39:18 41

41 PCB板EMC--EMI-的設(shè)計技巧,感興趣的小伙伴們可以看看。

2016-08-19 17:04:53 0

0 如何快速解決PCB設(shè)計EMI問題

2017-01-14 12:48:43 0

0 應(yīng)用就非常重要了。但目前國內(nèi)國際的普遍情況是,與IC設(shè)計相比,PCB設(shè)計過程中的EMC分析和模擬仿真是一個薄弱環(huán)節(jié)。同時,EMC仿真分析目前在PCB設(shè)計中逐漸占據(jù)越來越重要的角色。 PCB設(shè)計中的對EMC/EMI的分析目標(biāo)信號完整性分析包括同一布線網(wǎng)絡(luò)上同一信

2017-12-04 11:39:11 0

0 本文主要介紹了高速PCB的EMC設(shè)計原則,首先介紹了PCB設(shè)計的EMC基礎(chǔ)知識,其次闡述了PCB中EMC設(shè)計的重要性以及PCB中EMC設(shè)計相關(guān)項,最后詳細的介紹了關(guān)于高速PCB的EMC設(shè)計的47項原則,具體的跟隨小編一起來了解一下。

2018-05-25 15:58:19 4665

4665

由于PCB板上的電子器件密度越來越大,走線越來越窄,信號的頻率越來越高,不可避免地會引入EMC(電磁兼容)和EMI(電磁干擾)的問題,所以對電子產(chǎn)品的電磁兼容分析顯得特別重要。與IC設(shè)計相比,PCB設(shè)計過程中的EMC分析和模擬仿真是一個薄弱環(huán)節(jié)。

2018-08-05 09:45:52 2074

2074 隨著IC器件集成度的提高、設(shè)備的逐步小型化和器件的速度愈來愈高,電子產(chǎn)品中的EMI問題也更加嚴(yán)重。從系統(tǒng)設(shè)備EMC/EMI設(shè)計的觀點來看,在設(shè)備的PCB設(shè)計階段處理好EMC/EMI問題,是使系統(tǒng)設(shè)備達到電磁兼容標(biāo)準(zhǔn)最有效、成本最低的手段。本文介紹數(shù)字電路PCB設(shè)計中的EMI控制技術(shù)。

2018-08-25 09:08:00 1820

1820

(電磁兼容)和EMI(電磁干擾)的問題,所以對電子產(chǎn)品的電磁兼容分析顯得特別重要。與IC設(shè)計相比,PCB設(shè)計過程中的EMC分析和模擬仿真是一個薄弱環(huán)節(jié)。

2018-11-13 15:02:00 1284

1284 應(yīng)用就非常重要了。但目前國內(nèi)國際的普遍情況是,與IC設(shè)計相比,PCB設(shè)計過程中的EMC分析和模擬仿真是一個薄弱環(huán)節(jié)。同時,EMC仿真分析目前在PCB設(shè)計中逐漸占據(jù)越來越重要的角色。

2018-10-16 10:18:00 2737

2737 做pcb設(shè)計過程中,在走線之前,一般我們會對自己要進行設(shè)計的項目進行疊層,根據(jù)厚度、基材、層數(shù)等信息進行計算阻抗,計算完后一般可得到如下內(nèi)容。

2019-03-16 09:04:03 8234

8234

EMC/EMI的仿真需要用到仿真模型EMC/EMI分析要了解所用到的元器件的電氣特性,之后才能更好地具體模擬仿真。目前應(yīng)用較多的有IBIS和SPICE模型。IBIS(I/O Buffer

2019-06-28 15:27:22 1635

1635

高頻而忽略低頻的部分。 一個好的EMI/EMC設(shè)計必須一開始布局時就要考慮到器件的位置, PCB迭層的安排, 重要聯(lián)機的走法, 器件的選擇等, 如果這些沒有事前有較佳的安排, 事后解決則會事倍功半, 增加成本。

2019-06-25 15:43:07 1035

1035 在PCB設(shè)計中,EMC/EMI主要分析布線網(wǎng)絡(luò)本身的信號完整性,實際布線網(wǎng)絡(luò)可能產(chǎn)生的電磁輻射和電磁干擾以及電路板本身抵抗外部電磁干擾的能力,并且依據(jù)設(shè)計者的要求提出布局和布線時抑制電磁輻射和干擾

2019-05-31 15:03:10 1474

1474 在PCB設(shè)計過程中,使用仿真軟件評估具體走線,觀察信號質(zhì)量能不能滿足要求,這個仿真過程本身非常簡單,關(guān)鍵是要理解信號完整性的原理知識,并用來指導(dǎo)。

2019-08-15 10:58:00 1037

1037 高速PCB設(shè)計EMI有什么規(guī)則

2019-08-21 14:38:03 807

807

EMC/EMI的仿真需要用到仿真模型EMC/EMI分析要了解所用到的元器件的電氣特性,之后才能更好地具體模擬仿真。目前應(yīng)用較多的有IBIS和SPICE模型。IBIS(I/O Buffer

2019-09-27 15:09:34 1552

1552 (電磁兼容)和EMI(電磁干擾)的問題,所以對電子產(chǎn)品的電磁兼容分析顯得特別重要。與IC設(shè)計相比,PCB設(shè)計過程中的EMC分析和模擬仿真是一個薄弱環(huán)節(jié)。

2020-01-24 17:00:00 954

954

低EMI DC/DC變換器PCB設(shè)計

2020-02-04 15:26:08 3835

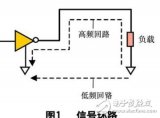

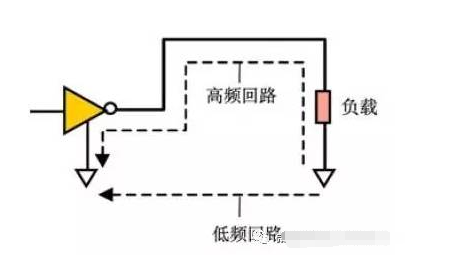

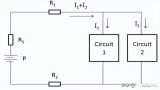

3835 在PCB設(shè)計過程中,由于平面的分割,可能會導(dǎo)致信號參考平面不連續(xù),對于低低頻信號,可能沒什么關(guān)系,而在高頻數(shù)字系統(tǒng)中,高頻信號以參考平面作返回路徑,即回流路徑,如果參考?面不連續(xù),信號跨分割,這就會帶來諸多的問題,如EMI、串?dāng)_等問題。

2020-03-11 15:00:24 1909

1909 隨著信號上升沿時間的減小,信號頻率的提高,電子產(chǎn)品的EMI問題,也來越受到電子工程師的重視。高速pcb設(shè)計的成功,對EMI的貢獻越來越受到重視,幾乎60%的EMI問題可以通過高速PCB來控制解決。

2020-03-25 15:55:28 1400

1400

PCB設(shè)計布局被認(rèn)為是促進EMI在電路中傳播的主要問題之一。這就是為什么在開關(guān)電源中降低EMI的普遍而通用的技術(shù)之一是布局優(yōu)化。

2021-01-28 10:58:06 2089

2089

“隨著IC器件集成度的提高、設(shè)備的逐步小型化和器件的速度愈來愈高,電子產(chǎn)品中的EMI問題也更加嚴(yán)重。從系統(tǒng)設(shè)備EMC/EMI設(shè)計的觀點來看,在設(shè)備的PCB設(shè)計階段處理好EMC/EMI問題,是使系統(tǒng)設(shè)備達到電磁兼容標(biāo)準(zhǔn)最有效、成本最低的手段。

2020-11-10 10:47:11 1714

1714

設(shè)計具有良好EMC性能的電路的關(guān)鍵要素之一是PCB設(shè)計。好的PCB設(shè)計可使電路板在其EMC性能方面表現(xiàn)良好。

2021-01-06 11:19:16 2705

2705

PCB設(shè)計之在真實世界里的EMI控制說明。

2021-06-23 14:53:34 0

0 高性能PCB的SI/PI和EMI/EMC仿真設(shè)計

2021-12-30 10:58:12 31

31 PCB設(shè)計中的EMC設(shè)計指南免費下載。

2022-02-16 14:02:06 42

42 本書旨在對我司PCB的EMC設(shè)計現(xiàn)有成果加以總結(jié)、推廣,同時對- -些未知的領(lǐng)域進行積極的探索。結(jié)合我司PCB設(shè)計過程中的經(jīng)驗教訓(xùn)以及產(chǎn)品的EMC測試數(shù)據(jù),我們PCB的EMC設(shè)計進行了較系統(tǒng)的總結(jié),謹(jǐn)供各硬件工程師進行PCB的EMC設(shè)計時參考。

2022-06-06 10:45:04 0

0 此應(yīng)用筆記的主旨是為硬件和/或PCB設(shè)計者在PCB設(shè)計過程中提供改善EMC的基本知識。由于詳

細的介紹這些設(shè)計規(guī)則將超過本應(yīng)用筆記負荷,所以此筆記解釋了大部分設(shè)計規(guī)則的基本知識。在市場

2022-09-09 16:18:35 22

22 何為EMC整改?EMC整改就是指產(chǎn)品在功能調(diào)試或EMC測試過程中出現(xiàn)問題后所采取的彌補手段。首先我們從EMC認(rèn)證測試項目說起,EMC認(rèn)證測試主要包含兩大項:EMI(干擾)和EMS(產(chǎn)品抗干擾和敏感度

2023-02-13 11:50:37 873

873

今天主要是關(guān)于: EMC,PCB設(shè)計中如何降低EMC? 一、EMC是什么? 在PCB設(shè)計中,主要的EMC問題包括3種: 傳導(dǎo)干擾 、 串?dāng)_干擾 、 輻射干擾。 1、傳導(dǎo)干擾 傳導(dǎo)干擾 通過 引線

2023-07-26 19:40:01 824

824

深圳PCB制造廠家與您分享PCB設(shè)計中的EMC問題與哪些因素有關(guān)? PCB設(shè)計中與EMC問題有關(guān)的因素 1.系統(tǒng)設(shè)計: 在進行系統(tǒng)級EMC設(shè)計時,首先要確定EMI干擾源,以便逐步更好地屏蔽EMI輻射源。 2.結(jié)構(gòu)影響: 非金屬機箱輻射騷擾發(fā)射超標(biāo),應(yīng)采取導(dǎo)電噴涂、局部屏蔽設(shè)計、電纜屏蔽

2023-09-06 09:30:05 610

610 考慮EMC的PCB設(shè)計

2022-12-30 09:22:03 15

15 在PCB設(shè)計中,EMC/EMI主要分析布線網(wǎng)絡(luò)本身的信號完整性,實際布線網(wǎng)絡(luò)可能產(chǎn)生的電磁輻射和電磁干擾以及電路板本身抵抗外部電磁干擾的能力,并且依據(jù)設(shè)計者的要求提出布局和布線時抑制電磁輻射和干擾的規(guī)則,作為整個PCB設(shè)計過程的指導(dǎo)原則。

2023-12-15 16:31:42 160

160

電子發(fā)燒友App

電子發(fā)燒友App

評論