引言

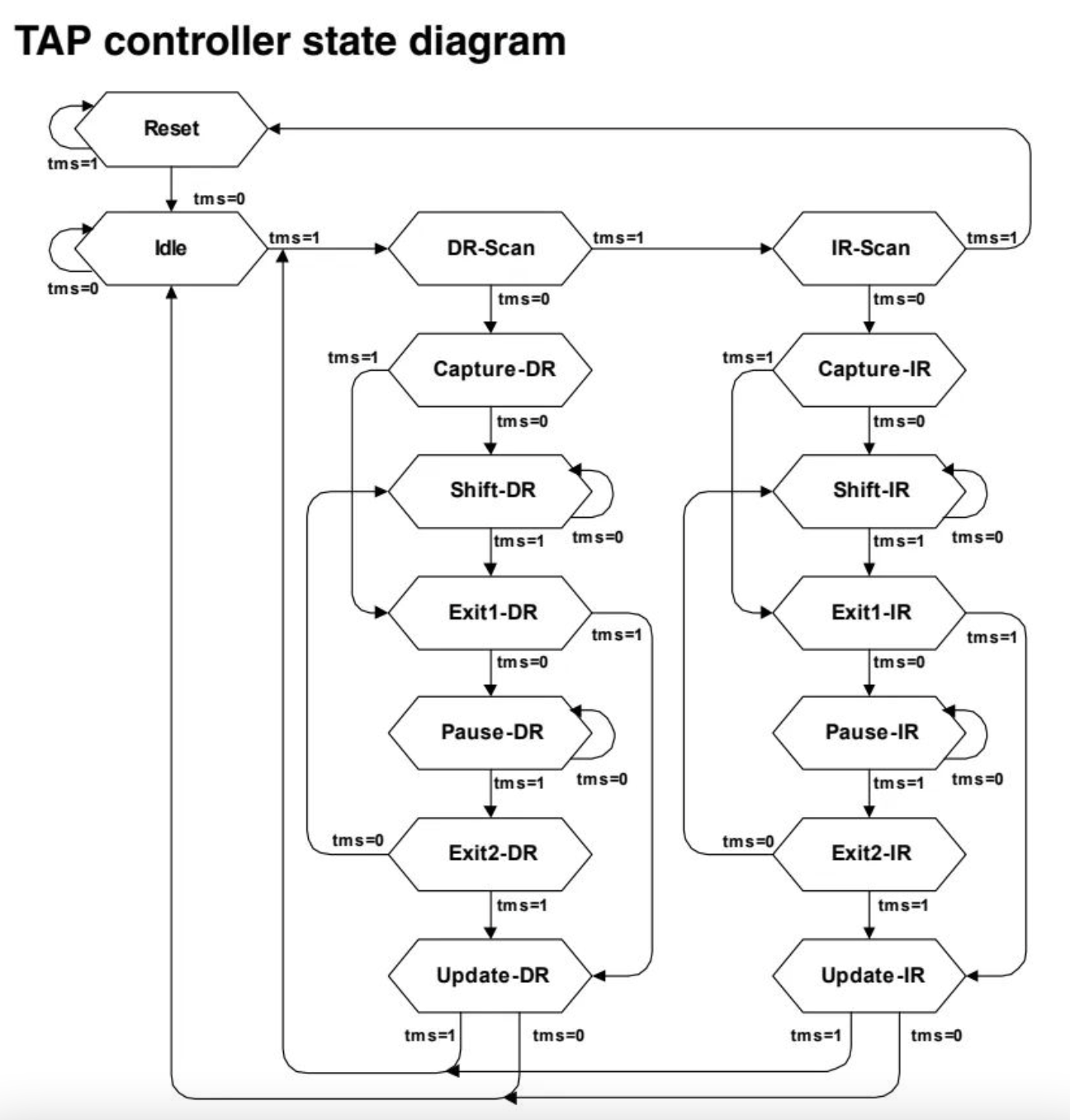

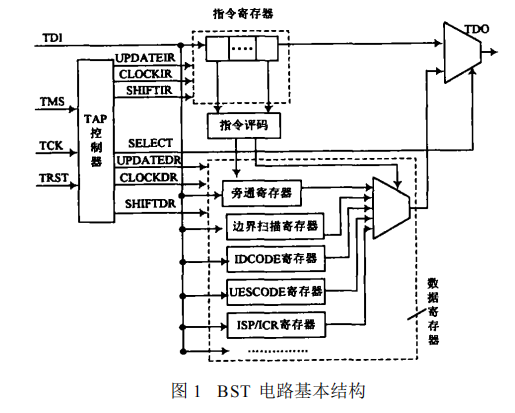

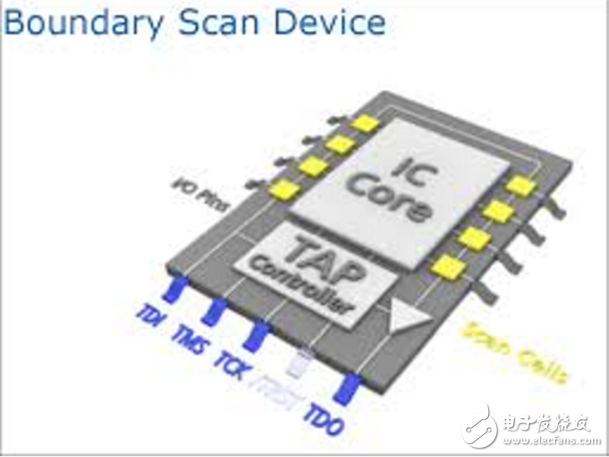

電子器件的生產(chǎn)商和電子產(chǎn)品的制造商都在傾向于采用最新的器件技術(shù),如BGA、CSP(芯片規(guī)模封裝)、TCP(倒裝芯片封裝)和其它更小的封裝,以提供更強(qiáng)的功能、更小的體積,并節(jié)省成本。電路板越來越密、器件越來越復(fù)雜、電路性能要求越來越苛刻,越來越難的接入問題導(dǎo)致了工業(yè)標(biāo)準(zhǔn)IEEE 1149.1——邊界掃描的誕生。邊界掃描測(cè)試BST是一種可測(cè)試結(jié)構(gòu)技術(shù),它是在芯片的I/O端上增加移位寄存器,把這些寄存器連接起來,加上時(shí)鐘復(fù)位、測(cè)試方式選擇以及掃描輸入和輸出端口,而形成邊界掃描通道。每個(gè)IEEE 1149.1兼容的器件,都包括一個(gè)4線或5線的測(cè)試端口(TAP)、一個(gè)狀態(tài)機(jī)(TAP控制器)和由邊界掃描單元構(gòu)成的邊界掃描移位寄存器。其中TAP控制器用于控制邊界掃描測(cè)試的執(zhí)行。邊界掃描描述語言(BSDL-Boundary-Scan Description Language)是VHDL語言的子集。測(cè)試軟件開發(fā)系統(tǒng)使用BSDL文件進(jìn)行測(cè)試生成、分析、故障診斷和在系統(tǒng)編程。

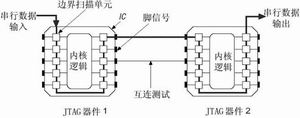

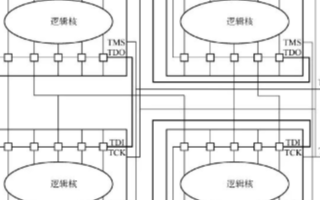

圖1 邊界掃描用于互連線測(cè)試

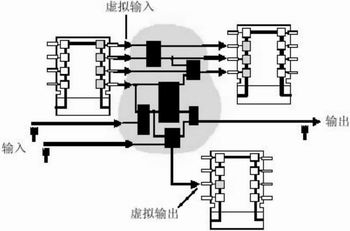

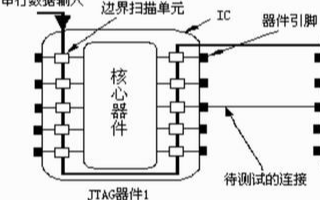

圖2 集群測(cè)試

邊界掃描在板級(jí)測(cè)試中的應(yīng)用

邊界掃描在板級(jí)測(cè)試中,主要是對(duì)PCB上器件間互連線和管腳的故障進(jìn)行檢測(cè)和隔離,對(duì)在系統(tǒng)編程器件進(jìn)行編程。測(cè)試邊界掃描板的通用測(cè)試策略是:

?執(zhí)行板級(jí)邊界掃描基本結(jié)構(gòu)完整性測(cè)試。

?使用Extest指令,施加激勵(lì)和檢測(cè)響應(yīng),進(jìn)行邊界掃描器件間互連的測(cè)試,測(cè)試時(shí)將非邊界掃描器件設(shè)置到安全狀態(tài)。

?對(duì)非邊界掃描器件進(jìn)行測(cè)試,如集群測(cè)試、RAM測(cè)試等。

在正常工作模式,帶邊界掃描功能的IC好像沒有實(shí)現(xiàn)其特定功能。然而,當(dāng)要進(jìn)行測(cè)試或在系統(tǒng)編程時(shí),器件的掃描邏輯被激活,通過菊花鏈將多個(gè)具有JTAG接口的器件串聯(lián)起來,組成一個(gè)掃描鏈,使用單組測(cè)試向量實(shí)現(xiàn)對(duì)整個(gè)電路板的完整測(cè)試,如圖1所示。

邊界掃描測(cè)試對(duì)于采用復(fù)雜表面貼裝技術(shù)的電路板功能測(cè)試也是一種較好選擇,它能快速剔除產(chǎn)品的制造故障,讓功能測(cè)試真正進(jìn)行功能性故障的查找。當(dāng)前的主流在線測(cè)試和飛針測(cè)試設(shè)備也都兼有邊界掃描測(cè)試功能。

盡管很多使用中的器件可以使用BST技術(shù),但仍有部分電路沒有邊界掃描功能。Teradyne公司的邊界掃描測(cè)試軟件VICTORY,可在其在線測(cè)試ATE上運(yùn)行,其中模塊VCCT (Virtual Component and Cluster Test 虛擬器件和集群測(cè)試)的工作原理是:VCCT將邊界掃描器件的掃描單元作為一個(gè)虛擬的ATE測(cè)試通道,去驅(qū)動(dòng)激勵(lì)非邊界掃描邏輯電路,然后測(cè)試響應(yīng)。VCCT可以組合虛擬通道和真實(shí)的ATE通道進(jìn)行驅(qū)動(dòng)和檢測(cè)。用VCCT進(jìn)行單個(gè)器件或集群(Cluster)測(cè)試時(shí),關(guān)鍵的任務(wù)是定義測(cè)試目標(biāo)的輸入和輸出,如圖2所示。

JTAG接口在FPGA中的應(yīng)用

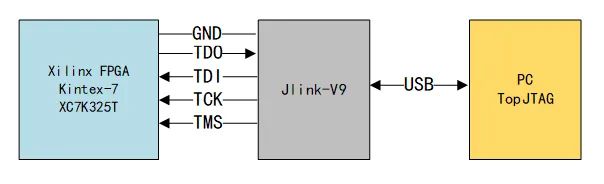

FPGA中的JTAG接口,除支持邊界掃描測(cè)試外,還具有在系統(tǒng)編程(ISP)和邏輯分析功能(SignalTap)。

ISC和ISP

ISC(在系統(tǒng)配置)或ISP是IEEE 1149.1的主要新應(yīng)用。如Altera公司的MAX7000系列EPLD就具有在系統(tǒng)編程功能,可用在線測(cè)試設(shè)備(ICT)或下載電纜,通過JTAG接口在板級(jí)對(duì)可編程器件進(jìn)行在線測(cè)試和編程,簡(jiǎn)化制造流程。

SignalTap

在Altera公司的Stratix、Excalibur、APEX II等器件中,通過JTAG接口,實(shí)現(xiàn)了SignalTap II嵌入式邏輯分析儀功能。SignalTap II是二次生成(second-generation)的系統(tǒng)級(jí)調(diào)試工具,能捕獲和顯示SOPC中的實(shí)時(shí)信號(hào)特性,由軟IP核、編程硬件和分析軟件構(gòu)成,通過JTAG接口下載FPGA配置數(shù)據(jù)和上載捕獲的信號(hào)數(shù)據(jù)。通過實(shí)時(shí)板級(jí)測(cè)試,減少功能驗(yàn)證時(shí)間。

JTAG接口在DSP器件中的應(yīng)用

在DSP器件中,使用JTAG接口主要有兩種工作模式:邊界掃描模式和仿真模式。例如TMS320C6000系列中的JTAG端口由7到17個(gè)信號(hào)組成,其中5個(gè)信號(hào)為IEEE 1149.1標(biāo)準(zhǔn)信號(hào),仿真信號(hào)EMUn用于選擇芯片的工作模式。芯片具有兩個(gè)TAP,一個(gè)用于邊界掃描,一個(gè)用于仿真。

關(guān)于邊界掃描的DFT問題

器件選擇

?選擇IEEE 1149.1兼容的器件:當(dāng)前一些大規(guī)模的集成電路都帶有JTAG接口,采用1149.1兼容的器件,能增加邊界掃描測(cè)試的覆蓋率。

?雙功能的JTAG端口:盡量避免選擇帶雙功能JTAG端口的器件。這些器件的雙功能引腳,在上電時(shí)默認(rèn)為內(nèi)核功能模式,通過預(yù)定義的JTAG使能引腳,將雙功能引腳切換到JTAG模式,因此,設(shè)計(jì)師必須確認(rèn)在進(jìn)行板級(jí)邊界掃描之前,能夠訪問和控制JTAG使能腳。

?所有IEEE 1149.1兼容的器件必須支持強(qiáng)制的SAMPLE/PRELOAD,EXTEST和BYPASS指令,并最好也支持可選的HIGHZ和IDCODE指令。

?對(duì)于CPLD器件,建議采用IEEE 1532兼容器件,這樣可使來自不同廠家的CPLD器件同時(shí)進(jìn)行配置。

掃描鏈布局

?JTAG控制信號(hào)的連接:TCK、TMS和可選的TRST并行連接,TDI、TDO信號(hào)將邊界掃描器件組成一個(gè)菊花鏈。

?分區(qū):(1)為了滿足第三方調(diào)試/仿真工具的要求,有些器件(如DSP)必須位于同一個(gè)分離鏈中。(2)為了使不同的FPGA和CPLD廠商的在系統(tǒng)配置軟件工具同各自器件良好通信,不同公司的器件必須位于不同鏈中。(3)不同的邏輯系列器件(如ECL/TTL)放在不同的鏈中。(4)為有利于測(cè)試分區(qū)、診斷分辨率的提高或優(yōu)化測(cè)試向量的執(zhí)行,應(yīng)對(duì)器件進(jìn)行分區(qū)。(5)在系統(tǒng)環(huán)境中,提供到背板接口的器件應(yīng)進(jìn)行分區(qū),這有利于進(jìn)行板到板互連測(cè)試時(shí)優(yōu)化測(cè)試向量的執(zhí)行。

?盡可能將邊界掃描鏈連接到邊緣連接器,這樣可不需要針床,避免因不清潔導(dǎo)致的接觸不良,有利于背板環(huán)境下的系統(tǒng)級(jí)訪問。

?對(duì)于高速的JTAG應(yīng)用,如SDRAM測(cè)試、FLASH編程等,TCK的速度高于10MHz,建議使用一個(gè)阻抗匹配的RC網(wǎng)絡(luò)端接(通常采用60-100Ω的電阻和100pF的電容串接),所有其它的輸入使用一個(gè)弱的上拉電阻(10kΩ)。為了抑制反射,在菊花鏈的最后一個(gè)TDO引腳串接一個(gè)22Ω的電阻。

?通過放置一個(gè)0Ω的旁路電阻,可實(shí)現(xiàn)對(duì)邊界掃描器件的物理旁路。有時(shí)由于上市時(shí)間的壓力,邊界掃描器件并未實(shí)現(xiàn)其功能和對(duì)其進(jìn)行測(cè)試,如果它是掃描鏈中的一部分,將導(dǎo)致電路板上該鏈中的剩余器件無法進(jìn)行邊界掃描測(cè)試。這時(shí)可以使用旁路電阻對(duì)單個(gè)器件和多個(gè)器件進(jìn)行旁路。

?最好對(duì)進(jìn)入板上的所有IEEE 1149.1輸入信號(hào)進(jìn)行緩沖,以保證信號(hào)的完整性,特別是TCK和TMS。一個(gè)通用的規(guī)則是,如果電路板線長(zhǎng)度相對(duì)較短,74244型緩沖器可扇出4~6個(gè)器件,如果緩沖器和邊界掃描器件間導(dǎo)線較長(zhǎng)(大于10cm),建議一個(gè)緩沖器扇出1~2個(gè)器件。

對(duì)非邊界掃描器件的控制

?對(duì)非邊界掃描邏輯控制信號(hào)的訪問:為了防止測(cè)試時(shí)的信號(hào)競(jìng)爭(zhēng)導(dǎo)致器件損壞或測(cè)試不可靠,非邊界掃描器件的控制信號(hào)必須連到邊界掃描單元,以實(shí)現(xiàn)對(duì)該器件的非使能控制。

?時(shí)鐘信號(hào)的控制:有時(shí)需要對(duì)同步存儲(chǔ)器讀寫的時(shí)鐘信號(hào)進(jìn)行控制,用測(cè)試時(shí)鐘替代或?qū)r(shí)鐘關(guān)斷。

?對(duì)連接器的測(cè)試,可將連接器的引腳接至邊界掃描器件的掃描單元,通過在連接器上外接的短接器,實(shí)現(xiàn)直通測(cè)試。

對(duì)FPGA器件

?IEEE 1149.1只提供了靜態(tài)測(cè)試能力,對(duì)于高速應(yīng)用的BIST,可以充分利用FPGA對(duì)軟IP內(nèi)核的支持能力和可重新配置能力,在電路板裝配階段,將FPGA配置為帶BIST功能的內(nèi)核,實(shí)現(xiàn)全速自測(cè)試,在系統(tǒng)集成階段和產(chǎn)品發(fā)運(yùn)時(shí),將FPGA配置為其原有的正常功能。

結(jié)語

IEEE 1149.1很好地解決了微型器件封裝、高密度電路板探測(cè)等問題,是內(nèi)置自測(cè)試(BIST)采用的主要技術(shù)。為提高電路板測(cè)試的故障覆蓋率、降低測(cè)試成本,在電路板的設(shè)計(jì)初期,就應(yīng)考慮電路板的測(cè)試策略,采用可測(cè)試性設(shè)計(jì)方法,借助測(cè)試軟件進(jìn)行可測(cè)試性分析、評(píng)估和優(yōu)化,以提高TPS的開發(fā)效率,增強(qiáng)電路板的可測(cè)試性。

- 測(cè)試技術(shù)(20905)

- 邊界掃描(14900)

相關(guān)推薦

電路板制板可測(cè)試性技術(shù)分析

1134

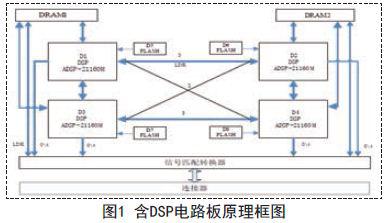

1134針對(duì)含DSP電路板的測(cè)試方法與診斷分析

8277

8277

什么是邊界掃描?JTAG邊界掃描測(cè)試方案介紹

1497

1497

電路板改板設(shè)計(jì)中的可測(cè)試性技術(shù)

電路板改板設(shè)計(jì)中的可測(cè)試性技術(shù)

電路板的自動(dòng)檢測(cè)技術(shù)

電路板的自動(dòng)檢測(cè)技術(shù)

電路板維修故障分析

電路板設(shè)計(jì)與制作

電路板設(shè)計(jì)可測(cè)試性技術(shù)

電路板設(shè)計(jì)可測(cè)試性技術(shù)

電路板設(shè)計(jì)可測(cè)試性技術(shù)

邊界掃描測(cè)試

邊界掃描測(cè)試技術(shù)介紹

邊界掃描測(cè)試技術(shù)簡(jiǎn)介及原理

Cyclone IV器件的JTAG邊界掃描測(cè)試

IC測(cè)試中三種常見的可測(cè)性技術(shù)

IMX8m Plus邊界掃描檢查鏈?zhǔn)〉脑颍?/a>

PCB電路板的測(cè)試點(diǎn)是什么

PCB可制造性與可測(cè)試性技術(shù)概述

一種新的PCB測(cè)試技術(shù):邊界掃描測(cè)試技術(shù)

產(chǎn)品級(jí)PCB電路板的技術(shù)要求

關(guān)于 RK3568 JTAG 邊界掃描的問題

印制電路板互聯(lián)技術(shù)的應(yīng)用

在配置的Virtex-5上進(jìn)行邊界掃描時(shí)出現(xiàn)問題怎么辦

基于邊界掃描的電路板快速測(cè)試系統(tǒng)設(shè)計(jì)

基于JTAG的互連測(cè)試技術(shù)原理分析概述

如何使用Goepel的Cascon為L(zhǎng)S1027設(shè)置邊界掃描?

如何通過邊界掃描測(cè)試進(jìn)行差分信號(hào)測(cè)試?

嵌入式邊界掃描系統(tǒng)是什么?怎樣去實(shí)現(xiàn)它?

有沒有免費(fèi)的工具可用于STM32F4進(jìn)行邊界掃描測(cè)試?

用mudbus+visa,通過labview來測(cè)試電路板,獲取電路板信息

請(qǐng)問什么是邊界掃描?

請(qǐng)問印制電路板是怎樣應(yīng)用互聯(lián)技術(shù)的?

采用邊界掃描法測(cè)試系統(tǒng)級(jí)芯片互連的信號(hào)完整性

高速邊界掃描主控器設(shè)計(jì)

17

17SPEA 4080 飛針測(cè)試機(jī) 高產(chǎn)能高精度電路板測(cè)試

定制柔性FPC電路板及硬性PCB電路板

SPEA 3030BT桌面型電路板測(cè)試機(jī)

邊界掃描測(cè)試技術(shù)在硬件實(shí)驗(yàn)中的應(yīng)用

17

17VXI邊界掃描模塊接口電路的設(shè)計(jì)

29

29基于VXI總線的多功能邊界掃描控制器

26

26應(yīng)用于FPGA的邊界掃描設(shè)計(jì)

22

22基于邊界掃描的電路板快速測(cè)試系統(tǒng)設(shè)計(jì)

20

20JTAG邊界掃描技術(shù)設(shè)計(jì)方案

29

29PCB噴碼機(jī)電路板行業(yè)

電路板冷熱沖擊試驗(yàn)箱

PCB印刷電路板應(yīng)力測(cè)試儀TSK-32

PCB噴碼機(jī)在電路板行業(yè)中的應(yīng)用

邊界掃描技術(shù)及其在VLSI芯片互連電路測(cè)試中的應(yīng)用

13

13基于廣義特征分析與邊界掃描技術(shù)的混合信號(hào)測(cè)試系統(tǒng)

21

21電路板改板設(shè)計(jì)中的可測(cè)試性技術(shù)

420

420電路板改板技術(shù)之光板測(cè)試工藝指導(dǎo)

891

891基于邊界掃描的電路板測(cè)試系統(tǒng)

1653

1653

VLSI邊界掃描測(cè)試故障診斷

30

30基于USB總線的邊界掃描測(cè)試系統(tǒng)

25

25基于邊界掃描的PCB測(cè)試

50

50基于邊界掃描技術(shù)的板級(jí)測(cè)試分析

45

45安捷倫推出Agilent x1149邊界掃描分析儀

4124

4124Cyclone_IV器件的JTAG邊界掃描測(cè)試

0

0簡(jiǎn)述BSDL邊界掃描語言,BSDL邊界掃描語言的應(yīng)用

7916

7916

邊界掃描測(cè)試技術(shù)在帶DSP芯片數(shù)字電路板測(cè)試中的應(yīng)用解析

3

3邊界掃描測(cè)試的基本原理及其測(cè)試系統(tǒng)的設(shè)計(jì)

19

19基于邊界掃描技術(shù)的難題提出了MERGE法邊界掃描技術(shù)解決方案

1560

1560

雷達(dá)嵌入式測(cè)試和診斷技術(shù)

0

0邊界掃描測(cè)試技術(shù)的原理解析

23574

23574

邊界掃描測(cè)試應(yīng)用與九大指令

6531

6531

TMS320VC5510 GGW BSDL Model邊界掃描DSP模型的詳細(xì)資料概述

5

5邊界掃描技術(shù)的詳細(xì)資料描述

0

0如何在邊界掃描機(jī)制下增加板級(jí)互連的故障診斷覆蓋率

1202

1202

你了不了解邊界掃描

5123

5123基于一種PCB的測(cè)試系統(tǒng)設(shè)計(jì)

671

671邊界掃描測(cè)試解決方案的原理及應(yīng)用分析

10213

10213

便攜式邊界掃描故障診斷儀的軟硬件設(shè)計(jì)與實(shí)現(xiàn)

703

703

基于MERGE邊界掃描測(cè)試模型實(shí)現(xiàn)雷達(dá)數(shù)字自動(dòng)測(cè)試系統(tǒng)的設(shè)計(jì)

2110

2110

DSP電路板測(cè)試中的邊界掃描技術(shù)研究綜述

9

9JTAG(四) 邊界掃描測(cè)試技術(shù)

20

20邊界掃描測(cè)試軟件XJTAG和TopJTAG介紹

1278

1278

基于Xilinx FPGA的邊界掃描應(yīng)用

655

655

一種新的PCB測(cè)試技術(shù)

203

203 電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論