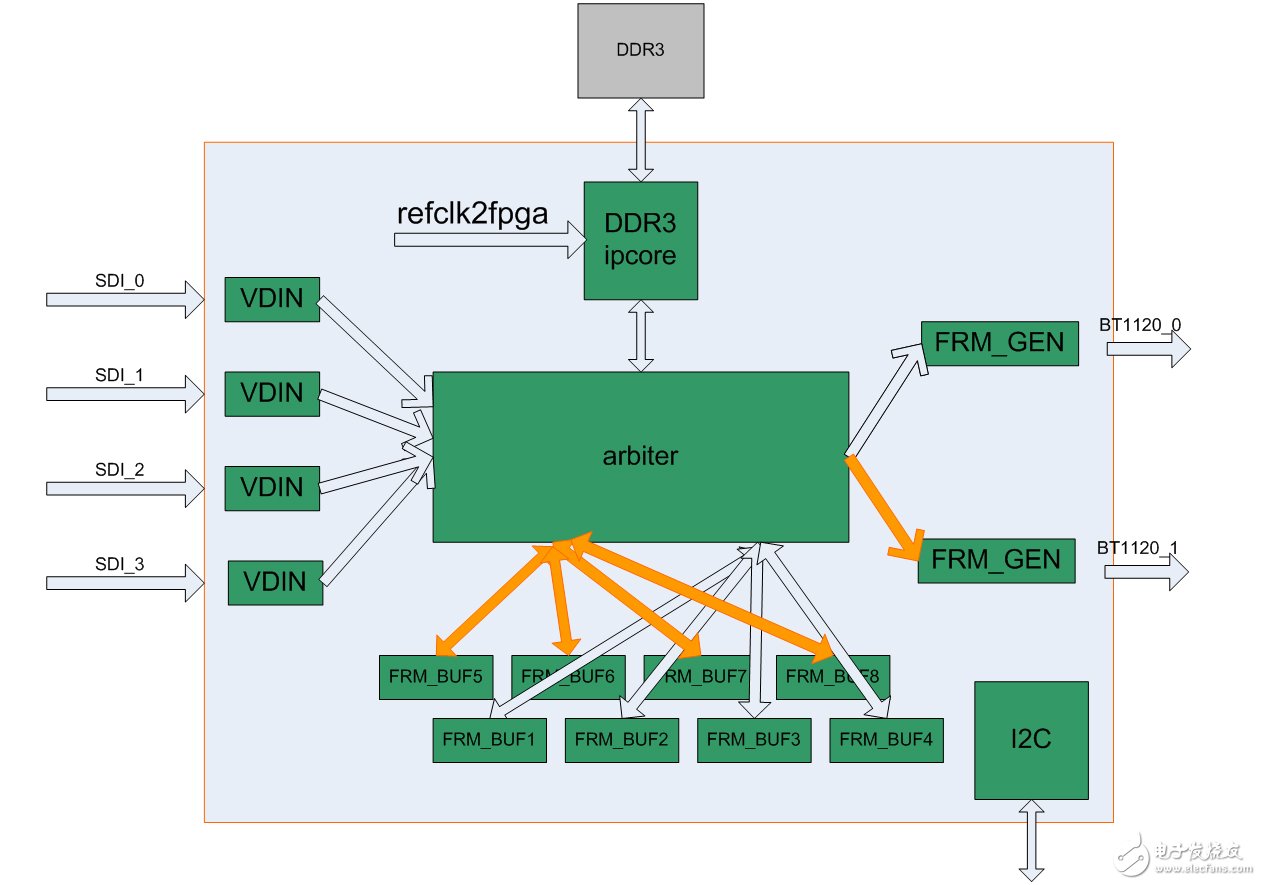

參考設計模塊功能描述

讓我們以其中的一顆FPGA為例,描述參考設計中的系統功能模塊以及處理細節。由圖示(四通道 HD-SDI DVR 架構)我們可知,系統中在需要進行幀數據處理的時候外掛一顆DDR3顆粒。同時其中I2C接口完成模式配置、切換功能。

VDIN模塊是HD-SDI視頻輸入處理分析模塊,采用Lattice自主知識產權 三速率SDI IP核接收模塊完成HD-SDI數據解析,并輸送給后續FRM_BUF幀緩存模塊申請視頻幀數據緩存。這里要說明的是輸入的每一路視頻數據為了便于邏輯處理,在緩存中開辟了兩個空間進行視頻幀數據存儲,分別對應于實時輸出通道和錄像通道。即對應于八個FRM_BUF模塊。

Arbiter模塊完成八路幀緩存數據的寫入、讀取的多端口仲裁。同時與DDR3控制器進行信號握手工作。這里我們采用的是智能控制讀寫策略與DDR3 IP核配合,以達到最高效率,使得DDR3運行于較低主頻同時能夠滿足系統設計需求。

DDR3 IPCORE核模塊是采用Lattice自主知識產權DDR3控制器。這是一個全功能的DDR3存儲器控制器IP核,接口至符合行業標準的DDR3元件和DIMM(DualInlineMemoryModules)。DDR3 IP核支持8bit到72bit DQ數據位寬,最大支持到58Gbps帶寬。當然這里我們僅采用了16bit數據(DQ)位寬的DDR3顆粒且主頻運行在300Mhz。

FRM_GEN模塊是BT1120成幀模塊。該模塊從FRM_BUF中申請讀取視頻幀數據,按照BT1120協議格式構造幀數據并發送給Hi3531。當然為了區分四路數據中的不同通道數據,成幀模塊中對輸出數據添加了特征字以便Hi3531識別處理。

I2C模塊,工作于從模式。用于完成寄存器配置、模式控制。

四通道HD-SDI DVR 架構

參考設計要點

HD-SDI、DDR3的硬件設計是該系統的一個挑戰。Lattice提供了完備的原理圖以及PCB設計指導。嚴格遵循設計指導會獲得良好的PCB信號質量,順利推進產品開發進度。客戶可以從Lattice當地技術支持獲取必要的技術協助。

視頻縮放處理。這里的實時處理通道,當需要輸出四拼接畫面時,需要進行縮小處理。這里采用了適當的縮小策略,在不浪費過多邏輯資源的情況下,保持了畫面高清晰度。

DDR3的效率是本參考設計的另外一個挑戰。如果在有限的DDR3帶寬資源下,最大限度的滿足設計需求,這是本參考設計所認真考慮的。比方說根據不同的視頻流提供相應的訪問權重,比方說充分利用DDR3物理特性的智能bank管理以及高效率刷新機制,這些優化都大大提高了DDR3的訪問效率。參考設計無論是從系統模塊搭建,仲裁策略設計還是DDR3 IP核智能管理等方面都提供了良好的范例。

結論

隨著經濟迅猛發展,人民生活水平不斷提高,尋常百姓的安全意識也在不斷增強,安全視頻監控逐漸由政府機關、企事業單位迅速滲透到消費類領域。LatticeECP3 針對安防等視頻處理領域不斷加大投入。為客戶提供更多的低成本、高穩定性接口、參考設計、IP核以及設計方案,協助客戶更快地將產品推向市場。

本文選自電子發燒友網6月《智能工業特刊》Change The World欄目,轉載請注明出處。

用戶評論(0)