特權同學為大家介紹市面上最常見的Xilinx spartan-3的xc3s400的配置電路...

2013-05-31 14:07:33 3814

3814

這里要列出一個市面上最常見的spartan-3的xc3s400的配置電路,所有spartan-3的FPGA配置電路的鏈接方式都是一樣的。

2015-02-04 09:47:57 3259

3259

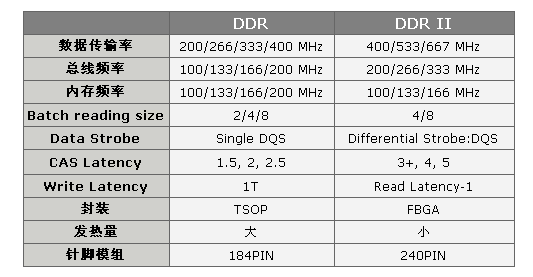

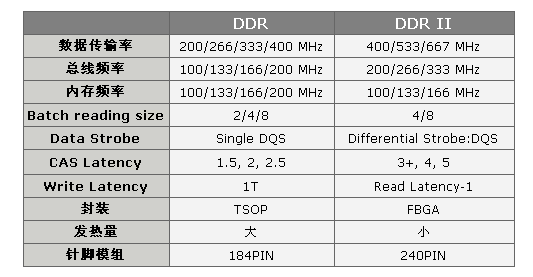

DDR內(nèi)存1代已經(jīng)淡出市場,直接學習DDR3 SDRAM感覺有點跳躍;如下是DDR1、DDR2以及DDR3之間的對比。

2023-04-04 17:08:47 2871

2871

DDR2 DDR3 dimm接口封裝文件,金手指接口

2017-12-03 22:22:02

DDR4,DDR3,DDR2,DDR1及SDRAM有什么不同之處?

2021-03-12 06:22:08

一般的FPGA的數(shù)據(jù)傳輸接送接口不都是用USB的么,我想用藍牙無線的接口,想買響應的藍牙模塊,有沒有能和Spartan-3 FPGA 系列 相匹配的藍牙模塊呢?

2019-08-14 16:33:55

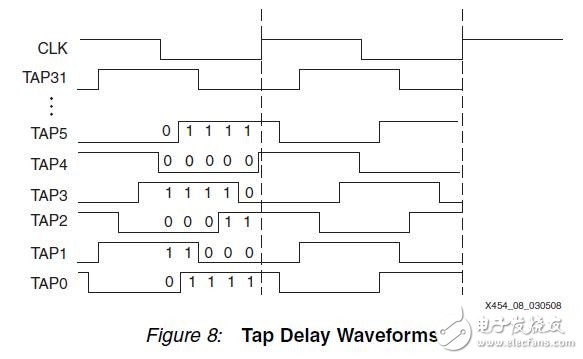

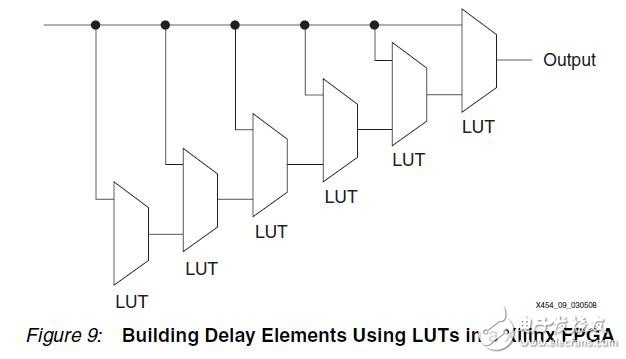

更快、更大,每比特的功耗也更低,但是如何實現(xiàn)FPGA和DDR3 SDRAM DIMM條的接口設計呢? 關鍵字:均衡(leveling)如果FPGA I/O結構中沒有包含均衡功能,那么它與DDR3

2019-04-22 07:00:08

:圖2:Spartan-7 FPGA同一bank連接1.8V SPI Flash和1.35V DDR3L雖然這不是一個標準的解決方案,只是限于有限的I/O資源,但是對于小型系統(tǒng)設計不失為一種好的方法。具體設計細節(jié)如器件選型、原理圖、確定時鐘頻率等要求請參看官方文檔`

2018-08-02 09:37:08

大家好!我有一個問題。我已經(jīng)閱讀了應用筆記XAPP486:7:1 Spartan-3E FPGA中的串行化速度高達666 Mbps和XAPP485:1:7 Spartan-3E FPGA中的串行化

2018-09-28 11:41:22

約束文件(XDC文件),它包含用于時序分析的“create_clock”和“set_input_jitter”約束。在ISE 14.7和Spartan-3 FPGA中,我可以使用稱為“時鐘向?qū)А钡腎P來

2019-08-02 09:54:40

本帖最后由 lpc2292 于 2013-2-27 20:24 編輯

“部分 I: 用 Spartan-3 系列 FPGA 進行設計”第 1 章 “概述”第 2 章 “使用全局時鐘資源”第 3

2013-02-27 20:20:10

與IP引腳接口時是否應該考慮特殊注意事項?或者將DDR SDRAM連接到Spartan 3E的具體要求是什么?到目前為止我的考慮: -Bank#需要具有相同的邏輯電平 - 需要考慮高速布局 - >

2019-05-10 13:59:37

求一DDR2接口設計代碼

2013-04-24 10:00:36

大家好,什么是spartan 3a入門套件板中DDR2內(nèi)存芯片的工作頻率?謝謝,randeel。

2019-08-22 09:18:39

、DDR2、DDR3型SDRAM存儲器,DDR系列的存儲器都需要FPGA芯片有對應的硬件電路結構支持。對于Altera Cyclone IV系列的FPGA,其最高支持到DDR2存儲器(不支持DDR3存儲器

2016-12-30 20:05:09

1、從工作平率上說:首先接口就全部不同 電壓不同 頻率的計算方法不同 SDR的頻率就是外頻 133=133 DDR的頻率就是外頻的2倍 133=266 DDR2的頻率就是外頻的4倍 133=533

2014-12-30 14:35:58

1、從工作平率上說:首先接口就全部不同 電壓不同 頻率的計算方法不同 SDR的頻率就是外頻 133=133 DDR的頻率就是外頻的2倍 133=266 DDR2的頻率就是外頻的4倍 133=533

2014-12-30 14:36:44

你好,有誰知道為什么Spartan-3E系列不支持DDR2接口?至少就MIG而言。問候,亞歷克斯以上來自于谷歌翻譯以下為原文Hello, does anyone know why DDR2

2019-05-09 14:23:32

為什么利用Spartan-3 FPGA來實現(xiàn)DSP系統(tǒng)?Spartan-3系列器件在平板顯示器中的應用有哪些?

2021-04-29 06:32:17

為什么利用Spartan-3 FPGA來實現(xiàn)DSP系統(tǒng)?Spartan-3系列器件在平板顯示器中的應用有哪些?

2021-04-30 07:12:22

這里要談的是Xilinx的spartan-3系列FPGA的配置電路。當然了,其它系列的FPGA配置電路都是大同小異的,讀者可以類推,重點參考官方提供的datasheet,畢竟那才是最權威的資料。

2019-10-10 06:16:52

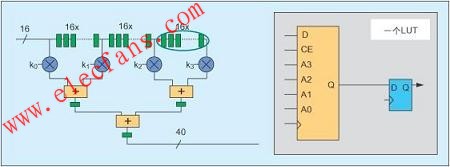

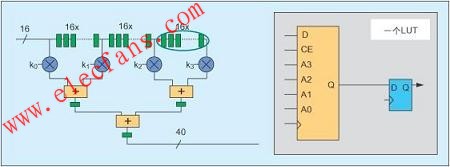

本文闡述了Spartan-3 FPGA針對DSP而優(yōu)化的特性,并通過實現(xiàn)示例分析了它們在性能和成本上的優(yōu)勢。

2019-10-18 07:11:35

、DDR2與DDR3內(nèi)存的特性區(qū)別: 1、邏輯Bank數(shù)量 DDR2 SDRAM中有4Bank和8Bank的設計,目的就是為了應對未來大容量芯片的需求。而DDR3很可能將從2Gb容量起步,因此起始

2011-12-13 11:29:47

`例說FPGA連載41:DDR控制器集成與讀寫測試之DDR2 IP核接口描述特權同學,版權所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1c0nf6Qc 如圖

2016-10-27 16:36:58

最近在設計一個需要連接DDR2 SDRAM的FPGA小系統(tǒng),由于是第一次在使用SDRAM,在硬件連接時就遇到一個很糾結的問題——引腳的連接。看了幾種參考設計,發(fā)現(xiàn)有兩種說法:1、DDR2的數(shù)據(jù)(DQ

2017-09-25 17:51:50

以前的一個DDR2接口設計,在原板上運行正常,現(xiàn)在重做了一塊板子,換了一款FPGA芯片,重新編譯后,無法初始化DDR2。IP重新例化了,但是不知到怎么運行TCL文件,運行哪個文件?有高手給指點一下,或者有相關教程,或書籍推薦也可以。先謝謝啦!

2013-12-10 20:38:10

我已經(jīng)完成了幾次搜索,并且無法找到一個文檔,告訴我在Spartan-6上可以使用哪些引腳用于DDR2接口。我確實理解引腳交換等,但有些引腳不能用于DDR2。我正在尋找的是以下具體內(nèi)容......1

2019-01-24 10:22:29

嗨,我想為Spartan3 XC3S4000 FG900設計板,之后我為Spartan-6設計了一塊板。在針對Spartan-6的Xilinx文檔中,我找到了“Spartan-6 FPGA電源管理

2019-07-17 09:16:04

選擇。視頻處理和圖形生成需要存儲海量數(shù)據(jù),FPGA內(nèi)部的存儲資源無法滿足存儲需求,因此需要配置外部存儲器。與DDR2 SDRAM相比,DDR3 SDRAM帶寬更好高、傳輸速率更快且更省電,能夠滿足

2019-06-24 06:07:53

Xilinx公司發(fā)布的SP6,V6系列的FPGA中的DDR2的IP核是一大改變。它由原來的軟核變?yōu)榱擞埠耍伺e讓開發(fā)DDR2變的簡單,因為不需要太多的時序調(diào)試,當然也帶來了麻煩,這是因為當DDR2

2015-03-16 20:21:26

特性。 Spartan-3 FPGA的面世改變了嵌入式DSP的應用前景。雖然Spartan-3系列器件的價位可能較低,但它們同樣具有DSP設計所需的平臺特性。這些平臺特性能夠以較高的面積利用率實現(xiàn)信號

2019-06-27 06:12:26

Cyclone III系列型號為EP3C16F484C6N的FPGA作為控制器,以Micron公司生產(chǎn)的型號為MT47H16M16BG-5E(16M×16bit)的DDR2 SDRAM為存儲器。用一個IP核完成

2011-05-03 11:31:09

基于Xilinx FPGA的DDR2 SDRAM存儲器接口

2012-08-20 18:55:15

均衡的定義和重要性是什么如何實現(xiàn)FPGA和DDR3 SDRAM DIMM條的接口設計?

2021-05-07 06:21:53

嗨!我正在尋找Spartan-3A / 3ANFPGA入門KitBoard用戶指南(UG334)。具體來說第13章:DDR2 SDRAM和我不明白如何使用DDR2 SDRAM,因為例如這個內(nèi)存

2019-07-31 06:18:10

Spartan-3 FPGA系列如何僅通過在接收器數(shù)據(jù)通路中加入一個倒相器即可避免大量使用過孔?如何利用Spartan-3 FPGA進行LVDS信號倒相設計?

2021-05-06 07:30:25

親愛的大家! 如何在IOB中為spartan-3生成FPGA使用TFF(TFF1和TFF2三態(tài)觸發(fā)器)? 我想在spartan-3 FPGA(Spartan-3 GenerationFPGA用戶指南

2019-06-28 09:53:28

你好我正在使用atlys主板,我必須在spartan-6上實現(xiàn)ddr2(MT47H64M16-25E)接口,...通過使用MIG及其示例設計,在模擬中一切正常....通過注意ddr2接口,例如

2019-10-28 07:46:43

由于系統(tǒng)帶寬不斷的增加,因此針對更高的速度和性能,設計人員對存儲技術進行了優(yōu)化。下一代雙數(shù)據(jù)速率(DDR)SDRAM芯片是DDR3 SDRAM。 DDR3 SDRAM具有比DDR2更多的優(yōu)勢。這些

2019-08-09 07:42:01

本文介紹了采用Xilinx公司的Spartan-3 FPGA實現(xiàn)通用視頻采集系統(tǒng)的設計方案。

2021-06-08 06:34:30

我正在使用spartan6 MCB與DDR2建立接口。我是VHDL的新手。在我預先編寫的示例設計數(shù)據(jù)和地址中,我想修改設計以給出用戶定義的數(shù)據(jù)和地址,并且想要添加三個控制信號wr,rd

2020-03-25 07:31:23

嗨,我即將使用Virtex-4QV設備(XQR4VFX140)開始一個新項目。雖然我對使用DDR2 / DDR3 SDRAM的Xilinx MIG有一些經(jīng)驗,但我發(fā)現(xiàn)MIG IP不支持VIRTEX-4QV器件。那可能是另類?如何將DDR2 SDRAM與此FPGA連接?彌敦道

2020-04-02 06:08:46

DDR2控制和FPGA實現(xiàn)

2015-07-21 19:28:14

DDR,DDR2,DDR3,DDR4,LPDDR區(qū)別文所有權歸作者Aircity所有1什么是DDRDDR是Double Data Rate的縮寫,即“雙比特翻轉”。DDR是一種技術,中國大陸工程師

2021-09-14 09:04:30

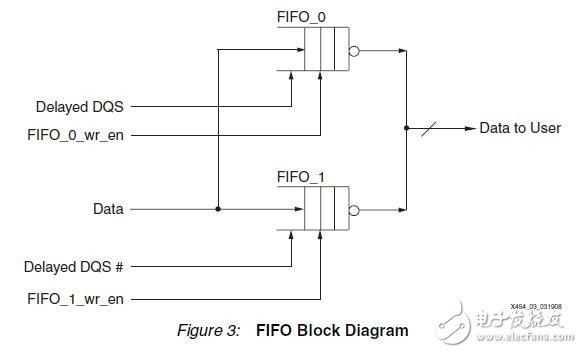

SDRAM的時鐘CLK可以差不多,但是DDR2的DQS速度可以達到DDR的兩倍,這也就是它們的DQ/DQS操作時序一樣的情況下,數(shù)據(jù)吞吐量卻倍增的原因。比對DDR與DDR2的接口,其實DDR2就多了一

2014-12-30 15:22:49

大家好,我開發(fā)了DDR2內(nèi)存和高速ADC 500Mpbs(2 ADC)到Spartan6 LX25器件。我想知道銀行分配的最佳選擇,因為接口都是高速且需要時鐘定時至關重要。根據(jù)MIG的推薦,DDR2

2019-07-12 06:30:06

如何測試ARM外接DDR2的正確連接? ARM具有DDR3接口而沒有SDRAM接口,目前在調(diào)試過程中發(fā)現(xiàn)程序在DDR3中跑飛,不知道如何去查或者不知道怎么定位在那出現(xiàn)問題,敬請各位指教,不勝感激。

2020-06-17 06:20:38

的內(nèi)存控制器的設計與應用.pdf基于Spartan-3+FPGA的DDR2+SDRAM存儲器接口設計.pdf一種采用FPGA設計的SDRAM控制器.pdf用Xilinx+FPGA實現(xiàn)DDR+SDRAM控制器.pdf

2012-07-28 14:40:53

各位好!之前用DM368的開發(fā)板進行實驗,目前需要根據(jù)自己公司的產(chǎn)品重新畫電路板,由于開發(fā)板上的FLASH和DDR2 SDRAM過于老舊,需要對這兩顆零件重新選型。我不太清楚在選擇DDR2

2018-06-21 05:34:23

,所以4片DDR2以地址和控制線共用、數(shù)據(jù)線獨立的方式進行管腳連接。圖1 接口總框圖EP3C16只有TOP和BOTTOM邊的BANK支持200MHz DDR2接口(因為DDR2管腳的特殊要求,DQS

2019-05-31 05:00:05

DDR2 SDRAM控制器的設計與實現(xiàn)

本文介紹了&&," -&,+. 的基本特征!并給出了一種&&," -&,+. 控制器的設計方法!詳述了其基本結構和設計思想!并使用+JC:8B 公

2010-02-09 14:57:51 64

64 Spartan-3 Generation FPGAs應用資料

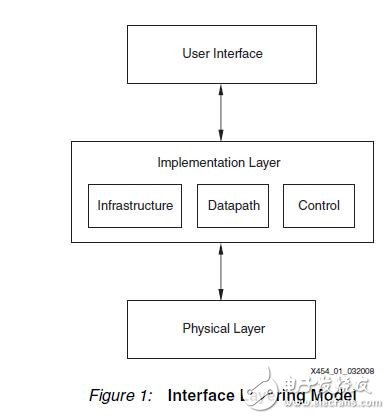

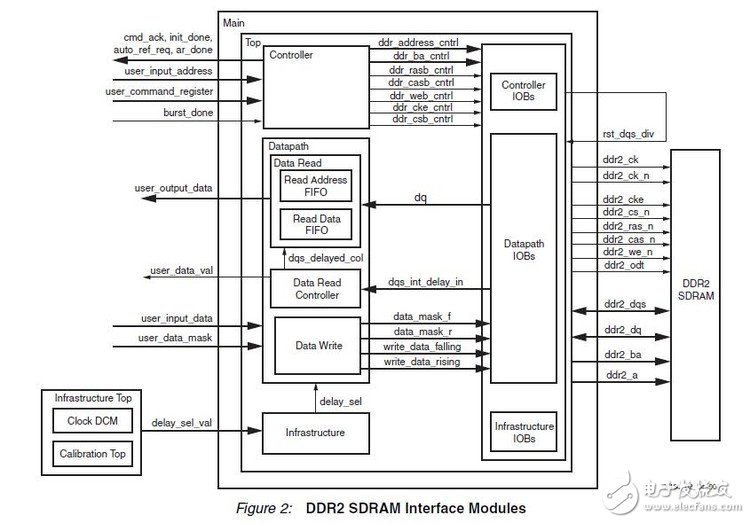

DDR2 SDRAM Interface for Spartan-3 Generation FPGA

2010-05-13 13:57:12 27

27 DDR2 SDRAM 和 FB-DIMM的電氣檢驗:

隨著DDR2 SDRAM時鐘頻率和信號邊沿速率不斷提高,檢查電路板結構、電氣系統(tǒng)和信令正變得越來越重要。本應用指南介紹了電路板、電源系統(tǒng)、

2010-08-06 08:29:01 39

39 不只計算機存儲器系統(tǒng)一直需要更大、更快、功率更低、物理尺寸更小的存儲器,嵌入式系統(tǒng)應用也有類似的要求。本應用指南介紹了邏輯分析儀在檢驗DDR, DDR2 和DDR3 SDRAM 命令和

2010-08-06 08:29:49 79

79 在高速、大容量存儲的系統(tǒng)設計中,DDR2 SDRAM為設計者提供了高性價比解決方案。在FPGA中實現(xiàn)DDR2 SDRAM控制器,降低了系統(tǒng)功耗并節(jié)省空間, 縮短開發(fā)周期,降低系統(tǒng)開發(fā)成本

2010-12-13 17:10:35 49

49 DDR2名詞解釋

DDR2的定義:

DDR2(Double Data Rate 2) SDRAM是由JEDEC(電子設備工程聯(lián)合委員會)進行開發(fā)的新生代內(nèi)存技術標準,它與上一代DDR內(nèi)

2009-04-26 18:02:22 1186

1186

什么是DDR2 SDRAM

DDR2的定義:

DDR2(Double Data Rate 2) SDRAM是由JEDEC(電子設備工程聯(lián)合委員會)進行開發(fā)的新生代內(nèi)存技

2009-12-17 11:17:59 623

623 DDR2的定義:

DDR2(Double Data Rate 2) SDRAM是由JEDEC(電子設備工程聯(lián)合委員會)進行開發(fā)的新生代內(nèi)存技術標準,它與上一代DDR內(nèi)存技術標準最大的不

2009-12-17 16:26:19 731

731 DDR2,DDR2是什么意思

DDR2(Double Data Rate 2) SDRAM是由JEDEC(電子設備工程聯(lián)合委員會)進行開發(fā)的新生代內(nèi)存技術標準,它與上一代DDR內(nèi)

2010-03-24 16:06:36 1381

1381 Spartan-3FPGA能以突破性的價位點實現(xiàn)嵌入式DSP功能。本文闡述了Spartan-3 FPGA針

2010-12-17 11:31:23 675

675

文中在介紹DDR2的工作原理的基礎上,給出了一個用VHDL語言設計的DDR2 SDRAM控制器的方法,并且提出了一種在高速圖像處理系統(tǒng)中DDR2 SDRAM的應用方案,同時在Virtex-5系列的FPGA上得到了實現(xiàn)

2011-07-23 10:03:16 5102

5102 文章對適用DDR2 SDRAM控制器的結構、接口和時序進行了深入研究與分析,總結出一些控制器的關鍵技術特性,然后采用了自頂向下(TOP-IX)WN)的設計方法,用Verilog硬件描述語言實現(xiàn)控制器,

2011-09-01 16:36:29 174

174 SDRAM, DDR, DDR2, DDR3 是RAM 技術發(fā)展的不同階段, 對于嵌入式系統(tǒng)來說, SDRAM 常用在低端, 對速率要求不高的場合, 而在DDR/DDR2/DDR3 中,目前基本上已經(jīng)以DDR2 為主導,相信不久DDR3 將全面取代

2012-01-16 14:53:01 0

0 使用功能強大的FPGA來實現(xiàn)一種DDR2 SDRAM存儲器的用戶接口。該用戶接口是基于XILINX公司出產(chǎn)的DDR2 SDRAM的存儲控制器,由于該公司出產(chǎn)的這種存儲控制器具有很高的效率,使用也很廣泛,

2013-01-08 18:15:50 237

237 基于Xilinx的DDR2 SDRAM存儲控制器的用戶接口設計與仿真,本設計通過采用多路高速率數(shù)據(jù)讀寫操作仿真驗證,可知其完全可以滿足時序要求,由綜合結果可知其使用邏輯資源很少,運行速

2013-01-10 14:12:45 2990

2990 ddr2_sdram 操作時序,非常好的教程,可以充分了解DDR2

2015-10-28 11:07:39 19

19 基于FPGA的VGA接口實現(xiàn)和字符顯示論文

2015-10-29 17:18:24 8

8 用FPGA設計DDR2控制器講解DDR2時序原理用戶接口設計幫助用戶快速掌握DDR2的控制技術新手上路的非常有幫助的資料。

2015-11-10 10:54:14 3

3 DDR2 SDRAM操作時序規(guī)范,中文版規(guī)范

2015-11-10 17:42:44 0

0 Xilinx FPGA工程例子源碼:Xilinx DDR2存儲器接口調(diào)試代碼

2016-06-07 14:54:57 27

27 SDRAM):DDR4提供比DDR3/ DDR2更低的供電電壓1.2V以及更高的帶寬,DDR4的傳輸速率目前可達2133~3200 MT/s。

2017-11-17 13:15:49 25152

25152 提出一種便于用戶操作并能快速運用到產(chǎn)品的DDR2控制器IP核的FPGA實現(xiàn),使用戶不需要了解DDR2的原理和操作方式的情況下,依然可以通過IP核控制DDR2。簡單介紹了DDR2的特點和操作

2017-11-22 07:20:50 4687

4687

DDR2(Double Data Rate2)SDRAM是由JEDEC(電子設備工程聯(lián)合委員會)制定的新生代內(nèi)存技術標準,它與上一代DDR內(nèi)存技術標準最大的不同:雖然采用時鐘的上升/下降沿同時傳輸

2017-11-25 01:41:01 3855

3855

本演示介紹了 Spartan?-3A 入門套件如何讓您立即獲得 Spartan-3A FPGA 器件的節(jié)能模式,高速 I/O 選項,DDR2 SDRAM 存儲器接口,商用閃存配置支持,以及利用 Device DNA 實現(xiàn)的 FPGA/IP 保護等特性。

2018-05-22 13:45:01 2484

2484 實現(xiàn)數(shù)據(jù)的高速大容量存儲是數(shù)據(jù)采集系統(tǒng)中的一項關鍵技術。本設計采用Altera 公司Cyclone系列的FPGA 完成了對DDR SDRAM 的控制,以狀態(tài)機來描述對DDR SDRAM 的各種時序

2019-08-14 08:00:00 3401

3401

本用戶指南為客戶使用 Spartan?-3 FPGA 系列各平臺 (Spartan-3、Spartan-3E、Spartan-3A、Spartan-3AN 和 Spartan-3A DSP FPGA

2020-03-05 08:00:00 16

16 DDR2 SDRAM采用雙數(shù)據(jù)速率結構實現(xiàn)高速運行。雙數(shù)據(jù)速率體系結構本質(zhì)上是4n預取體系結構,其接口設計為在I/O球處每個時鐘周期傳輸兩個數(shù)據(jù)字。DDR2 SDRAM的單次讀寫操作有效地包括在內(nèi)部

2020-05-21 08:00:00 1

1 Spartan-3 FPGA包括擴展的斯巴達-3A系列(斯巴達-3A、斯巴達-3AN和斯巴達-3A DSP平臺),以及早期的斯巴達-3和斯巴達-3E系列。這些系列的現(xiàn)場可編程門陣列(FPGA)是專門

2021-01-23 08:00:00 21

21 ARM與FPGA的接口實現(xiàn)的解析(應廣單片機)-該文檔為ARM與FPGA的接口實現(xiàn)的解析詳述資料,講解的還不錯,感興趣的可以下載看看…………………………

2021-07-22 09:47:55 14

14 基于FPGA的DDR3SDRAM控制器設計及實現(xiàn)簡介(arm嵌入式開發(fā)平臺PB)-該文檔為基于FPGA的DDR3SDRAM控制器設計及實現(xiàn)簡介資料,講解的還不錯,感興趣的可以下載看看…………………………

2021-07-30 09:05:51 7

7 基于FPGA的DDR3SDRAM控制器設計及實現(xiàn)(嵌入式開發(fā)式入門)-該文檔為基于FPGA的DDR3SDRAM控制器設計及實現(xiàn)總結文檔,是一份很不錯的參考資料,具有較高參考價值,感興趣的可以下載看看………………

2021-07-30 13:07:09 35

35 基于FPGA的SDRAM串口實驗(嵌入式開發(fā)板實驗報告)-基于FPGA的SDRAM串口實驗,verilog語言編寫

2021-08-04 09:43:17 37

37

電子發(fā)燒友App

電子發(fā)燒友App

評論