光纖項(xiàng)目系統(tǒng)概述

第一章項(xiàng)目背景

光纖項(xiàng)目是明德?lián)P承接自某研究所的項(xiàng)目。該項(xiàng)目功能是接收4路光纖數(shù)據(jù),經(jīng)過內(nèi)部DDR3緩存后,通過PCIE接口上送到電腦保存。其中光纖采集到數(shù)據(jù)后,需要做一定的算法處理,該算法處理由客戶實(shí)現(xiàn),明德?lián)P保留易修改、易插入的模塊接口。

該項(xiàng)目實(shí)質(zhì)就是一個(gè)數(shù)據(jù)采集卡功能:采集到高速數(shù)據(jù)并保存到電腦本地,具有速率高、數(shù)據(jù)量大的特點(diǎn)。采集卡項(xiàng)目均可參考此方案實(shí)現(xiàn)。

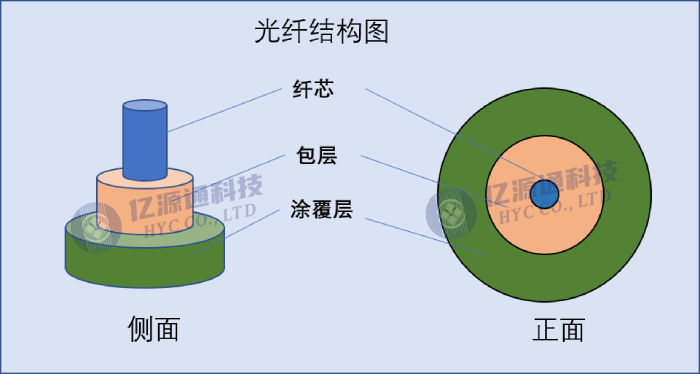

該項(xiàng)目使用到光纖接口,可以學(xué)習(xí)到光纖IP核的應(yīng)用。

本項(xiàng)目可以通過PCIE,實(shí)現(xiàn)對(duì)FPGA的配置。特別是實(shí)現(xiàn)了可分別配置和讀取1路接收FPGA、4路發(fā)送FPGA寄存器的功能。關(guān)于上位機(jī),如DSP、ARM、單片機(jī)、電腦 ,如何與FPGA通信交互的,可以參考此方案。(在優(yōu)化版本中,也提供了通過串口配置的方案,即將PCIE配置改為用串口配置。)

PCIE部分不作講解,要注意。

該項(xiàng)目有對(duì)應(yīng)的視頻專題課,并提供代碼學(xué)習(xí)。

第二章 系統(tǒng)功能和架構(gòu)

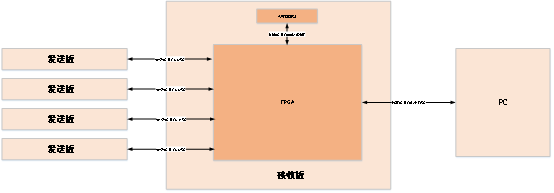

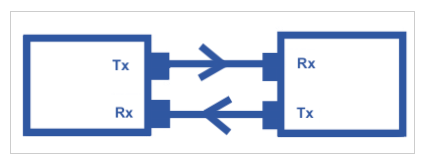

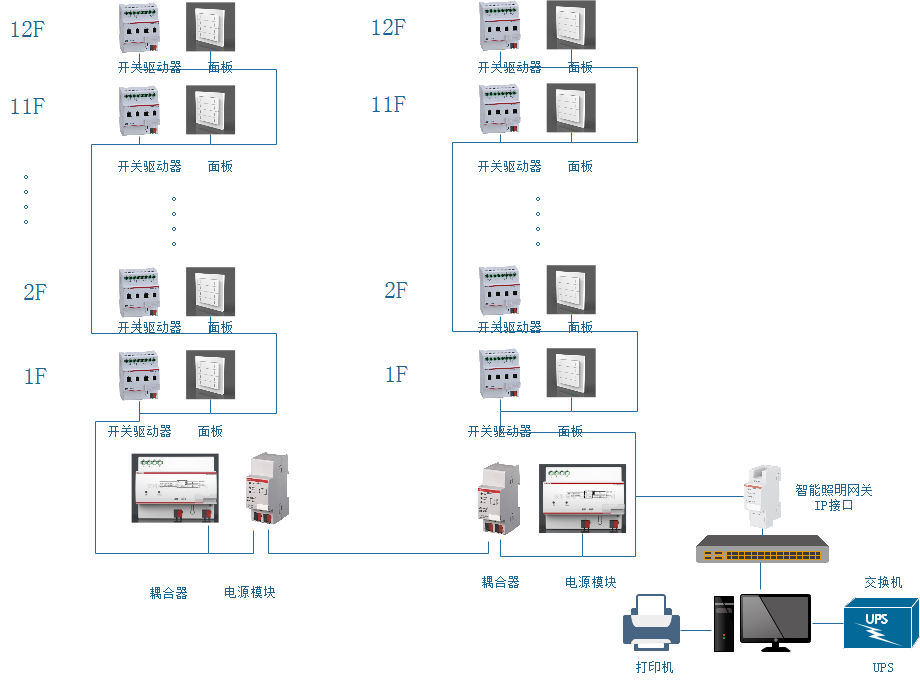

上圖是本項(xiàng)目整體的簡圖,包括4個(gè)發(fā)送板、1個(gè)接收板和PC電腦。其中本項(xiàng)目主要實(shí)現(xiàn)提接收板功能。

接收板包括四片的DDR3、一個(gè)PCIE接口、四路光纖接口。當(dāng)然接收板上還有很多其他接口,但是對(duì)于我們的項(xiàng)目來講,主要的就是這三種接口。

接收卡通過PCIE接口,直接插到PC的插槽上,跟PC進(jìn)行相連。

發(fā)送板可以通過光纖口發(fā)送數(shù)據(jù),從接收板看來,可以認(rèn)為外部有四路光纖口,接受這四種光纖的數(shù)據(jù)。

本項(xiàng)目中,四路發(fā)送板,每一個(gè)發(fā)送板其實(shí)它是一個(gè)AD采集卡。每個(gè)發(fā)送板它大概有16路的AD的采集,采集好數(shù)據(jù)匯總通過光纖送到這個(gè)接收卡。

接收卡從光纖接受到數(shù)據(jù)后,把數(shù)據(jù)匯聚起來,做適當(dāng)?shù)奶幚砗螅瑢?shù)據(jù)保存到DDR3中,等待被讀出送給PCIE接口,然后上送給PC電腦 ,這個(gè)就是我們整體的功能。

第三章 FPGA架構(gòu)

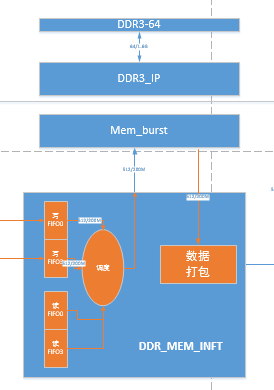

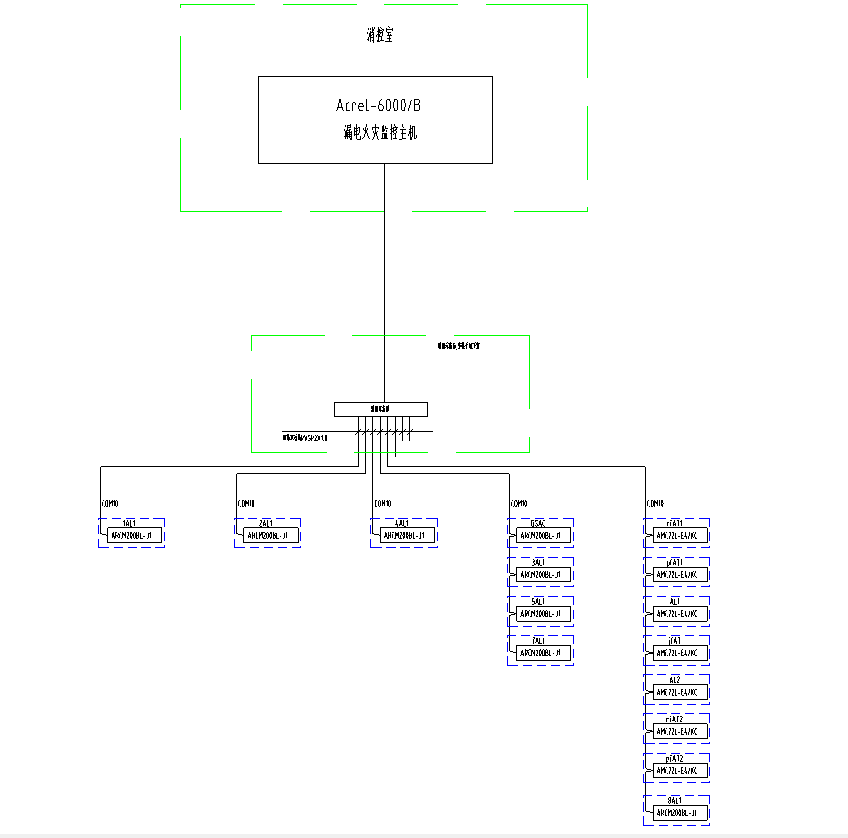

上圖是FPGA的內(nèi)部實(shí)現(xiàn)架構(gòu)。根據(jù)功能,可以大概劃分成光纖功能、存儲(chǔ)控制功能、PCIE功能三大部分。

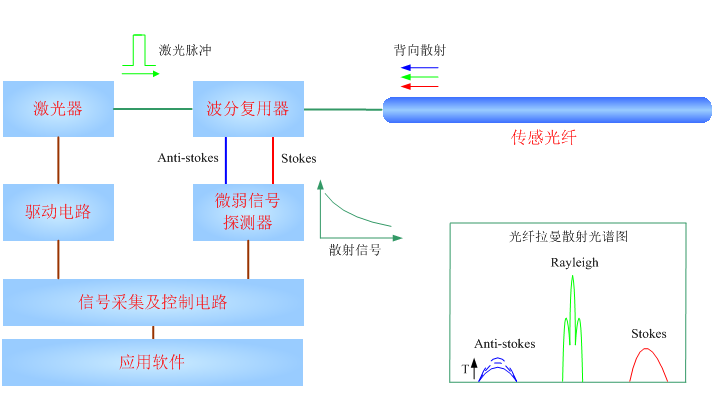

第1節(jié) 光纖功能

本項(xiàng)目通過光纖模塊,實(shí)現(xiàn)接收板和發(fā)送板的通信,通信速率是2.5Gbps,采用XILINX的官方IP核:7 Series FPGAs Transceivers Wizard(以下簡稱:GTX IP核)。關(guān)于該IP核的設(shè)置,有興趣的讀者,可以閱讀我們之前發(fā)表的文章《XILINX(K7)和CycloneV之間的光纖通信設(shè)置》一文。

由于使用到4路光纖,在設(shè)置高速收發(fā)器IP核 時(shí),注意要生成4路通道。當(dāng)生成后,每路通道給用戶側(cè)的數(shù)據(jù)發(fā)送接口只有兩個(gè):發(fā)送數(shù)據(jù)tx_data和K碼指示tx_kchar。同理,接收方向則是rx_data和rx_kchar。

我們注意到,數(shù)據(jù)接口只有數(shù)據(jù)和K碼指示,而不是明德?lián)P常見的包文形式。事實(shí)上,兩個(gè)較高級(jí)的設(shè)備之間通信,一般就是采用包文的形式,一次發(fā)一組數(shù)據(jù),每組數(shù)據(jù)可以達(dá)到幾千字節(jié)。為實(shí)現(xiàn)分組發(fā)送,特自定義了光纖協(xié)議層包文格式,如下表。

包文頭數(shù)據(jù)長度校驗(yàn)和無效值數(shù)據(jù)

16位16位16位16位數(shù)據(jù)長度個(gè)數(shù)據(jù)

上面是光纖協(xié)議層的包文格式,其有一個(gè)16位的包文頭(固定為0x55d5),一個(gè)16位的長度指示(指示后面數(shù)據(jù)的長度,單位為字節(jié)),一個(gè)16位的校驗(yàn)碼,一個(gè)16位的無效值,以及數(shù)據(jù)。

在FPGA內(nèi)部架構(gòu)圖中的光纖打包模塊,當(dāng)從上游模塊收到一個(gè)包文時(shí),就計(jì)算該包文的長度、校驗(yàn)和,然后產(chǎn)生包文頭+數(shù)據(jù)長度+校驗(yàn)和+無效值字段,再加上輸入的包文數(shù)據(jù),送給GXT IP核。GTX IP核再通過光纖送給發(fā)送板。

同理,發(fā)送板那里,也應(yīng)該有一個(gè)打包模塊,其要發(fā)送數(shù)據(jù)給接收卡,就會(huì)將包文封裝成上面格式,再通過光纖傳輸?shù)浇邮瞻濉=邮瞻鍙腉TX IP核接收數(shù)據(jù),在光纖解包模塊中,搜索包文頭55D5。如果搜索到包文頭,下一狀態(tài)就獲取數(shù)據(jù)長度和校驗(yàn)和。根據(jù)數(shù)據(jù)長度,接收后面的數(shù)據(jù)。邊接收數(shù)據(jù)邊計(jì)數(shù)數(shù)據(jù)的校驗(yàn)和。當(dāng)接收數(shù)據(jù)完畢,校驗(yàn)和也計(jì)算完了。這個(gè)時(shí)候,就對(duì)比收到的校驗(yàn)和與計(jì)算的校驗(yàn)和,是否相同。如果相同,說明包文是正確的;如果不同,說明包文是錯(cuò)誤的。

上面就是光纖的基本功能,主要涉及到光纖打包、光纖解包等。

事實(shí)上,如果光纖采用的是Aurora協(xié)議,那么推薦采用另一個(gè)IP核:Aurora 8B10B。這個(gè)IP核使用AXI4-stream總線接口,并且已經(jīng)是包文的格式。因此使用起來更加簡單。

第2節(jié) 存儲(chǔ)控制功能

本項(xiàng)目接收光纖數(shù)據(jù)后,首先會(huì)保存到DDR3中,等存夠一定數(shù)據(jù)時(shí),讀出數(shù)據(jù),送到PCIE。

接收板一共有4片DDR3,每片DDR3的數(shù)據(jù)位寬是16位。要注意的是,雖然有4片DDR4,但這4片DDR3不是各自獨(dú)立工作的。在硬件設(shè)計(jì)時(shí),將DDR3的地址線、控制線共用,數(shù)據(jù)線分開。也就是說,4片DDR3同時(shí)進(jìn)行讀寫,對(duì)FPGA來說,這相當(dāng)于一片64位的DDR3。

由于光纖數(shù)據(jù)一共有4路,并且4路數(shù)據(jù)都同時(shí)過來的,但只有一片64位的DDR3,如果不做處理,必須會(huì)有沖突。所以必須要做一個(gè)調(diào)度模塊:4路光纖數(shù)據(jù),首先會(huì)保存到內(nèi)部的寫FIFO中;調(diào)度模塊判斷4路FIFO的空閑情況,從而決定讀取哪一路數(shù)據(jù),存到DDR3中。沒有被讀取的,則繼續(xù)保存在FIFO中,直到被調(diào)度出來。

在設(shè)計(jì)調(diào)度模塊時(shí),要注意如下幾點(diǎn):

a.調(diào)度的優(yōu)先級(jí)

一共有4路數(shù)據(jù),那么調(diào)度器的優(yōu)先級(jí)如何選擇,即如果4路中有多于1路均同時(shí)有數(shù)據(jù),那么該如何選擇哪一路。例如,您可以指定第0~3路優(yōu)先級(jí)依次由高變低,即當(dāng)?shù)?路有數(shù)據(jù),一定選擇0路;當(dāng)?shù)?路沒有數(shù)據(jù)了,再?zèng)Q定看下一路。當(dāng)采用此方式時(shí),就要考慮是否存在如下情況:第0路一直有數(shù)據(jù),導(dǎo)致其他路一直無法讀出送到DDR3呢,這是要思考的問題。

b.調(diào)度的單位

調(diào)度的單位是指:選擇了一路數(shù)據(jù)后,會(huì)讀取多少個(gè)數(shù)據(jù)才結(jié)束。可供選擇是1個(gè)數(shù)據(jù)、多個(gè)數(shù)據(jù),或者是讀到FIFO空為止。這里要思考的是,1個(gè)數(shù)據(jù)最靈活,但是最繁瑣,會(huì)出現(xiàn)頻率調(diào)度的情況;如果是越多的數(shù)據(jù),調(diào)度沒有那么繁瑣了,但也意味著寫FIFO要臨時(shí)存比較多的數(shù)據(jù)才行,所以這里要有一個(gè)平衡。

c.調(diào)度的起啟水線

調(diào)度的起啟水線:當(dāng)FIFO存夠多少個(gè)數(shù)據(jù),才可以被調(diào)度器調(diào)度。這個(gè)是要考慮DDR的寫速度、光纖的輸入速度、以及調(diào)度單位的。例如,如果調(diào)度單位為1024個(gè)數(shù)據(jù),起啟水線100,當(dāng)DDR寫速度比光纖速度快時(shí),就可能會(huì)存在DDR寫到一半時(shí),新的數(shù)據(jù)還沒有來的情況。

當(dāng)然,最省事的,就是將起啟水線設(shè)置為跟調(diào)度單位一樣,這樣就絕對(duì)不存在問題,但這會(huì)存在一定的浪費(fèi)。為什么呢?我們?cè)O(shè)想如下場景,當(dāng)往DDR寫數(shù)據(jù)的同時(shí),光纖也會(huì)同時(shí)有新的數(shù)據(jù)送到寫FIFO。我們可以計(jì)算DDR的寫速度,以及新數(shù)據(jù)輸入速度,根據(jù)速度差,得到起啟水線。最理想的情況,就是當(dāng)最后一個(gè)數(shù)據(jù)寫到FIFO時(shí),剛好也 要將該數(shù)據(jù)寫到DDR,然后調(diào)度結(jié)束。這樣做的好處,就是將FIFO的深度設(shè)置為最適合的大小,從而節(jié)省資源。

在FPGA領(lǐng)域,貌似還不能理解FIFO深度多一點(diǎn)或者少一點(diǎn)有什么所謂。但在芯片設(shè)計(jì)領(lǐng)域則是經(jīng)常考慮的點(diǎn)。筆者在做芯片設(shè)計(jì)時(shí),經(jīng)常要花很多精力去計(jì)算出最省資源的方案。其實(shí)這也說明了FPGA設(shè)計(jì)和芯片設(shè)計(jì)的區(qū)別,區(qū)別是做得更細(xì)、設(shè)計(jì)得更好。

by the way,就如我一直在強(qiáng)調(diào)的,F(xiàn)PGA和芯片是一個(gè)講究做“細(xì)節(jié)”的技術(shù),很多人可以做很粗的功能,但很少人可以做很細(xì)的功能,例如圖像顯示很多人都會(huì),但用較少資源來實(shí)現(xiàn)圖像顯示,那就不會(huì)了。

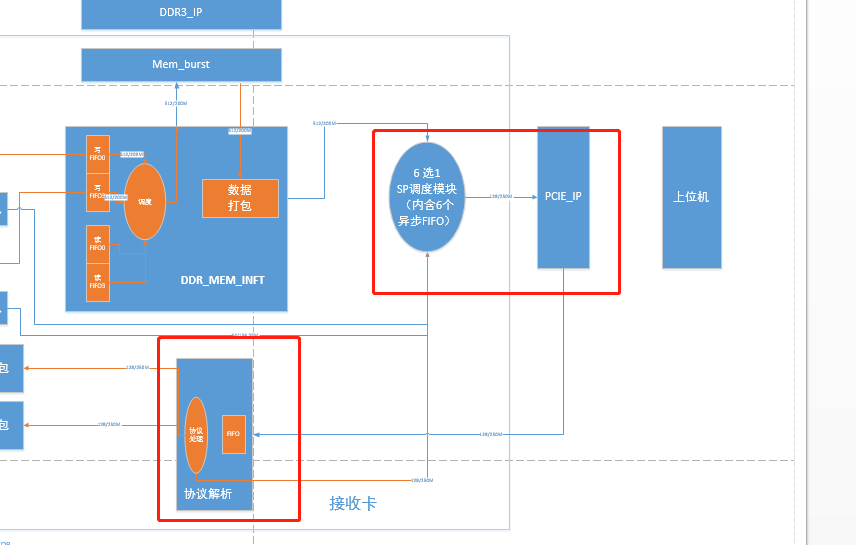

第3節(jié) PCIE功能

PCIE實(shí)現(xiàn)FPGA與上位機(jī)通信的功能,通信包文有兩種,一種是業(yè)務(wù)包文,一種是配置包文。

配置包文是用來對(duì)接收卡、發(fā)送卡內(nèi)的寄存器讀寫的包文。例如上位機(jī)對(duì)接收卡通道的開戶和關(guān)閉,對(duì)發(fā)送卡的數(shù)據(jù)收發(fā)控制、上位機(jī)讀取接收卡的內(nèi)部狀態(tài)等,均是由配置包文來實(shí)現(xiàn)的。

業(yè)務(wù)包文是指發(fā)送卡里的AD采集的數(shù)據(jù),是真正上位機(jī)要保存的數(shù)據(jù)。

下面上位機(jī)和FPGA的通信格式。

|

包文類型 (16b) |

讀寫屬性 (1b) |

板卡編號(hào) (15b) |

寄存器地址 (16b) |

寄存器數(shù)據(jù) (32b) |

無效填充 (48b) |

包文類型:用來指示是業(yè)務(wù)包文還是配置包文。業(yè)務(wù)包文的包文類型為16'h55AA;配置包文的類型為16'hF8F8。

讀寫屬于:用于上位機(jī)指示對(duì)FPGA的寄存器進(jìn)行寫,還是讀其值 。

板卡編號(hào):用來指示當(dāng)前包文是對(duì)哪個(gè)板卡進(jìn)行配置,可以理解為設(shè)備地址。例如是對(duì)接收卡或具體的一個(gè)發(fā)送卡進(jìn)行寄存器讀取。編號(hào)為0~3表示發(fā)送板0~3,編號(hào)4為接收卡。

寄存器地址:這個(gè)可以理解 為寄存器地址。

寄存器數(shù)據(jù):對(duì)寄存器配置的數(shù)據(jù),如果是讀的話,則填0。

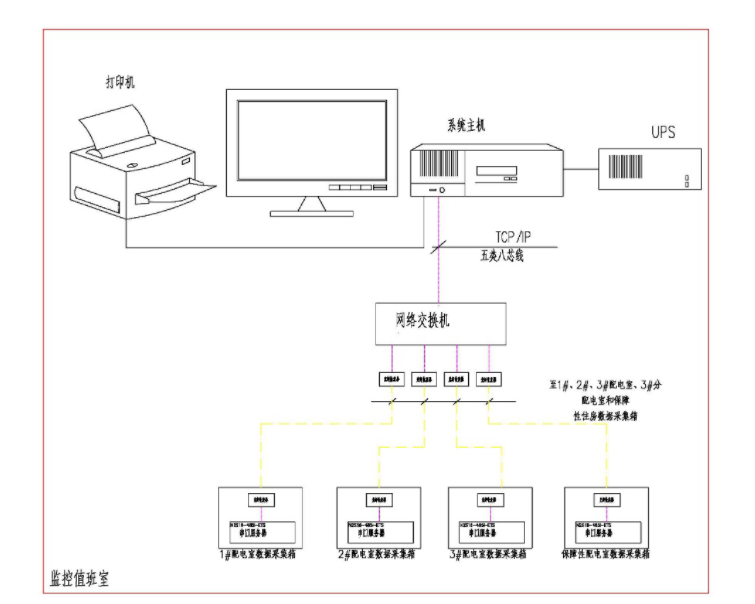

上位機(jī)當(dāng)要配置或者讀取寄存器時(shí),會(huì)按格式產(chǎn)生一個(gè)配置包文,通過PCIE傳給FPGA。FPGA的內(nèi)部有一個(gè)PCIE IP核。該IP核支持AXI4并且是包文形式,從PCIE里接收到包文數(shù)據(jù),并送往協(xié)議解析模塊。

協(xié)議解析模塊分析該包文,特別是對(duì)包文編號(hào)進(jìn)行識(shí)別。根據(jù)編號(hào),如果是接收卡配置包文,則直接對(duì)內(nèi)部的寄存器進(jìn)行讀取;如果是某一路發(fā)送板配置包文,則將該包文轉(zhuǎn)發(fā)到該路光纖接口。

如果是讀取寄存器數(shù)據(jù),則會(huì)將配置包文返回給上位機(jī),具體路徑是:協(xié)議解析模塊處理后,將寄存器數(shù)據(jù)補(bǔ)充到包文的數(shù)據(jù)域,然后讀該包文轉(zhuǎn)給6選1 SP調(diào)度模塊。在該調(diào)度模塊中,從6路包文(1路是業(yè)務(wù)包文,1路是接收卡返回的配置包文,其他4路是4個(gè)光纖返回的配置包文),選取一路發(fā)給PCIE IP核。

上位機(jī)從包文類型中,識(shí)別出業(yè)務(wù)包文還是配置包文,做相對(duì)應(yīng)的處理。

審核編輯:湯梓紅

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論