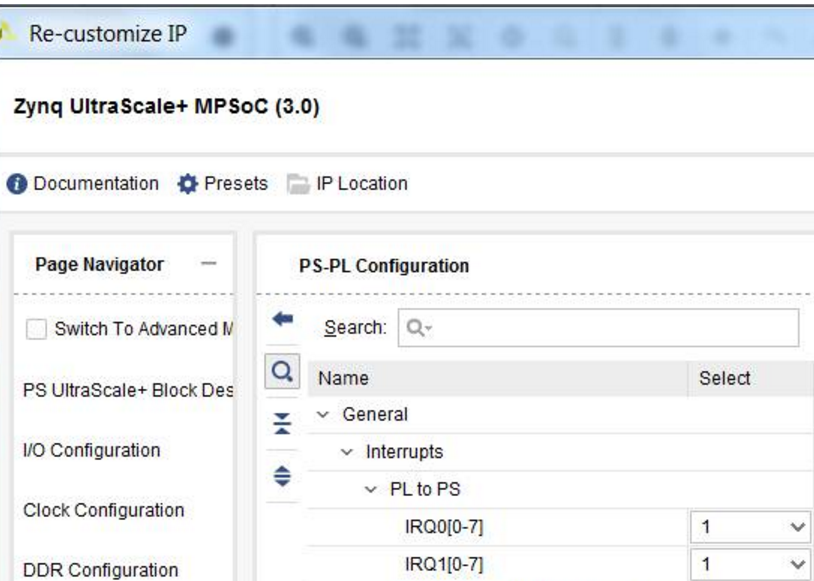

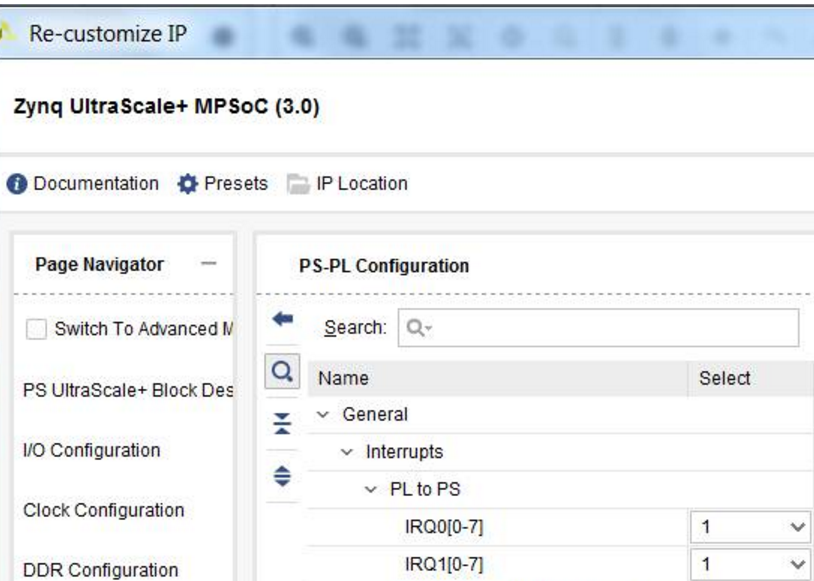

硬件連接MPSoC 可以接收兩組來自 PL 的中斷信號(hào)。在 Vivado 中,可以通過 PS-PL Conf

2017-09-28 06:39:00 9219

9219

。 Pynq降低了開發(fā)人員的門檻,但知其然也知其所以然,開發(fā)效率將會(huì)更高。因此,在進(jìn)入PYNQ的python開發(fā)之前,我們先來學(xué)習(xí)ZYNQ的PL與PS開發(fā),為接下來的學(xué)習(xí)提供良好的基礎(chǔ)。 本部分的學(xué)習(xí)

2020-12-25 14:11:50 6842

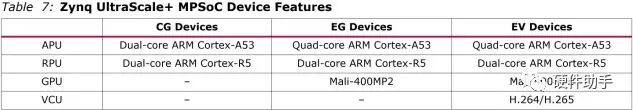

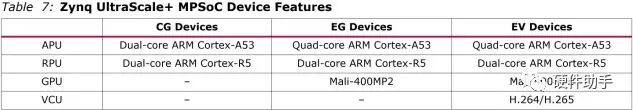

6842 本篇主要介紹ZU+系列MPSoC的外圍接口,針對(duì)每個(gè)接口進(jìn)行概述性介紹,后續(xù)會(huì)針對(duì)個(gè)別接口進(jìn)行詳細(xì)介紹原理圖設(shè)計(jì)和PCB設(shè)計(jì)。 ZU+系列MPSoC的外圍接口主要包括兩部分:PL部分和PS部分。PL

2020-12-26 10:04:38 4310

4310

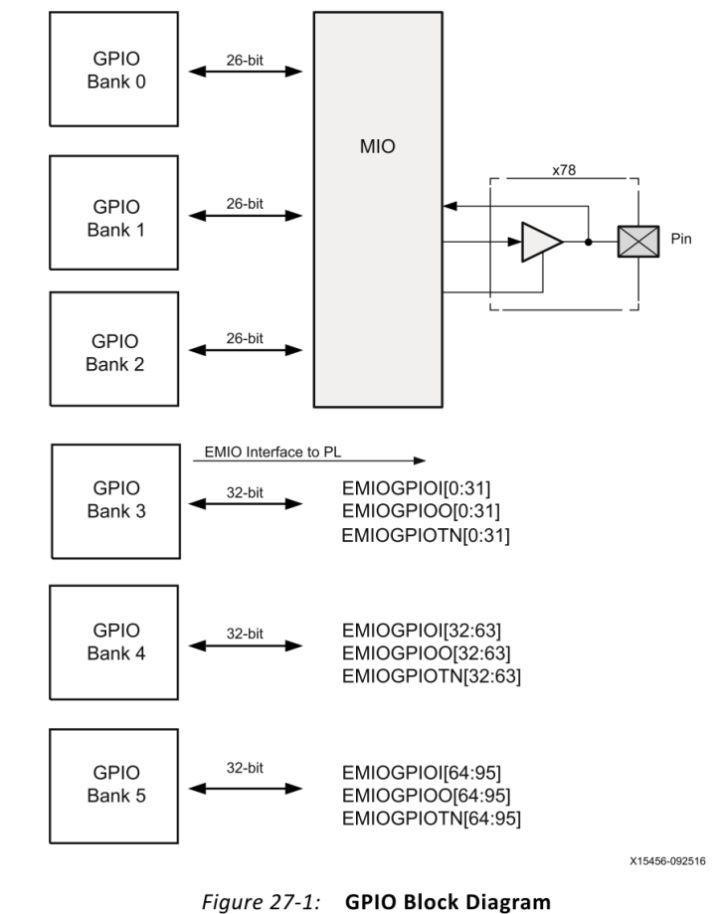

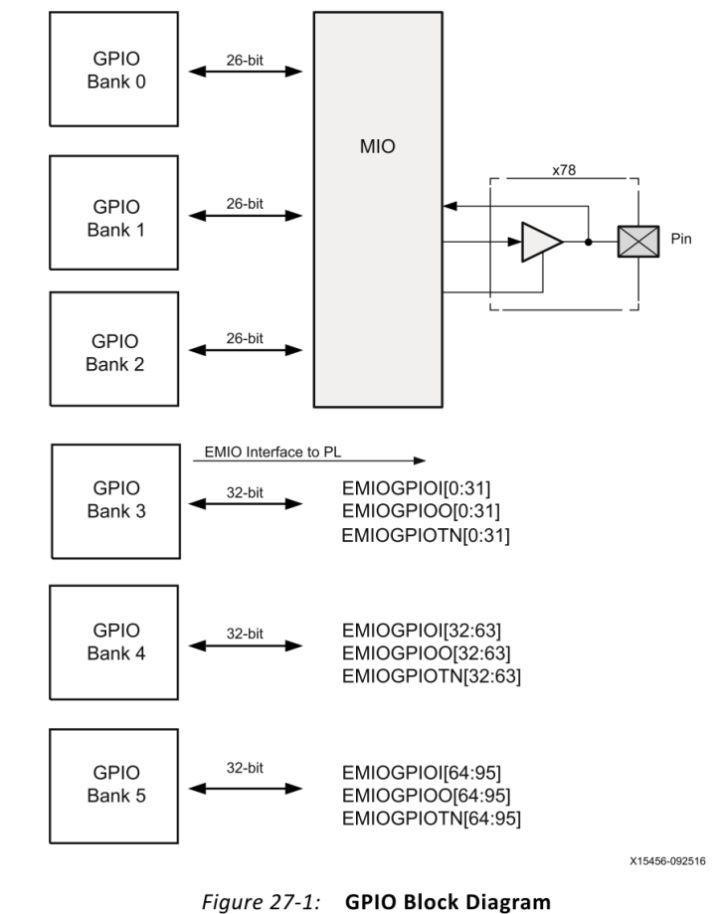

如果想用PS點(diǎn)亮PL的LED燈,該如何做呢?一是可以通過EMIO控制PL端LED燈,二是通過AXI GPIO的IP實(shí)現(xiàn)控制。本章介紹如何使用EMIO控制PL端LED燈的亮滅。同時(shí)也介紹了,利用EMIO連接PL端按鍵控制PL端LED燈。

2021-01-30 10:05:00 6730

6730

使用zynq最大的疑問就是如何把PS和PL結(jié)合起來使用,在其他的SOC芯片中一般都會(huì)有GPIO,本實(shí)驗(yàn)使用一個(gè)AXI GPIO的IP核,讓PS端通過AXI總線控制PL端的LED燈,實(shí)驗(yàn)雖然簡(jiǎn)單,不過可以讓我們了解PL和PS是如何結(jié)合的。

2021-02-01 10:06:00 6182

6182

PL和PS的高效交互是zynq soc開發(fā)的重中之重,我們常常需要將PL端的大量數(shù)據(jù)實(shí)時(shí)送到PS端處理,或者將PS端處理結(jié)果實(shí)時(shí)送到PL端處理,常規(guī)我們會(huì)想到使用DMA的方式來進(jìn)行,但是各種協(xié)議非常

2021-01-30 09:54:00 12916

12916

有時(shí)CPU需要與PL進(jìn)行小批量的數(shù)據(jù)交換,可以通過BRAM模塊,也就是Block RAM實(shí)現(xiàn)此要求。本章通過Zynq的GP Master接口讀寫PL端的BRAM,實(shí)現(xiàn)與PL的交互。在本實(shí)驗(yàn)中加入了自定義的FPGA程序,并利用AXI4總線進(jìn)行配置,通知其何時(shí)讀寫B(tài)RAM。

2021-02-22 13:51:00 7359

7359

/p/005899fe6815 二、ZYNQ7020 分為PS端、PL端 PS: 處理系統(tǒng) (Processing System) , 就是與 FPGA 無關(guān)的 ARM 的 SOC 的部分。 PL: 可編程邏輯

2021-05-12 10:25:31 13958

13958

本文主要介紹ZYNQ PS + PL異構(gòu)多核案例的使用說明,適用開發(fā)環(huán)境:Windows 7/10 64bit、Xilinx Vivado 2017.4、Xilinx SDK 2017.4

2021-09-07 17:03:30 2880

2880

MPSoC有六個(gè)PL側(cè)高性能(HP)AXI主接口連接到PS側(cè)的FPD(PL-FPD AXI Masters),可以訪問PS側(cè)的所有從設(shè)備。這些高帶寬的接口主要用于訪問DDR內(nèi)存。有四個(gè)HP AXI

2022-07-22 09:25:24 2501

2501 在Zynq MPSoC的器件里,PS (Processing System )集成了三個(gè)看門狗,分別是CSU SWDT,LPD SWDT和FPD SWDT。

2023-06-30 09:47:22 851

851

xilinx mpsoc 平臺(tái)中,PS 和 PL 進(jìn)行交互時(shí),PS 需要獲取 PL 發(fā)出的中斷信號(hào)。從 mpsoc 技術(shù)參考手冊(cè) ug1085 TRM 中可知,PL 給到 PS 的中斷有兩組

2023-08-24 16:06:22 560

560

大家好,我似乎遇到了與MPSoC交互的UART接口問題。在遵循系統(tǒng)控制器GUI教程(XTP433)時(shí),我似乎無法連接到MP。波特率設(shè)置為115200.當(dāng)嘗試設(shè)置Si5328頻率時(shí),軟件超時(shí)且無法設(shè)置

2019-10-09 07:03:27

實(shí)驗(yàn)15_i2c時(shí)序及EEPROM介紹16_i2c EEPROM及溫度傳感器控制實(shí)驗(yàn)17_PS端DP接口顯示實(shí)驗(yàn)18_SD原理介紹19_SD卡TXT文件讀寫實(shí)驗(yàn)20_SD卡Bmp圖片顯示實(shí)驗(yàn)21_

2022-07-21 10:34:51

中的片內(nèi)外設(shè)。AXI-HP接口(4個(gè)):是高性能/帶寬的標(biāo)準(zhǔn)的接口,PL模塊作為主設(shè)備連接(從下圖中箭頭可以看出)。主要用于PL訪問PS上的存儲(chǔ)器(DDR和On-Chip RAM)AXI-ACP接口

2018-01-08 15:44:39

、Xilinx Vivado 2017.4、Xilinx SDK 2017.4。案例包含PL端Vivado工程,主要使用Xilinx提供的標(biāo)準(zhǔn)IP核配置PL端資源實(shí)現(xiàn)接口擴(kuò)展,同時(shí)包含PS端裸機(jī)

2021-05-28 14:28:28

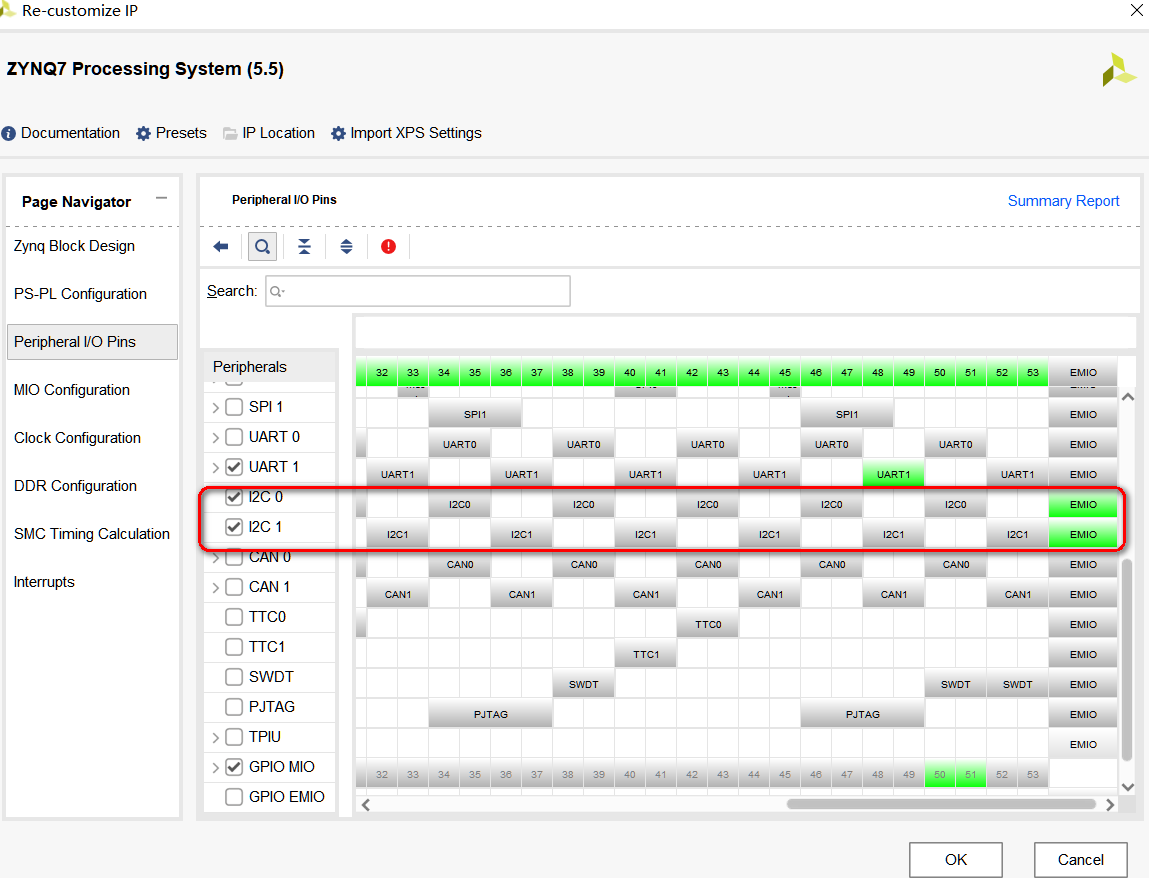

ZYNQ PS端IIC接口使用筆記

2021-02-23 06:23:31

ZYNQ Ultrascale+ MPSOC FPGA教程

2021-02-02 07:53:25

建立這部分請(qǐng)參考我上篇講述搭建操作系統(tǒng)的文章二、VIVADO工程設(shè)置zynq核的搭建也請(qǐng)參照上篇文章,不過需要增加一些內(nèi)容;雙擊zynq核,進(jìn)入zynq的配置;選擇PS-PL Configuration,選中General—>Enable Clock Resets—>FCLK_RESET

2021-12-17 06:42:06

Linux主機(jī)測(cè)試CDC功能履行實(shí)施細(xì)節(jié)設(shè)計(jì)類型僅PSSW類型Zynq?UltraScale+?MPSoC Linux操作系統(tǒng)CPU的ARM Cortex A53 Core 0以1.1 GHz運(yùn)行PS

2019-01-03 09:59:50

嗨,我必須找出zynq 7020 PS和zynq PL如何通話,特別是我必須找到將在ARM中處理的SDK C代碼。你能用一個(gè)明確的C代碼告訴我,它解釋了數(shù)據(jù)如何從PS轉(zhuǎn)移到PL,這是ARM用來做這個(gè)的基本程序嗎?謝謝

2020-05-08 09:37:11

本帖最后由 blackroot 于 2015-6-10 17:06 編輯

一直沒搞懂PS怎樣給PL提供復(fù)位和時(shí)鐘,今天這個(gè)問題終于解決了~~~~~用一個(gè)簡(jiǎn)單的例子來說明一下,怎樣使用PS輸出

2015-06-10 16:59:53

在板子上除了給PS(33.33 MHz)、DDR、SPI FLASH、microSD卡接口和USB提供時(shí)鐘信號(hào)外,并沒有為PL部分提供單獨(dú)的晶振。為了讓PL部分正常工作,一種方法是使用接口板從外部

2015-06-01 11:54:12

”實(shí)驗(yàn)》的步驟2-10中,移除了PS中與PL端交互的接口信號(hào),這些接口在我們本次實(shí)驗(yàn)中需要予以保留。最后點(diǎn)擊右下角的“OK”,本次實(shí)驗(yàn)ZYNQ處理系統(tǒng)就配置完成了。ZYNQ7 PS配置完成后其接口如圖

2020-09-04 11:08:46

。 ZYNQ MPSoC芯片的總體框圖 PS: 處理系統(tǒng)(Processing System) , 就是與FPGA無關(guān)的ARM的SoC的部分。 PL: 可編程邏輯 (Progarmmable

2021-01-07 17:11:26

我想給板子接上一個(gè)u***接口的鍵盤,不跑操作系統(tǒng),只用ps部分接收鍵盤的數(shù)據(jù)然后傳遞給PL,不知道如何編寫sdk的代碼來跟u***的phy通信呢?有沒可以參考的例程或者文檔?

2015-12-16 17:12:38

本文介紹了一種基于MPSoC的以太網(wǎng)接口設(shè)計(jì)方案。

2021-05-19 07:22:17

賽靈思和 DornerWorks 的系統(tǒng)軟件團(tuán)隊(duì)在賽靈思的 Zynq? Ultrascale+? MPSoC 上啟動(dòng) Xen Project 管理程序時(shí),我們發(fā)現(xiàn)可通過運(yùn)行當(dāng)年叱詫一時(shí)的流行電子游戲

2019-10-09 06:21:21

我的設(shè)備是zedboard702,我知道如何在使用PS和PL時(shí)使用SDK生成啟動(dòng)映像和程序閃存。問題是我只是使用PL,現(xiàn)在如何編程flash?

2019-09-30 09:43:18

親愛的大家,我只是想知道如何找到Ultrascale +的PL和PS的地址轉(zhuǎn)換(映射方案到DRAM-我的意思是哪個(gè)等級(jí),庫(kù)等)?

2019-10-16 08:35:37

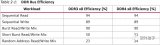

),并在高級(jí)選項(xiàng)卡中啟用高級(jí)流量生成器: DDR 應(yīng)用: 一旦 PHY 接口被驗(yàn)證,如果還會(huì)出現(xiàn)問題,請(qǐng)嘗試切換到 PS-DDR,看看問題是否還會(huì)繼續(xù)。 這將表明該問題是一個(gè) VCU 至內(nèi)存

2021-01-07 16:02:09

大家好,我已經(jīng)在PS中產(chǎn)生了一個(gè)100Mhz的時(shí)鐘信號(hào),并使其在外部被PL接收。我使用了原始的ODDR但沒有成功我可以從引腳輸出100 Mhz時(shí)鐘。有什么建議么??以上來自于谷歌翻譯以下為原文

2019-02-22 09:09:05

為什么一個(gè)簡(jiǎn)單的程序運(yùn)行不了,請(qǐng)求幫忙看一下。做個(gè)LED流水燈,是想用PS部分生成100MHz的頻率,然后用這個(gè)頻率來實(shí)現(xiàn)PL部分三色led移位,但是好像PS部分有問題,不知道怎么配置了。這是PS

2016-01-02 21:35:38

PS測(cè)試1、 QSPI加載2、 DDR3讀寫3、 EMMC讀寫4、 網(wǎng)口測(cè)試(RGMII接口)5、 USB轉(zhuǎn)串口收發(fā)測(cè)試2.MPSOC PL測(cè)試1、 KEY/LED/撥碼開關(guān)/PMOD測(cè)試2

2023-04-13 16:04:38

你好我們正在考慮在我們的新設(shè)計(jì)中使用Zynq Ultrascale + MPSOC。我們想在我們的電路板設(shè)計(jì)中加入HDMI接口。 Zynq Ultrascale + MPSOC在PS中有一個(gè)

2019-10-14 09:17:03

請(qǐng)問zynq 怎么實(shí)現(xiàn)PS與PL數(shù)據(jù)交互,然后通過UART串口打印出來?前輩們做過的指導(dǎo)我一下。

2020-08-03 15:53:30

XAPP1251說明顯示,可以在Zynq ARM處理器上運(yùn)行XVC服務(wù)器來控制FPGA中的JTAG端口。但是,我不清楚,是否可以在同一個(gè)FPGA中控制PL JTAG?可以使用運(yùn)行在設(shè)備PS部分上

2020-07-30 13:51:19

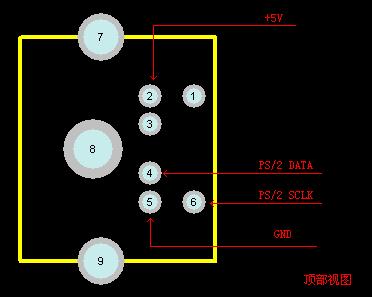

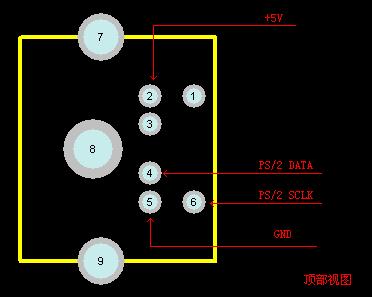

鼠標(biāo)有RS232串口和PS/2二種接口,在單片機(jī)應(yīng)用中,由于PS/2鼠標(biāo)是1yrL電平,和單片接口更方便,通常PS/2鼠標(biāo)控制芯片采用TP8452。以TP8452為例說明PS/2鼠標(biāo)的工作原理,其他

2008-10-22 23:00:22 121

121 RS232接口在嵌入式設(shè)備中應(yīng)用廣泛。為了充分利用USB接口即插即用的特點(diǎn),詳細(xì)介紹一種基于PL2303的RS232與USB轉(zhuǎn)換的設(shè)計(jì)方案。PL2303是高集成度的通用串行總線(USB)與串口的接口轉(zhuǎn)

2010-12-31 17:23:17 277

277

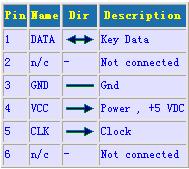

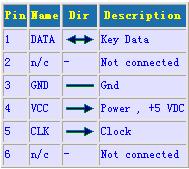

PS/2接口協(xié)議解析及應(yīng)用

2006-07-03 14:29:19 1928

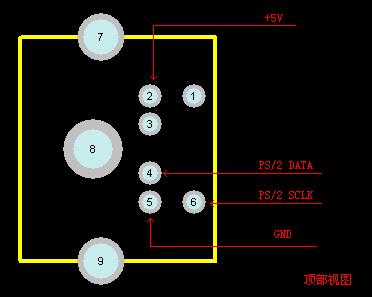

1928 ps 2接口定義圖

外觀為: &n

2007-11-19 17:25:36 6201

6201

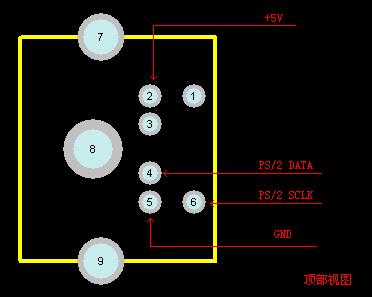

PS 2 鼠標(biāo)接口引腳定義圖

PS/2 鼠標(biāo)接口為 6 針母插,外觀為:

2007-11-27 12:34:52 18983

18983

PS2鍵盤接口引腳定義圖

PS/2 鍵盤接口為 6 針母插,外觀為:

2007-11-27 12:36:18 40828

40828

PS 2鼠標(biāo)接口轉(zhuǎn)串行鼠標(biāo)轉(zhuǎn)接器

本轉(zhuǎn)換口把一個(gè)串行鼠標(biāo)接到 PS/2 鼠標(biāo)口上,到鼠

2007-11-27 20:08:15 861

861

PS 2鍵盤接口轉(zhuǎn)普通鍵盤接口轉(zhuǎn)接器

本轉(zhuǎn)換口把一個(gè)普通鍵盤接到 PS/2 的鍵盤口上,PC 一側(cè)為 6 針 PS/2 公插頭:

2007-11-27 20:09:28 944

944

普通鍵盤接口轉(zhuǎn)PS 2鍵盤轉(zhuǎn)接器

本轉(zhuǎn)換口把一個(gè) PS/2 鍵盤接到普通鍵盤口上,到鍵盤一側(cè)為 6 針 PS/2 母插頭:

2007-12-04 12:38:42 781

781

PS/2 鍵盤接口定義PS/2 鍵盤接口為 6 針母插。Pin Name Description1 DATA Key Data2 n/c Not connected3 GND Gnd4 VCC +5 VDC5

2009-02-12 10:34:19 4139

4139 ps2的usb接口有什么用

PS2鍵盤鼠標(biāo)USB U盤接口,你用什么連接USB 接口啊? 如果你的是2000或XP 系統(tǒng), U盤直接插上就可以 如果是手機(jī)或MP3有的直接插可以但是

2009-05-03 22:05:26 4965

4965 什么是ps2接口 ps2接口是什么意思?

PS/2接口是目前最常見的鼠標(biāo)接口,最初是IBM公司的專利,俗稱“小口”。這是一種鼠標(biāo)和鍵

2009-05-03 22:07:26 24774

24774

什么是PS/2接口

很多老式的品牌機(jī)上采用PS/2口來

2010-01-22 12:21:57 2085

2085 什么是主板PS/2鼠標(biāo)接口

PS/2鼠標(biāo)接口:現(xiàn)今的一些流行的Pentium

2010-02-05 11:46:51 1379

1379 本文通過實(shí)例詳細(xì)解析如何利用Zynq-7000的PL和PS進(jìn)行交互。實(shí)際上,Zynq就是兩大功能塊:雙核Arm的SoC和FPGA。根據(jù)Xilinx提供的手冊(cè),PS: 處理系統(tǒng) (Processing System) , 就是與FPGA無關(guān)的A

2012-12-12 13:40:22 53204

53204

文中詳細(xì)介紹了PS/2接口協(xié)議的內(nèi)容、電氣特性和標(biāo)準(zhǔn)鍵盤的第二套鍵 盤掃描碼集。給出了基于嵌入式系統(tǒng)的PS/2接口的軟、硬件實(shí)現(xiàn)方法,并介紹了工控PC外接雙鍵盤的解決方案。

2016-03-25 15:25:53 17

17 針對(duì)標(biāo)準(zhǔn)的PS/2設(shè)備,實(shí)現(xiàn)了與單片機(jī)的接口,本文分析了PS/2鍵盤的接口和通訊議,介紹了PS/2鍵盤與單片機(jī)的接口設(shè)計(jì),并以8051為例,配合點(diǎn)陣LCD顯示器,實(shí)現(xiàn)了PS/2鍵盤的輸入,并進(jìn)一步探討了用PS/2鼠標(biāo)實(shí)現(xiàn)嵌入式設(shè)備的圖形化人機(jī)接口(GUI)。

2016-03-25 14:50:51 11

11 本篇文章詳細(xì)的介紹了介紹ps2接口協(xié)議及其典型應(yīng)用

2016-08-24 16:52:02 9

9 分享下PS與PL之間數(shù)據(jù)傳輸比較另類的實(shí)現(xiàn)方式,實(shí)現(xiàn)目標(biāo)是: 1、傳輸時(shí)數(shù)據(jù)不能滯留在一端,無論是1個(gè)字節(jié)還是1K字節(jié)都能立即發(fā)送; 2、PL端接口為FIFO接口; PS到PL的數(shù)據(jù)傳輸流程: PS

2017-02-08 01:00:11 1431

1431

端的GTR也是單獨(dú)供電的,還有還有,這個(gè)GTR的電壓竟然和PL端的GTH完全不同。圖4是Zynq-7000和Zynq UltraScale MPSoC電源系統(tǒng)的比較。 典型的是,內(nèi)核電壓由1.0V降至

2017-02-08 08:33:41 427

427

因?yàn)镸icroZed是個(gè)低成本的開發(fā)套件,所以在板子上除了給PS(33.3333 MHz)、DDR、SPI FLASH、microSD卡接口和USB提供時(shí)鐘信號(hào)外,并沒有為PL部分提供單獨(dú)的晶振。

2017-02-09 14:16:11 4135

4135

了解Zynq PS / PL接口之后;到目前為止,我們已經(jīng)分析了Zynq All Programmable SoC芯片中的PS (處理器系統(tǒng))與PL(可編程邏輯)之間的接口。

2017-02-10 12:00:11 956

956

我們先來了解一下上節(jié)中介紹的Zynq SoC PS/PL接口,我創(chuàng)建一個(gè)很簡(jiǎn)單的外設(shè),使用的是DSP48E1的DSP邏輯片,依靠這個(gè)外設(shè)第一個(gè)寄存器內(nèi)的控制字執(zhí)行乘法,加法或減法。

2017-02-10 12:04:41 469

469

構(gòu)建SoC系統(tǒng),畢竟是需要實(shí)現(xiàn)PS和PL間的數(shù)據(jù)交互,如果PS與PL端進(jìn)行數(shù)據(jù)交互,可以直接設(shè)計(jì)PL端為從機(jī),PS端向PL端的reg寫入數(shù)據(jù)即可,本節(jié)研究如何再實(shí)現(xiàn)PL端對(duì)DDR3的讀寫操作。

2017-09-18 11:08:55 23

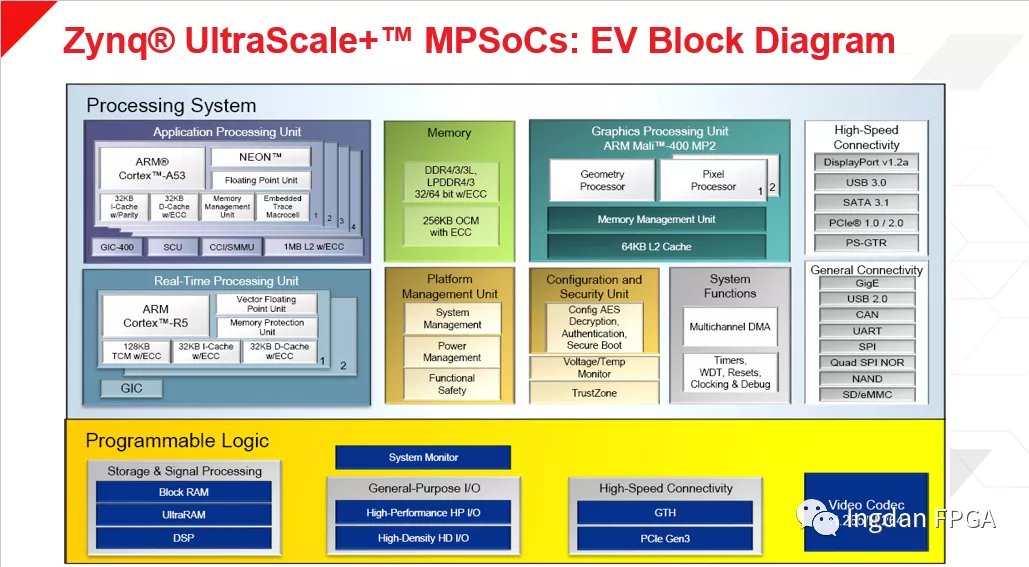

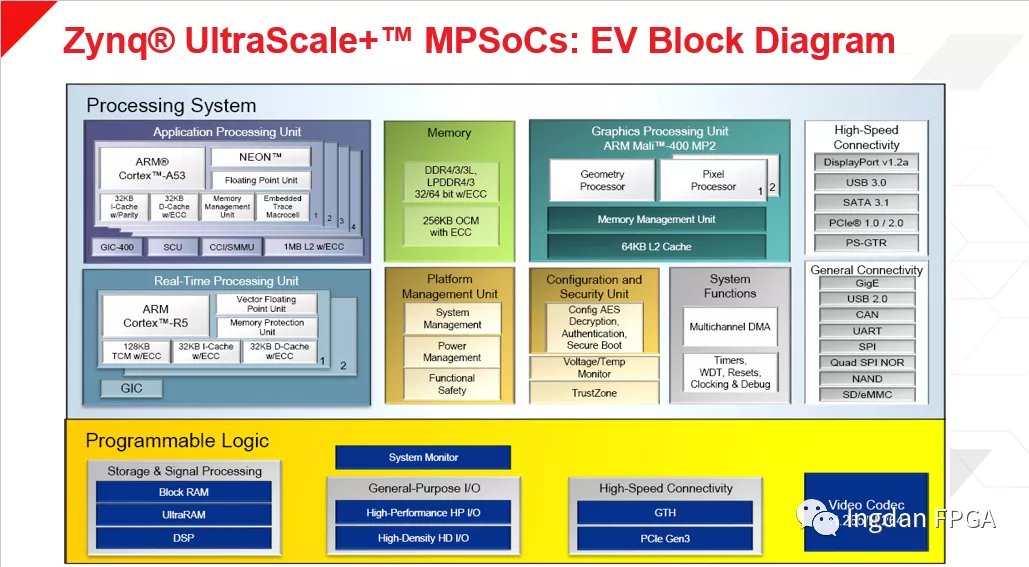

23 應(yīng)用程序完成測(cè)試。ZCU102上的MPSOC集成固化了四核ARMCortex-A53,雙核Cortex-R5以及Mali-400 MP2 GPU,這部分官方稱為PS(processor system)。另外

2017-11-15 14:46:59 13661

13661

的文章,在此分享。 當(dāng)我們?cè)谠O(shè)計(jì)中使用Zynq SoC或Zynq UltraScale + MPSoC時(shí),可以有兩種方法來實(shí)現(xiàn)SPI接口: 1. 使用PS端的SPI控制器(PS端有兩個(gè)SPI控制器

2017-12-30 05:03:45 5104

5104

iVeia演示了將Android操作系統(tǒng)移植到Zynq UltraScale + MPSoC上,以獲取角落和邊緣檢測(cè)濾波器的實(shí)時(shí)視頻和控制系數(shù)。

結(jié)果是使用軟件仿真器QEMU實(shí)現(xiàn)更快的從PS到PL的算法

2018-11-26 06:57:00 4838

4838 Cortex-A53和雙核ARM Cortex-R5處理系統(tǒng)(PS)以及Xilinx可編邏輯(PL)UltraScale架構(gòu);此外還集成了片上存儲(chǔ)器,多端口外接存儲(chǔ)器接口,以及豐富的外設(shè)連接接口.處理單元

2018-12-11 18:17:01 1206

1206 Zynq在PS和PL之間有9個(gè)AXI接口。

2018-12-30 09:45:00 6907

6907 和基于雙核ARM Cortex-R5的處理系統(tǒng)(PS)和Xilinx可編程邏輯(PL)超尺度架構(gòu)。還包括片上存儲(chǔ)器、多端口外部存儲(chǔ)器接口和一組豐富的外圍連接接口。

2019-02-20 15:57:46 10

10 和基于雙核ARM Cortex-R5的處理系統(tǒng)(PS)和Xilinx可編程邏輯(PL)的超尺度結(jié)構(gòu)。還包括片上存儲(chǔ)器、多端口外部存儲(chǔ)器接口和一組豐富的外圍連接接口。

2019-02-21 16:48:54 19

19 Zynq UltraScale+ MPSoC是Xilinx推出的第二代多處理SoC系統(tǒng),在第一代Zynq-7000的基礎(chǔ)上做了全面升級(jí),在單芯片上融合了功能強(qiáng)大的處理器系統(tǒng)(PS)和用戶可編程邏輯(PL)。Zynq UltraScale+ MPSoC系統(tǒng)框圖

2019-11-18 11:03:22 2539

2539

MPSoC是Xilinx基于16nm工藝推出的異構(gòu)計(jì)算平臺(tái),由于靈活、穩(wěn)定,在業(yè)界得到了廣泛的使用。異構(gòu)計(jì)算是一個(gè)比較新的領(lǐng)域,需要協(xié)調(diào)硬件設(shè)計(jì)、邏輯設(shè)計(jì)、軟件設(shè)計(jì),對(duì)工程師的要求很高。實(shí)際設(shè)計(jì)過程中,很多工程師對(duì)實(shí)現(xiàn)PS/PL之間的數(shù)據(jù)交互感到頭疼。

2020-09-15 09:27:00 11208

11208

工程師根據(jù)FSBL的main.c中的InitWatchDog( ),添加代碼后,依然不能使MPSoC的PS復(fù)位。

2020-09-19 11:15:06 1361

1361

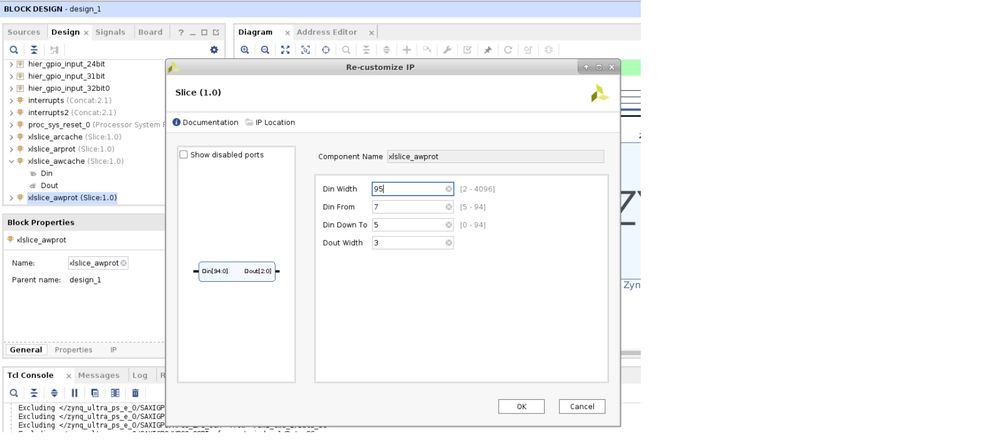

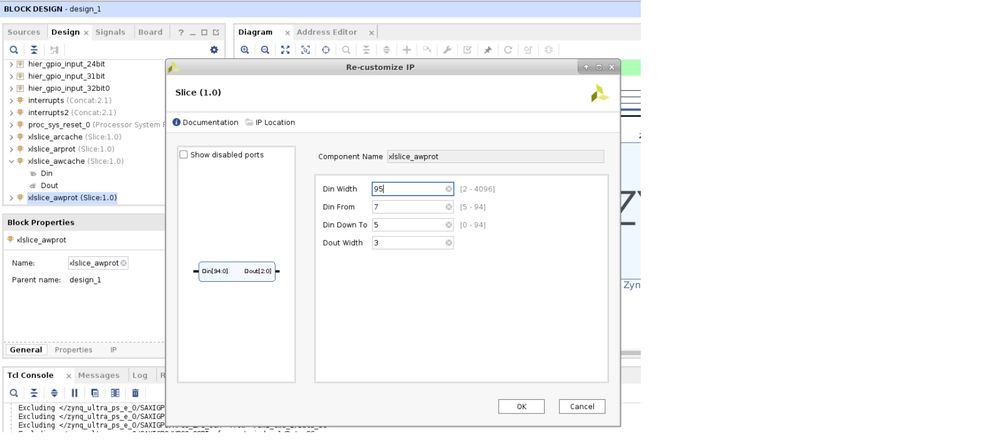

MPSoC 為PL提供了96個(gè)GPIO,通過EMIO管腳鏈接到PL。 普通PL設(shè)計(jì),一般只會(huì)用到幾個(gè)GPIO管腳。可以使用Vivado IPI中的Slice IP, 從其中分出指定數(shù)量的管腳

2020-11-04 14:57:17 1499

1499

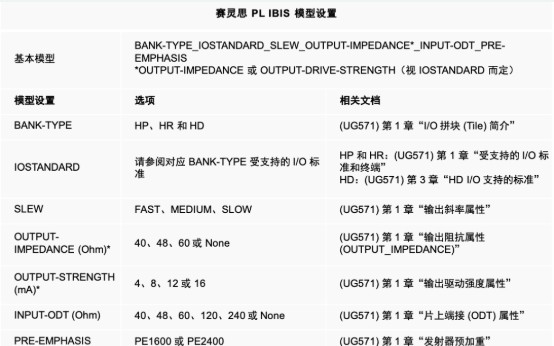

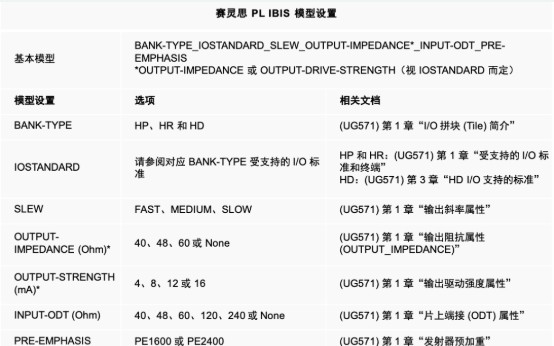

。 本篇博文旨在提供有關(guān)如何為可編程邏輯 (PL) 和處理器系統(tǒng) (PS) 多用途 I/O (MIO) 進(jìn)行 IBIS 模型名稱解碼的指導(dǎo)信息。 本文主要分 3 個(gè)部分: PL I/O 標(biāo)準(zhǔn) PS MIO

2020-10-15 18:29:15 2145

2145

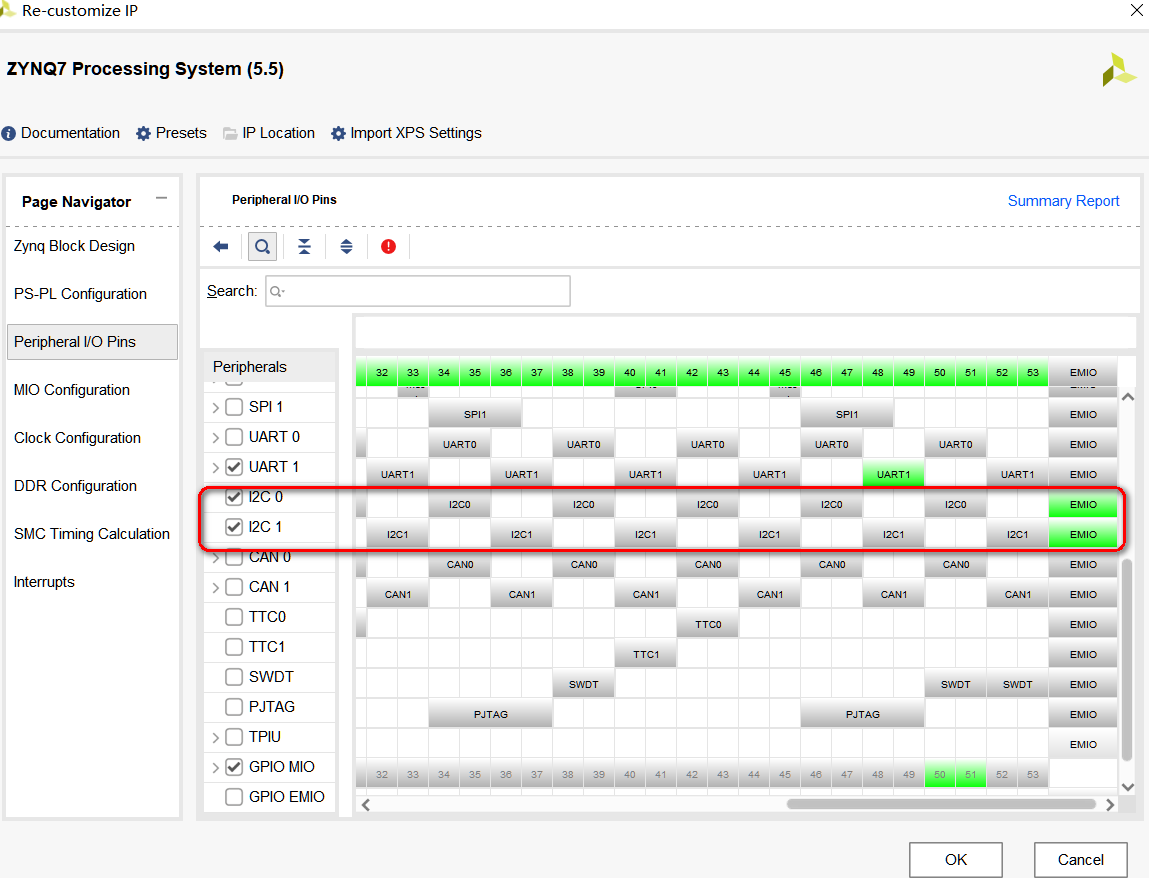

ZYNQ7000系列FPGA的PS自帶兩個(gè)IIC接口,接口PIN IO可擴(kuò)展為EMIO形式即將IO約束到PL端符合電平標(biāo)準(zhǔn)的IO(BANK12、BANK13、BANK34、BANK35);SDK

2022-07-25 17:56:52 1404

1404

ZYNQ7000系列FPGA的PS自帶兩個(gè)IIC接口,接口PIN IO可擴(kuò)展為EMIO形式即將IO約束到PL端符合電平標(biāo)準(zhǔn)的IO(BANK12、BANK13、BANK34、BANK35);SDK

2021-01-28 08:05:27 25

25 FPGAs,Zynq 和 Zynq MPSoC! Zynq MPSoC是Zynq-7000 SoC(之后簡(jiǎn)稱Zynq)的進(jìn)化版本。Zynq是賽靈思發(fā)布的集成PL(FPGA)和PS設(shè)計(jì)的最早的一代產(chǎn)品

2021-04-02 17:20:14 13780

13780

目錄1. MPSoC的中斷處理介紹 2. 擴(kuò)展PL中斷 3. 擴(kuò)展AXI Intc中斷 3.1. AXI Intc PL連接 3.2. AXI Intc Device Tree 3.3. AXI

2021-05-07 15:34:15 3626

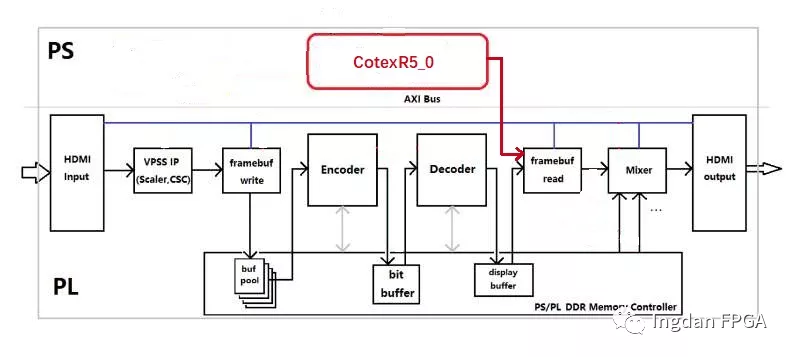

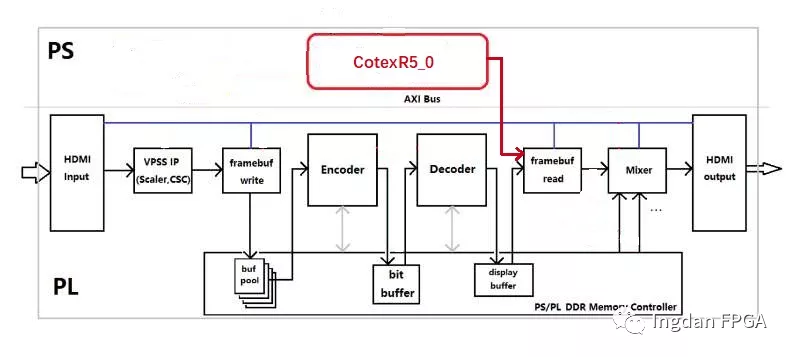

3626 PL側(cè)的寶貴資源。 這個(gè)設(shè)計(jì)是基于PS側(cè)的RPU(R5_0)來實(shí)現(xiàn)的上電送顯,首先系統(tǒng)上電在載完FPGA代碼后同時(shí)啟動(dòng)A53和RPU,然后我們通過RPU初始化HDMI接口并實(shí)現(xiàn)開機(jī)畫面的送,在顯示指定時(shí)間后自動(dòng)退出來將HDMI(Mixer,F(xiàn)ramebuffer等)控制權(quán)給ARM(A53)來使

2021-07-22 09:23:21 2388

2388

側(cè)和PL側(cè)。 PL和PS均支持64位的DDR4(不帶ECC功能),PL部分如果要支持64位的DDR4,則至少需要提供三個(gè)bank的HP接口,只能

2021-09-16 10:17:02 4789

4789

的協(xié)議,可用于寄存器式控制/狀態(tài)接口。例如,Zynq XADC 使用 AXI4-Lite 接口連接到 Zynq PS。

2022-05-10 09:52:12 1949

1949 目前基于MPSOC的一些參考設(shè)計(jì)中并沒有實(shí)現(xiàn)開機(jī)畫面的功能 ,那在一些帶顯示屏的產(chǎn)品在設(shè)計(jì)的時(shí)候就需要這一功能,基于原來傳統(tǒng)的方式也可以在FPGA中來實(shí)現(xiàn),今天分享一個(gè)在PS側(cè)來實(shí)現(xiàn)開機(jī)畫面,以節(jié)省PL側(cè)的寶貴資源。

2022-08-02 10:23:20 850

850

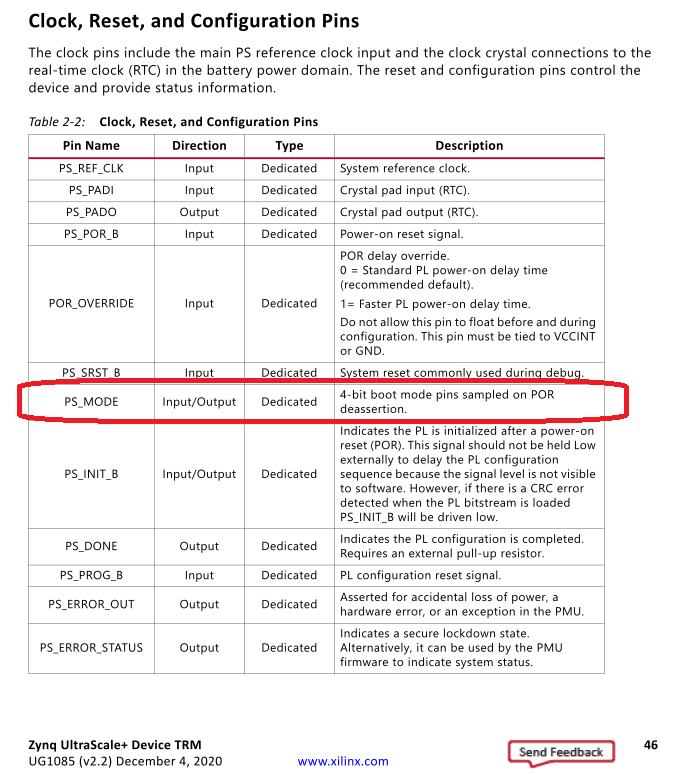

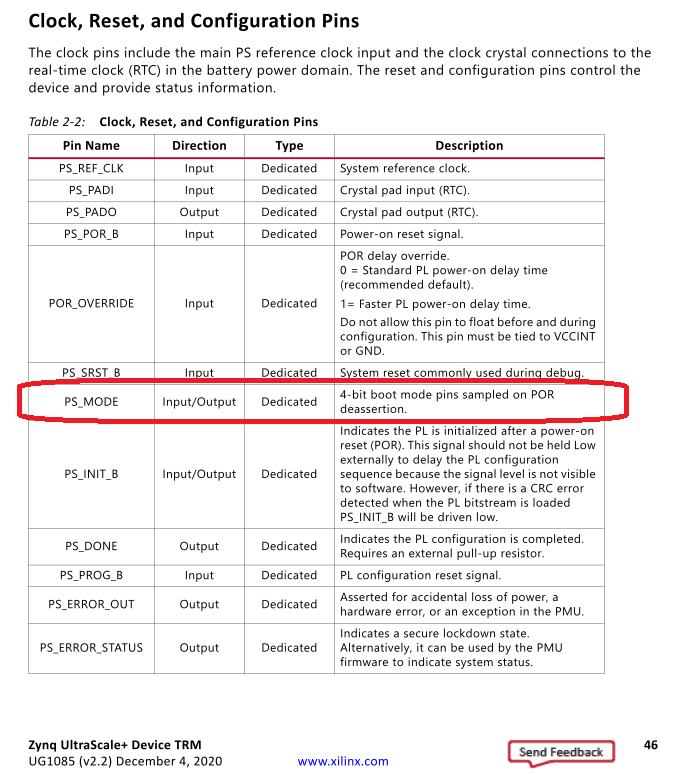

在Xilinx的ZCU102和ZCU106單板設(shè)計(jì)中,使用了管腳PS_MODE1作為外部USB Phy的復(fù)位信號(hào)。在MPSoC的文檔ug1085和ug1087中,關(guān)于PS_MODE1的信息比較少。下面是更詳細(xì)的描述。

2022-08-02 09:38:51 2142

2142

部分 ZynqUltraScale+MPSoC的可編程邏輯(PL)中包含最新的視頻編碼器/解碼器。這種新型硬化編解碼器能夠訪問來自PL 或PS的視頻和音頻流,以提供和/或存取達(dá)到軟件算法50倍的壓縮視頻信息,從而節(jié)省寶貴的系統(tǒng)存儲(chǔ)空間

2022-08-02 16:48:15 2465

2465

MPSoC是帶ARM處理器和FPGA(PL)的SoC,包含4核A53及其常用外部模塊(PS)。A53(PS)使用Arm GIC-400,屬于GICv2架構(gòu)。如果想了解GIC-400的具體細(xì)節(jié)

2022-08-02 09:14:52 1290

1290 Zynq MPSoC是Zynq-7000 SoC(之后簡(jiǎn)稱Zynq)的進(jìn)化版本。Zynq是賽靈思發(fā)布的集成PL(FPGA)和PS設(shè)計(jì)的最早的一代產(chǎn)品。如圖2.1所示,在相對(duì)較高層次對(duì)比了三種器件。Zynq MPSoC的PS部分比Zynq的PS部分面積更大,也更復(fù)雜。本章,將介紹這三種器件的特點(diǎn).

2022-08-15 09:16:38 1629

1629 電子發(fā)燒友網(wǎng)站提供《將Zynq PS和PL與內(nèi)存映射寄存器集成.zip》資料免費(fèi)下載

2022-12-06 15:14:29 2

2 S_AXI_ACP_FPD接口實(shí)現(xiàn)了PS 和PL 之間的低延遲連接,通過這個(gè)128位的接口,PL端可以直接訪問APU的L1和L2 cache,以及DDR內(nèi)存區(qū)域。故PL側(cè)可以直接從cache中拿到APU的計(jì)算結(jié)果,同時(shí)也可以第一時(shí)間將邏輯加速運(yùn)算的結(jié)果送至APU。

2023-02-01 15:36:53 1708

1708 有客戶需要通過PCie從Windows系統(tǒng)訪問MPSoC的DDR,從而使X86和A53通過共享DDR內(nèi)存的方式交互大量數(shù)據(jù)

2023-07-10 16:52:32 474

474

電子發(fā)燒友網(wǎng)站提供《基于PS和PL的1G/10G以太網(wǎng)解決方案應(yīng)用筆記.pdf》資料免費(fèi)下載

2023-09-15 10:29:25 1

1 電子發(fā)燒友網(wǎng)站提供《基于PS和PL的1G/10G以太網(wǎng)解決方案.pdf》資料免費(fèi)下載

2023-09-15 10:05:18 0

0 資料\Demo\All-Programmable-SoC-demos\”目錄下。案例包含PL端Vivado工程,主要使用Xilinx提供的標(biāo)準(zhǔn)IP核配置PL端資源實(shí)現(xiàn)接口擴(kuò)展,同時(shí)包含PS端裸機(jī)/Linu

2023-01-03 15:50:37 18

18

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論