第三個十年:FPGA成為SoC

2003 年,互聯網泡沫破滅的時候,Altera開始了他的第三個十年。這是大結局的一年:哥倫比亞號航天飛機悲劇謝幕,先驅者10號失去聯絡,最后一臺大眾甲殼 蟲駛出裝配線。但這也是開始的一年:伊拉克戰爭,美國股市大牛市的開始,私人開發的SpaceShipOne第一次超音速飛行,中國第一次載人航天。

在系統設計領域,FPGA悄然向下一階段發展。使用最先進的CMOS技術,FPGA的邏輯密度和速度足以在一個芯片中實現CPU內核及其外設。 Altera發布了Nios,這一RISC CPU內核針對FPGA進行了優化,合作伙伴也開發了在FPGA中實現的其他流行CPU內核。Avalon是一種多主機總線體系結構,適用于CPU和芯片 系統之間的可編程邏輯規范互聯。市場上還出現了SoPC Builder,這款工具可以自動的在基于FPGA的SoC中裝入知識產權(IP)。

這些底層工作導致人們對可編程邏輯進行全新的思考。設計人員會繼續在CPLD中開發膠合邏輯。對高性能有要求的設計人員會繼續在數據包交換、信號處理和相關應用中實現更快、功能更強大的加速器和子系統。而此外,在Altera的第三個十年,FPGA作為芯片系統冉冉升起。

以CPU為中心的時期

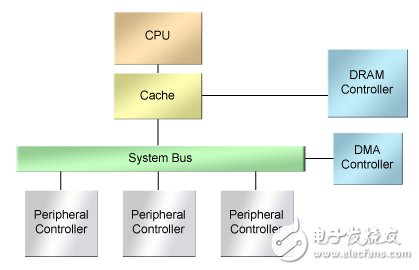

即使在這十年中,SoC也趨向于采用簡單模式,以它們所替代的電路板級計算機為基礎。一片SoC通常包括一個CPU內核,一個本地高速緩存或者緊耦合SRAM,一個DRAM控制器,一條片內微處理器總線,以及應用程序所需要的外設控制器等(圖1)。這類應用會包括DMA控制器或者應用加速器,適用于經常性的繁雜任務,例如,數據傳送、加密計算,或者快速傅里葉變換(FFT)等。

圖1.一個典型的以CPU為中心的Soc設計

在FPGA中實現SoC有很大的優點。設計人員可以只選擇CPU內核中需要的硬件模塊。數字加速器可以使用Altera FPGA中的高速數字信號處理(DSP)模塊,其算術性能要遠遠高于微處理器和DSP芯片組合所能達到的水平。設計人員還可以使用嵌入在FPGA架構中的 可編程邏輯、DSP模塊以及RAM模塊實現定制加速器。可以把這些加速器設計用作微處理器總線單元,或者獨立直通處理器,開發與微處理器控制平面相獨立的 數據平面。

據Altera產品規劃經理Bernhard Friebe,提高集成度的一個重要優點是能效。FPGA中的RAM和DSP模塊等硬件功能的能效不會低于等價的ASIC或者貨架功能產品的能效。在可編 程邏輯中實現的功能的功耗通常要比等價的標準產品高,但并不總是這樣。但是,在這一時期,很多系統的主要能耗來自I/O。數據通過FPGA架構傳送不但非 常快,而且效率要遠遠高于通過芯片邊界進行傳送。通過限制FPGA內部寬帶數據傳送,系統設計人員能夠有效的降低系統級能耗。

由于已經有了硬件和IP來支持以CPU為中心的SoC,因此,Altera的重點放在了工具流程上。很顯然,SoC開發人員的工具需求與傳統邏輯設 計人員的完全不同。傳統上,接口或者數據通路組件設計人員會以VHDL或者Verilog的形式詳細的表達他們的設計,然后,每一個單元要通過邏輯驗證、 映射至FPGA資源以及時序收斂等步驟。

而SoC設計人員更關注抽象級。硬件足夠快,片內RAM容量足夠大?總線和存儲器帶寬夠用嗎?總線接口能夠互聯嗎?由于能夠充分重新使用IP,因 此,設計投入的重點由全部SoC邏輯轉向編寫軟件,利用已有IP開發一個或者兩個新模塊,將其置入到設計中。換句話說,SoC開發人員就像系統設計人員那 樣進行思考,而不像芯片設計人員那樣。

這樣帶來的一個結果就是Altera于2005年首次推出的漸進式編譯功能。設計投入一般是集中在SoC的一個或者兩個模塊上,而硬件大部分工作保 持不變。Altera的漸進式編譯特性支持設計人員對設計中的一部分重新進行設計,一般是固定位置和引腳約束,不需要通過工具鏈重新運行整個設計。這不僅 節省了編譯時間,而且降低了已經設計好的硬件部分受到干擾的風險。

SoC設計還導致偏向使用FPGA I/O引腳。作為總線橋接或者加速器,FPGA會有突發或者流形式的數據流過芯片,一般是從一條標準總線到另一條總線。一般而言,只有較少的時鐘域,大部分是由總線定義的。

以CPU為中心的SoC帶來了新需求。通常會有標準外部總線,例如,PCI或者USB。而現在,FPGA會最先使用總線,而不僅僅是總線上的一個用 戶。當然還會有DRAM端口,使得FPGA面臨如何使用DDR SDRAM接口技術的難題。在片內外設控制器和外部器件之間還會有很多串行或者并行連接。這種多樣性意味著更多的引腳,I/O上更多的信號和更大的電壓變 化,以及更多的時鐘域。這些變化反映在越來越復雜的FPGA I/O單元和時鐘網絡上。

內核和多核

半導體工藝一直在不斷改進,晶體管密度也越來越高。但是在Altera的第三個十年中,越來越難以進一步提高電路速度了。相應的,CPU生產商關注 的重點從提高時鐘頻率轉向兩個、四個甚至管芯上更多的CPU內核——多核體系結構。SoC設計人員在ASIC設計和FPGA設計上都緊隨其后。

多核思路體現在FPGA使用上有兩個明顯的方向。一個思路就是簡單的復制CPU內核。這相對比較容易將多個處理器內核編譯到FPGA中。但是將其連 接起來就不那么容易了。這里,可編程邏輯提供了豐富的資源,設計人員幾乎可以實現從陣列到緊耦合內核,直至共享L2高速緩存體系結構的所有一切,設計實現 多主機Avalon?總線上的獨立CPU。

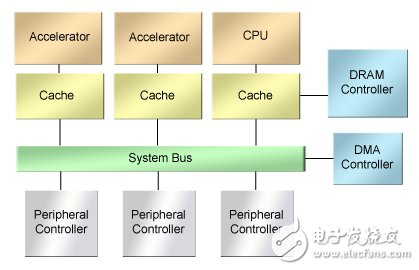

多核的另一個思路采用了不同的方法:異構系統。實現一個CPU內核例化的同一總線、IP和工具支持同時實現CPU內核和多個對等的加速器 (圖2)。這也導致完全不同的多核設計思路:以軟件為中心的方法。

圖2.一個異構多核SoC設計

設計同構多核系統非常直觀,極其簡單。您需要知道比單個CPU速度快多少倍。使用更多的CPU,多出一個或者兩個也有可能降低效率。根據您期望的線 程之間共享的存儲器等級,選擇互聯體系結構。在CPU之間劃分軟件線程,仿真系統,并重復直至符合規范要求。這一過程一直是以硬件為中心的,選擇一種體系 結構,實現它,然后,劃分代碼,適配到硬件中。

但是,能夠建立自己的加速器則創立了全新的方法。它是這樣工作的。分析您的代碼,找到熱點。對于最難處理的代碼部分,建立定制加速器,這節省了 CPU周期,降低了能耗。仿真系統,然后再分析步驟,并重復,直到性能滿足要求。這一方法從一個CPU內核上的工作軟件開始,產生定制滿足實際系統軟件要 求的多個硬件加速器。系統第一次反映了軟件需求,而不是強制軟件符合要求。

2006年,Altera推出了兩項創新,支持這種異構多核設計風格。一項是編譯器,將一組可執行ANSI C代碼轉換成加速器,針對Altera FPGA中的Nios? CPU內核進行了優化。這種C語言至硬件加速(C2H)編譯器工具自動完成以軟件為中心的設計中最耗時和最容易出錯的步驟:生成加速器。

第二項創新則不太明顯。如果您對比一個快速單核處理器與時鐘速度較慢的一組等價處理器的功耗,由于高效的加速器,動態功耗會大幅度下降。但是泄漏 ——多年來一直難以解決的問題,不論電路是否工作,都隨著晶體管數量的增加而增大。因此,對于多核設計,泄漏電流對能效的影響最大。

Altera以第二項創新——可編程功耗技術來解決這一問題。硬件和軟件工具相結合,對于時序不關鍵的通路,選擇慢速低泄漏電路,減小了FPGA中的泄漏電流,同時實現了時序收斂。結果是,不管深亞微米工藝的泄漏有多大,都滿足了異構多核設計的能耗要求。

一致性和增強

最后階段標志著Altera第三個十年的結束:IP選擇的一致性。逐漸的,系統設計領域更加關注最棘手問題的特殊解決方案。特別是,嵌入式系統開發 人員幾乎都采用了C語言,嵌入式計算普遍采用ARM?內核,一些接口標準開始成為某些應用的主要標準,例如,高速系統總線、背板鏈接和芯片間互聯等。由 此,Altera開發創新技術來支持這些解決方案。

一個例子是,編程人員表達并行代碼的方式。C語言雖然能夠很好的定義順序執行的程序,但是無法表達熟練的編程人員使用的并行處理方法。但是,名為 OpenCL?的C衍生語言可以。2011年,Altera推出了一組工具,支持編程人員采用越來越流行的OpenCL編寫并行算法,將其翻譯成FPGA 中的并行硬件以及傳統CPU中的控制代碼,這不需要專門的FPGA設計知識。

多核SoC越來越一致的使用ARM Cortex?-A類CPU內核帶來了第二項創新。只要每一個設計團隊希望有不同的CPU,FPGA供應商就要滿足這些需求,在可編程邏輯中實現軟核。但是這種靈活性有其成本:占用邏輯單元、高功耗和低速。

Altera則采用了別的方法:在越來越多的嵌入式和無線應用中使用Cortex-A9。2012年,公司開始推出具有管芯硬核處理器子系統的 FPGA樣片:雙核Cortex-A9群,有自己的高速緩存、本地RAM、經過優化的存儲器控制器,以及部分外設控制器,這些都在ASIC類型基于單元的 硬件中實現。芯片設計人員非常小心的優化子系統和可編程邏輯架構之間的互聯,以實現異構多核系統。

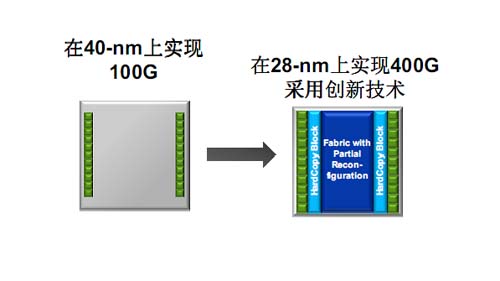

這種多核處理器系統和FPGA之間不斷的融合帶來了另一項更關鍵的創新。2013年,Altera發布其下一代高端FPGA不僅由傳統的代工線合作 伙伴制造,而且還由Intel公司制造,使用了14 nm三柵極工藝,這源自Intel自己的CPU和SoC。從ASIC定位的代工線市場轉向擅長CPU的代工線,Altera FPGA獨辟蹊徑來解決功耗和性能問題,優化半導體工藝特性,而不是優化滿足ASIC代工線要面對的各種市場需求,這對于工藝單元、本地RAM和高速互聯 都非常關鍵。

Altera相信,這種選擇的結果是打破FPGA業界多年以來所習慣的性能和能耗模式。這是新十年最好的開始。

電子發燒友App

電子發燒友App

評論