MZ7KH1T9HAJR1.92 TB2.5 英寸

MZ7KH240HAHQ240 GB2.5 英寸

MZ7KH3T8HALS3.84 TB2.5 英寸

MZ7KH480HAHQ480 GB2.5 英寸

MZ7KH960HAJR960 GB2.5 英寸

MZ7LH1T9HMLT1.92 TB2.5 英寸

MZ7LH240HAHQ240 GB2.5 英寸

MZ7LH3T8HMLT3.84 TB2.5 英寸

MZ7LH480HAHQ480 GB2.5 英寸

MZ7LH7T6HMLA7.68 TB2.5 英寸

MZ7LH960HAJR960 GB2.5 英寸

MZQL21T9HCJR-00A071.92 TBU.2

MZQL23T8HCJS-00A073.84 TBU.2

MZQL2960HCJR-00A07960GBU.2

MZVLB480HBJQ-00017480 GBM.2

MZVLB960HBLR-00017960 GBM.2

MZILT15THALA-0000715.36 TB2.5 英寸

MZILT15THMLA-0000715.36 TB2.5 英寸

MZILT1T9HAJQ-000071.92 TB2.5 英寸

MZILT1T9HBJR-000071.92 TB2.5 英寸

MZILT30THALA-0000730.72 TB2.5 英寸

MZILT30THMLA-0000730.72 TB2.5 英寸

MZILT3T8HALS-000073.84 TB2.5 英寸

MZILT3T8HBLS-000073.84 TB2.5 英寸

MZILT7T6HALA-000077.68 TB2.5 英寸

MZILT7T6HMLA-000077.68 TB2.5 英寸

MZILT960HAHQ-00007960 GB2.5 英寸

MZILT960HBHQ-00007960 GB2.5 英寸

MZPLJ12THALA-0000712.8 TBHHHL

MZPLJ1T6HBJR-000071.6 TBHHHL

MZPLJ3T2HBJR-000073.2 TBHHHL

MZPLJ6T4HALA-000076.4 TBHHHL

MZPLL12THMLA-0000512.8 TBHHHL

MZPLL1T6HAJQ-000051.6 TBHHHL

MZPLL3T2HAJQ-000053.2 TBHHHL

MZPLL6T4HMLA-000056.4 TBHHHL

MZWLJ15THALA-0000715.36 TB2.5 inch

MZWLJ1T9HBJR-000071.92 TB2.5 inch

MZWLJ3T8HBLS-000073.84 TB2.5 inch

MZWLJ7T6HALA-000077.68 TB2.5 inch

MZWLL12THMLA-0000512.8 TB2.5 英寸

MZWLL1T6HAJQ-000051.6 TB2.5 英寸

MZWLL3T2HAJQ-000053.2 TB2.5 英寸

MZWLL6T4HMLA-000056.4 TB2.5 英寸

MZPJB800HMGC800 GBPCI

2024-03-21 23:12:45

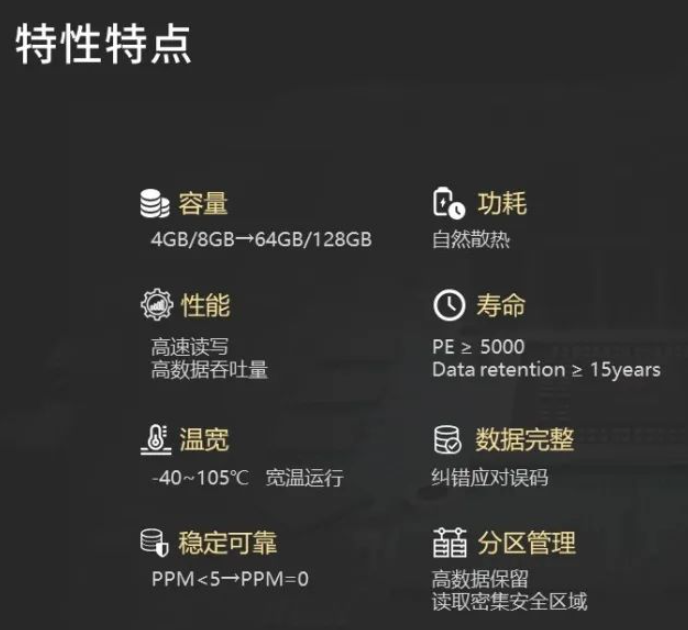

AI技術的飛速發展,存儲行業迎來了前所未有的挑戰與機遇。AI對算力的需求推動了存儲技術的進步,在這一背景下,作為一家成立于2011年的本土企業級SSD廠商,憶恒創源不斷探索如何提升存儲產品的能效和密度,以適應AI時代的需求。 ? 憶恒創源 C

2024-03-21 18:19:50 1362

1362

在硬件設施方面,三星選用的是具有1RU機架大小的PB SSD v2存儲服務器。據悉,每個PB SSD v2服務器均配備1顆AMD EPYC處理器及16個EDSFF E3.S規制的固態硬盤,每個硬盤容量高達15.36TB。

2024-03-21 14:21:56 93

93 2024年3月20日,上海?– 數字化時代的高速發展要求推動未來技術創新的數據存儲也持續迭代革新。為滿足用戶對于高性能、高可靠性、更大容量及更低成本的多樣化存儲需求,西部數據公司(NASDAQ

2024-03-20 18:19:54 852

852

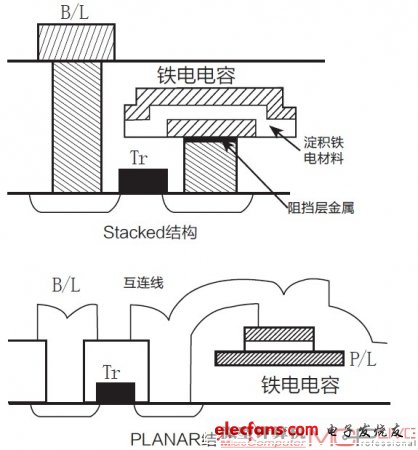

隨著數據存儲需求的持續增長,數據中心存儲技術和架構不斷發展以滿足企業和消費者的需求。在本節中,我們將分析數據中心存儲未來的一些關鍵趨勢。 一、全閃存存儲陣列 隨著閃存成本的下降以及相對于傳統硬盤

2024-03-18 17:39:22 141

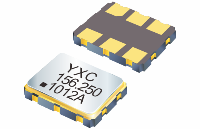

141 固態硬盤(SSD)已經成為現代計算機存儲的主流設備。相比于傳統的機械硬盤,SSD具有更高的讀寫速度、更低的功耗以及更高的耐用性,當然封裝尺寸也在往小型化的發展。隨著SSD容量的不斷增長和應用場景的性能要求不斷提升,其晶振需求也變得越來越復雜。

2024-03-07 15:48:12 740

740

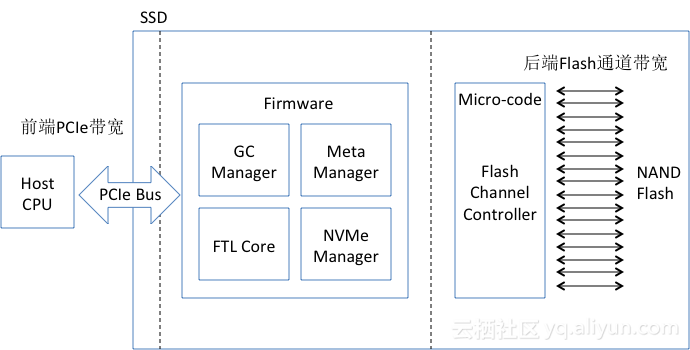

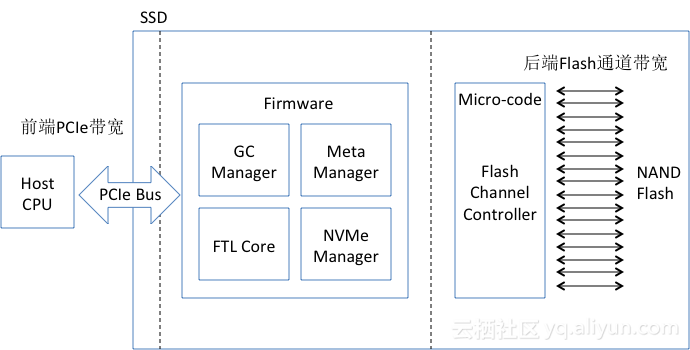

SSD(Solid State Disk)俗稱固態硬盤,是一種用于存儲數據的非易失性存儲設備,與傳統的機械硬盤(HDD)相比,具有更高的速度、更低的能耗和更好的可靠性。

2024-03-01 18:09:41 595

595

隨著NAND閃存需求預計在2024年復蘇,全球科技巨頭三星電子已迅速行動,在印度組建了一個專門的SSD(固態硬盤)研發團隊。此舉旨在擴大其業務版圖,并確保公司在存儲技術領域的領先地位。

2024-02-25 13:38:51 176

176 自2023年1月江波龍首次發布企業級存儲產品FORESEE ORCA 4836系列NVMe SSD與FORESEE UNCIA 3836系列SATA 3.2 SSD以來,企業級存儲產品于過去的一年

2024-02-06 10:35:03 96

96

NAND閃存作為如今各種電子設備中常見的非易失性存儲器,存在于固態硬盤(SSD)、USB閃存驅動器和智能手機存儲等器件。而隨著電腦終端、企業存儲、數據中心、甚至汽車配件等應用場景要求的多樣化

2024-02-05 18:01:17 418

418

近日,FORESEE XP2200系列PCIe SSD推出M.2 2280規格,進一步豐富了其產品線。這款產品搭載了主流的232層3D TLC閃存顆粒,展現了卓越的性能和穩定性。

2024-01-24 16:59:00 229

229 經歷兩年多的“低迷”,存儲產品的價格又要上揚了。最新行業消息稱,由于關鍵閃存芯片緊缺,SSD的價格將在本季度大幅上漲,尤其是大容量產品。

2024-01-19 11:12:39 438

438

產品簡介:OPC-2300液體顆粒計數器是普洛帝采用顆粒計數器提供者英國普洛帝分析測試集團公司的核心技術,嚴格按照英國普洛帝第八代雙激光窄光顆粒檢測技術,研制的一款在線液體顆粒計數器檢測設備,集結

2024-01-08 11:53:40

產品簡介:OPC-2300液體顆粒計數器是普洛帝采用顆粒計數器提供者英國普洛帝分析測試集團公司的核心技術,嚴格按照英國普洛帝第八代雙激光窄光顆粒檢測技術,研制的一款在線液體顆粒計數器檢測設備,集結

2024-01-08 11:19:28

產品簡介:OPC-2300液體顆粒計數器是普洛帝采用顆粒計數器提供者英國普洛帝分析測試集團公司的核心技術,嚴格按照英國普洛帝第八代雙激光窄光顆粒檢測技術,研制的一款在線液體顆粒計數器檢測設備,集結

2024-01-08 11:16:06

產品簡介:OPC-2300液體顆粒計數器是普洛帝采用顆粒計數器提供者英國普洛帝分析測試集團公司的核心技術,嚴格按照英國普洛帝第八代雙激光窄光顆粒檢測技術,研制的一款在線液體顆粒計數器檢測設備,集結

2024-01-08 11:13:11

產品簡介:OPC-2300液體顆粒計數器是普洛帝采用顆粒計數器提供者英國普洛帝分析測試集團公司的核心技術,嚴格按照英國普洛帝第八代雙激光窄光顆粒檢測技術,研制的一款在線液體顆粒計數器檢測

2024-01-08 11:02:19

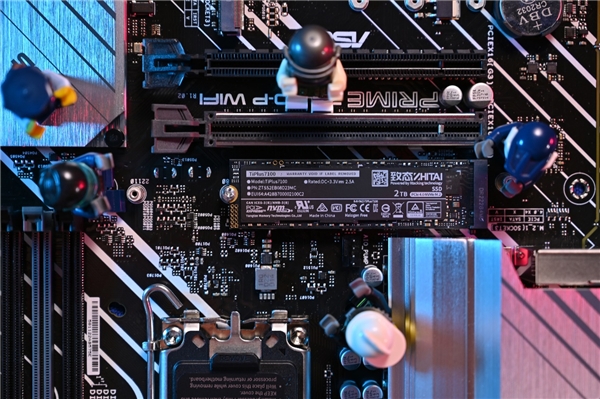

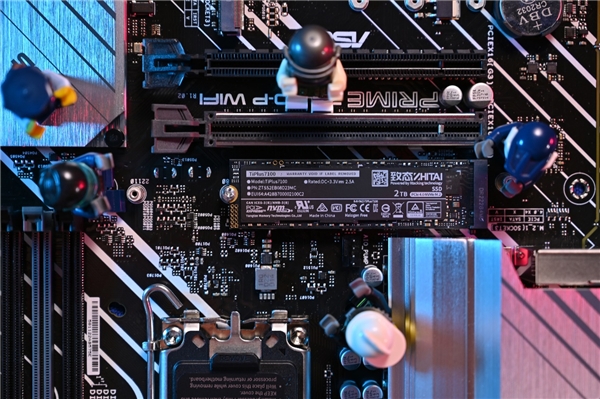

雖然現在PCI-E 5.0協議的主板已經算是比較普及,但真的要大家全套搞上5.0的顯卡+SSD,恐怕攢機的預算也會漲上去不少。為了提升我們攢機的性價比,我們只需要一個旗艦級別的系統盤就夠了,至于需要

2024-01-04 10:19:31 247

247

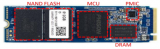

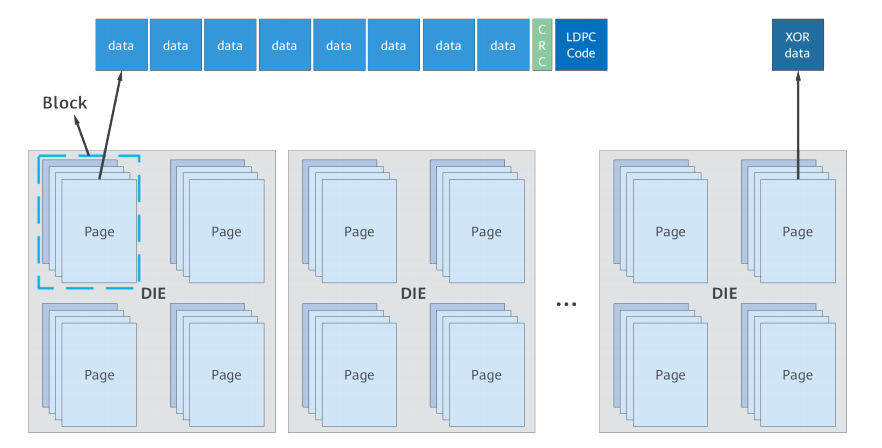

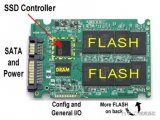

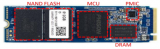

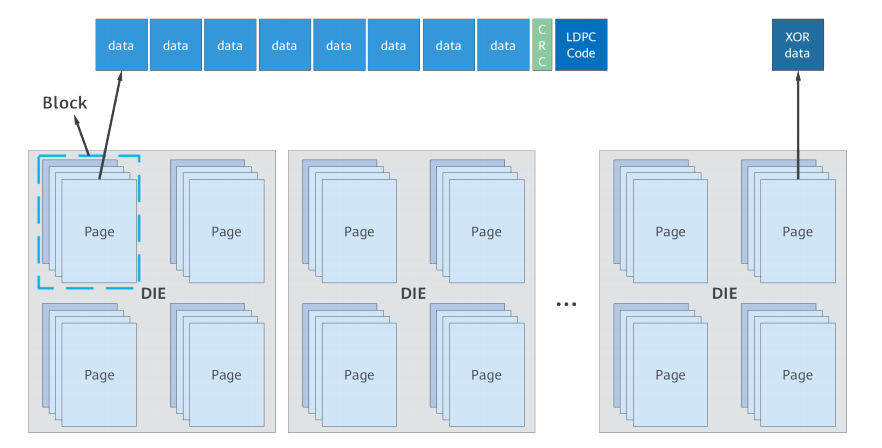

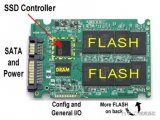

SSD主要由控制單元和存儲單元組成,控制單元包括SSD控制器、主機接口、DRAM等,存儲單元主要是NAND FLASH顆粒。NAND FLASH內部存儲讀寫的基本單元為Block和Page。

2024-01-02 10:16:58 277

277

前段時間長江存儲旗下的致態推出了首款QLC SSD,Ti600。Ti600之前已推出了500GB、1TB、2TB 3個容量配置,現在Ti600 又加推了4TB版本,讓消費者又多了一個大容量配置的選擇

2023-12-25 10:36:51 361

361

倪光南表示,隨著我國國產存儲整機和閃存生產能力逐步提升,SSD取代HDD時機已經到來。

2023-12-21 15:19:45 168

168 提及英睿達,相信很多人都知道這個品牌,因為當年組裝電腦沒少使用英睿達的內存,實際上英睿達是美光旗下的SSD和內存高端品牌。英睿達所使用的的存儲顆粒也都是美光。

2023-12-16 11:34:19 451

451

SSD領域涉及到較多的專業術語,為了更深入地了解SSD技術,本文對常用SSD術語進行簡要的說明和介紹。Namespace命名空間,是NVMe協議中一個基本的邏輯空間的概念。簡單地說,命名空間

2023-12-16 08:34:56 319

319

其實早在年初,就有不少搭載長江存儲閃存顆粒的國產4TB SSD,不過長江存儲的自有品牌致態,直到現在才推出這款致態TiPlus7100 4TB。

2023-12-12 11:07:48 594

594

在數字化時代,數據是我們生活的核心。從個人用戶到企業級應用,大數據存儲的需求越來越大,需要存儲速度更快、更可靠的解決方案。正是在這個背景下,U.2/U.3 SSD嶄露頭角,以其出色的性能和高速傳輸

2023-12-11 18:02:20 187

187

這主要得益于該月SSD控制芯片總出貨量的持續上升,其中受PCIe SSD控制芯片需求強勁影響,總出貨量年增長率接近40%,刷新歷史同期記錄,從而證實存儲行業總體漲價確實存在并可能持續。

2023-12-11 15:28:34 222

222 SSD硬盤的優點和缺點? SSD(固態硬盤)是一種基于閃存存儲器來存儲數據的存儲設備,與傳統的機械硬盤(HDD)相比,SSD具有明顯的優勢和一些缺點。下面將詳細介紹SSD硬盤的優點和缺點。 優點

2023-12-11 11:32:57 439

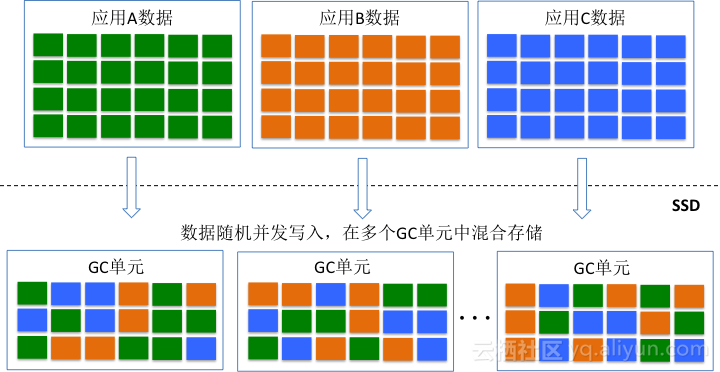

439 IO Pattern會對SSD的性能產生嚴重影響,主要表現在如下幾個方面

2023-12-09 11:38:19 830

830

,致態今日一次性上新兩款,讓你用個夠!搶先擁有致態TiPlus7100?4TB?SSD以及致態Ti600?4TB SSD兩款大容量顯眼包“卷王”,即刻實現容量自由! 大容量? 放肆用 致態兩款4TB大容量SSD,均采用基于長江存儲晶棧?Xtacking?3.0架構的高品質原廠顆粒,擁有強勁性

2023-12-08 10:36:00 408

408 SSD廠商早就預測NAND閃存的價格會隨著時間的推移而下降,讓SSD能夠在單價上與HDD競爭。事實上,NAND閃存的價格一直在下降。

2023-12-01 15:06:01 490

490

產品介紹 PXIe7501 是一款PCIe Gen3.0 X4 接口的標準PXIe 擴展 SSD 存儲卡,支持

2023-12-01 10:37:23

聚焦“數智創新 AI 未來”,邀請了眾多數據存儲龍頭企業以及專家學者參會,共同探討數據存儲領域的技術革新和商業趨勢。 “在智能化時代,算力、網力、存力是三大基礎。隨著算力、網力的飛速發展,以SSD為代表的存力,也必須提供更強的存儲性能、更優秀的時延、更高的可靠性,以滿足智能

2023-11-30 14:15:02 160

160

SSD主控芯片(SSD controller)好比固態硬盤的大腦。

2023-11-29 12:16:55 815

815

長鑫12GB LPDDR5芯片由8個12Gb顆粒封裝,這是長鑫存儲首款采用層疊封裝(Package on Package)的芯片產品。

2023-11-29 11:11:33 339

339 什么是聚集度指數PDI粒徑分布一、PDI的概念及作用PDI全稱為Polydispersity Index,中文翻譯為聚集度指數,是一種描述顆粒尺寸分布均勻程度的參數。PDI的值越小,顆粒尺寸分布越

2023-11-28 13:38:39

電子發燒友網站提供《毫米波人體掃描儀市場:過去、現在和未來.pdf》資料免費下載

2023-11-22 10:25:00 0

0 將 NVMe SSD 的用戶空間進行邏輯劃分,每個命名空間擁有自身的 NAND 顆粒,可以獨立地進行格式化和加密等操作。 OP Over-provisioning,一般稱為預留空間,它是指 SSD 保留一部分閃存空間留作他用,這部分空間用戶不可操作,容量大小一般是由主控決定的,一般不建議用戶自

2023-11-21 20:40:02 458

458

NVMe SSD 廠商Spec給出的性能非常完美,前面也給出了NVMe SSD和磁盤之間的性能對比,NVMe SSD的性能的確比磁盤高很多。

2023-11-13 11:39:15 545

545

8gu盤閃存顆粒壞了 可以自己換16g或者更大的閃存顆粒嗎

2023-11-01 06:47:37

SSD主要由控制單元和存儲單元(當前主要是FLASH閃存顆粒)組成,控制單元包括SSD控制器、主機接口、DRAM等,存儲單元主要是NAND FLASH顆粒。

2023-10-27 10:27:03 198

198

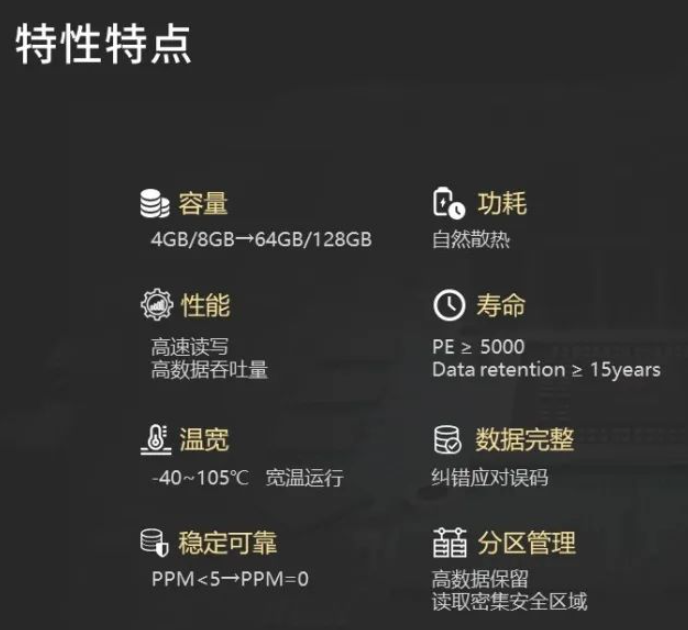

10月25日至28日,為期4天的第十九屆中國國際社會公共安全博覽會(簡稱:安博會)將在深圳會展中心(福田)盛大舉行,佰維將亮相安博會并重點展示 G系列工業級寬溫SSD、數據采集盤、軌道交通存儲

2023-10-24 14:57:02 102

102

本工作發表于FAST 2022。首次基于一家主要存儲供應商(NetApp)的近200萬個SSD的大量企業存儲系統,對生產使用中SSD的關鍵操作特性進行了大規模的現場研究。

2023-10-19 11:29:35 322

322

ssd1306用spi連接arduino,幾率花屏,但是在樹莓派上用就沒問題,請問各位大佬有什么好的建議嗎

2023-10-19 08:26:08

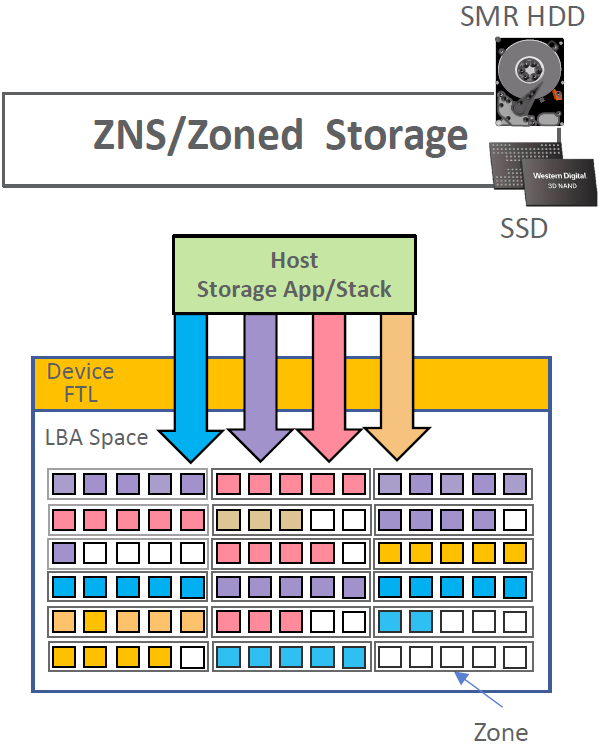

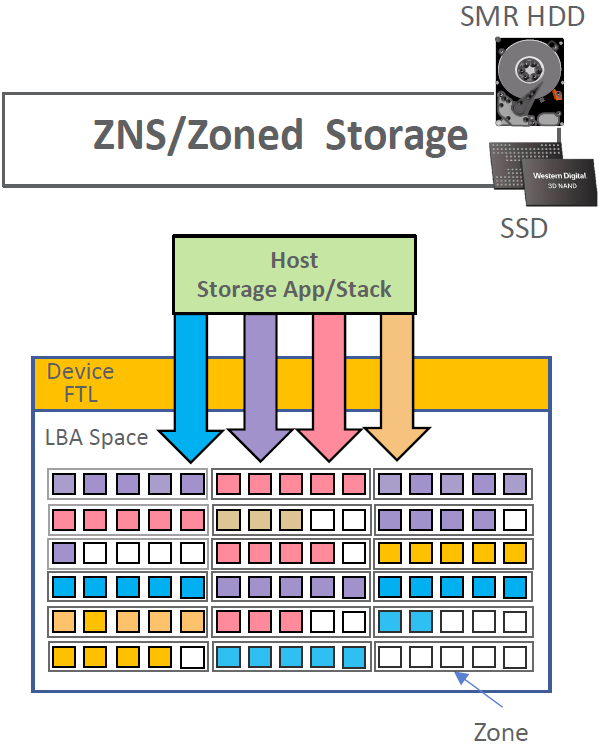

1、從ZNS說起 Zone Namespace(ZNS)在2020年開始廣泛討論,2021年在NVMe協議組織基本定稿發布。ZNS對于存儲系統或者云系統,在系統側可控制IO在SSD內的具體寫入位置

2023-10-12 15:55:01 907

907

固態驅動器(SSD)是一種由固態電子存儲芯片陣列構成的存儲設備,由控制單元和存儲單元組合而成。其接口規范、功能和使用方法與傳統硬盤完全一致,外形和尺寸也相同。與傳統硬盤相比,SSD提供了更快的讀寫速度和更高的可靠性。

2023-10-12 09:29:07 746

746

輸液瓶玻璃顆粒耐水性測試設備 在國家藥包材標準中,《YBB00252003-2015 玻璃顆粒在121℃耐水性測定法和分級》、《YBB00362004-2015 玻璃

2023-09-28 13:34:40

對于DIYer、硬件愛好者而言,最近一年顯然是愉快的一年,往日價格高高在上的大容量SSD,現在只需數百元就能買到。而為了讓用戶獲得更好的使用體驗,長江存儲在近期帶來了致態Ti600 SSD。其最低

2023-09-28 10:49:06 934

934

近日長江存儲旗下的致態家族再添新成員Ti600.Ti600是致態推出的首款QLC SSD。SSDFans第一時間體驗這款產品性能,并對Ti600(2T)做了相關測試。

2023-09-28 09:50:02 909

909

初始化函數

void SSD2828_Init(void)

{

SSD2828_QSPI_Init();

//Packet Write Configuration

SSD

2023-09-28 06:16:21

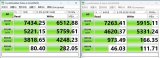

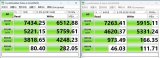

致態Ti600系列SSD采用了長江存儲最新一代NAND閃存顆粒,基于晶棧Xtacking 3.0架構,

再配合優秀主控解決方案,可以達到7000MB/s的讀取速度和6000MB/s的寫入速度,而實測數據比這還要更高一些。

2023-09-27 10:49:29 606

606

128*64 OLED的驅動芯片SSD1306的數據手冊0.96oled一般用ssd1306驅動,ssd1306的指令豐富,但是在平常顯示使用默認的初始化命令,之后就是讀寫顯示數據了,網上的例程很多,除了常用的命令,還描述工作模式。。。

2023-09-27 07:59:54

SSD主要由控制單元和存儲單元(當前主要是FLASH閃存顆粒)組成,控制單元包括SSD控制器、主機接口、DRAM等,存儲單元主要是NAND FLASH顆粒。

2023-09-25 09:45:51 161

161

隨著表面貼裝技術的不斷發展,越來越多的人開始接觸這個行業。當我們購買錫膏時,焊錫廠家一般都會問要幾號粉的錫膏。這是因為錫膏顆粒的大小對焊接有很大的影響,不同顆粒的大小有不同的焊接效果。今天

2023-09-20 16:46:04 773

773

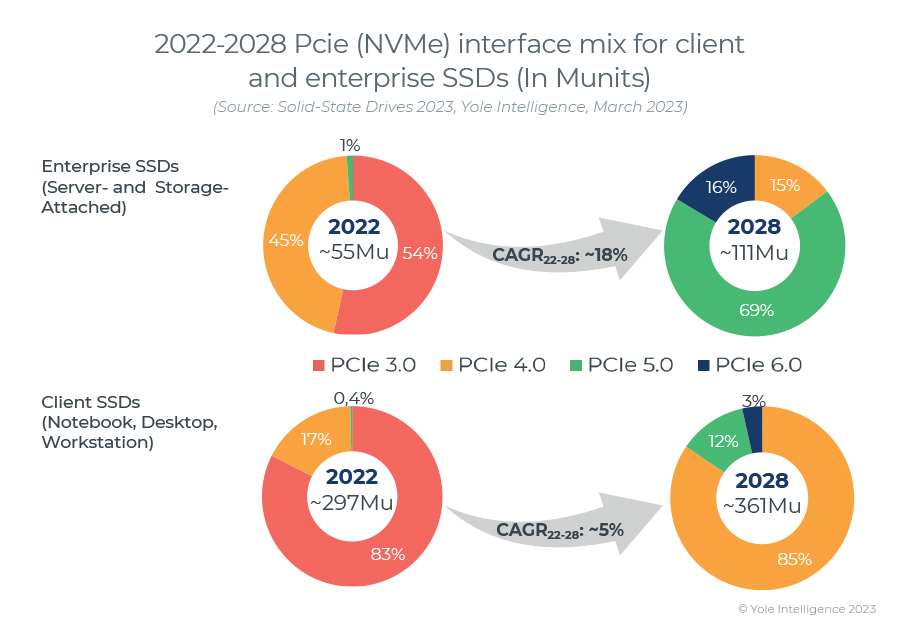

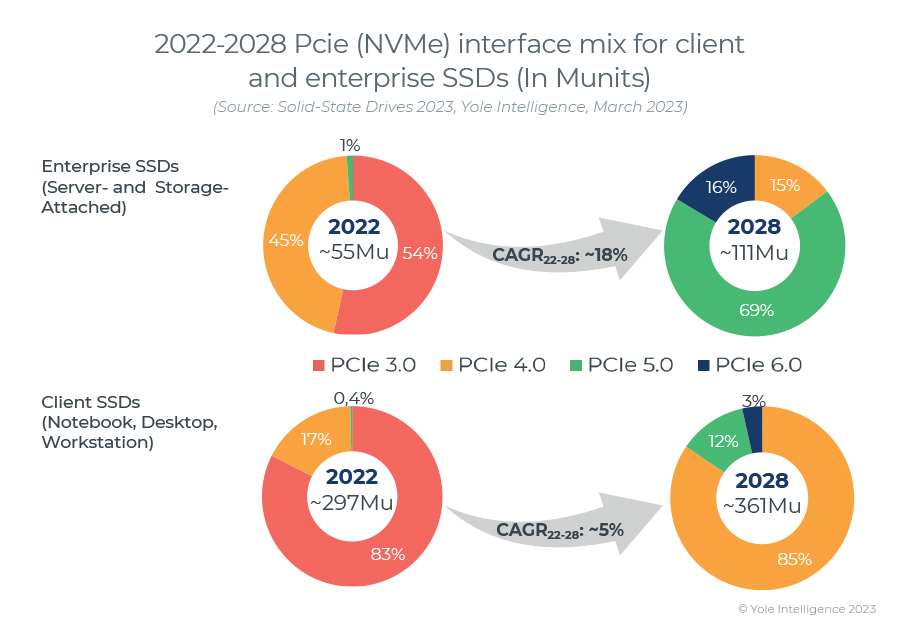

AI大模型、數據中心、云存儲等數字化領域的建設浪潮帶動了企業級SSD(eSSD)市場的新增需求。 根據Yole Group最新報告,2022年全球SSD出貨量約3.52億塊,其中企業級SSD出貨量

2023-09-14 12:15:02 369

369

LPDDR4內存顆粒 ),用于存放記錄數據位置的FTL映射表。SSD的讀寫操作都需要查詢這張記錄表,要想讀寫速度快,就需要把這張映射表存放在高性能的DRAM內存顆粒中,從而有效提升SSD的讀寫性能。

2023-09-12 11:01:54 481

481

近日,長江存儲旗下的致態即將發布新款SATA SSD產品SC001 XT,外觀尺寸為2.5寸,目前提供容量為500G/1TB,未來還會發布250GB/2TB的版本。

2023-09-12 10:52:53 1320

1320

如圖,2280規格SSD使用附帶螺絲完全無法鎖住。

2023-09-12 08:10:32

我想請問一下:

1、NVMe SSD的最大規格支持到 多大容量?500GB?1TB?2TB?以及PCIe版本和通道數,3.0[i]4或者4.04的版本可以嗎?還是?

2、所支持的TF存儲卡的最大規格,是多大容量?

3、板子背面eMMC的空位如果要用起來的話,有什么型號推薦嗎,怎么用?

非常感謝!

2023-09-12 07:44:25

。在這樣的背景下,建興儲存科技(鎧俠子公司)憑借對市場需求的精準洞察,正式推出首款搭載KIOXIA第六代BiCS FLASH? 3D閃存顆粒的CL6系列工業級SSD。 CL6系列SSD采用PCIe? 4.0 x4傳輸模式與NVMe? 1.4c標準,支持全面成熟的主機內存緩沖(HMB)

2023-09-06 16:40:34 772

772

近日,每年一度的國內閃存峰會Flash Memory World 2023于杭州蕭山完美落幕。峰會圍繞“芯存儲 AI未來”為主題,匯集了行業相關領導企業及權威教授學者,共同探討閃存和內存芯片為核心

2023-09-06 15:34:29 498

498 。SQErase旨在開創數據安全的未來,可通過 UEFI刪除關鍵數據 ,不受操作系統的限制,為堅固耐用型工業應用提供了全面的存儲安全解決方案。研華SSD SQFlash系列產品為 軍事 、 金融

2023-09-06 13:44:40 139

139

嵌入式終端正在打破過去的架構限制,朝著智能化、數字化、集成化的方向轉變,為存儲領域帶來全新的機遇。在日前舉辦的2023年elexcon深圳國際電子展上,江波龍旗下行業類存儲品牌FORESEE帶來了一站式存儲類產品,深化行業廣度,為未來存儲發展賦能。

2023-09-05 15:29:03 3659

3659 所以搭配有PCIe總線、BGA封裝類別的大容量SSD,即車用BGA PCIe SSD會是未來車用存儲的主要形態,它可以完美繼承PCIe總線接口帶來的所有先天優勢,同時具有更高容量密度,更快啟動速度,更好數據隔離性等特點。

2023-08-30 12:01:46 406

406

,其采用FLASH芯片作為存儲介質。SSD的基本組成結構包括Flash顆粒和Flash控制器,Flash控制器中有芯片,負責Flash的讀寫、磨損均衡、壽命監控等等。

2023-08-29 16:10:09 495

495 Disk,簡稱SSD)是以NAND閃存介質為主的一種存儲產品。近年來,由于SSD的低功耗、高性能、穩定安全等優點,使其越來越受到客戶的青睞,SSD也逐漸大量應用于IT運維、金融等行業。 性能vs成本,SSD如何兼得? 一個NAND閃存芯片封裝了若干個DIE(或者叫LUN)

2023-08-22 18:25:03 253

253

有人說“錫膏顆粒度越小其活性也就越強”,這是真的嗎?對于剛接觸錫膏行業不久的人可能會認同這一說法,小編本人就是其中之一。后來經過學習后才知道這是一種錯誤的說法。接下來由錫膏廠家講一下為什么說錫膏顆粒

2023-08-22 16:05:49 549

549

正式發布。與主流PCIe 4.0產品相比,PBlaze7 7940有著2.5倍的性能表現,支持更加豐富的企業級功能和更高產品能效比,可滿足未來數據中心不斷增長的存儲性能要求,為企業數字業務應用帶來更好支撐

2023-08-09 11:06:59 682

682

未來,軟件定義存儲(SDS)、分布式存儲和超融合(HCI)將延續高增長勢頭,成為未來云存儲的重要發展方向。

2023-08-07 14:33:02 1085

1085

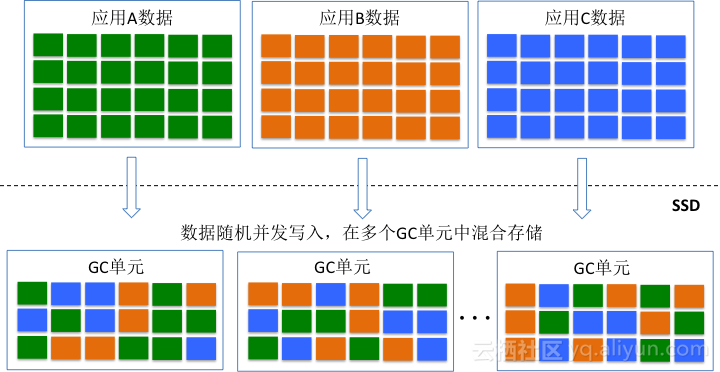

對更快速、更安全、更綠色的存儲需求,且隨著Flash顆粒單位容量成本不斷降低,SSD固態硬盤正在加速替代磁介質的HDD機械硬盤成為市場主流存儲介質。 如何應用好更強性能的SSD硬盤 卻并非易事 首先,在SSD硬盤高性能下,以往面向磁盤設計的傳

2023-08-01 16:35:03 276

276 在 PCI Express 誕生 20 周年之際,我們回顧一下這一盛行的擴展插槽的過去和未來。

2023-07-31 11:07:56 298

298

密碼是國家的重要手段,是國家重要的戰略資源,也是保障網絡和信息安全的核心技術和基礎基地。芯盛智能mp2000 pro安全ssd使用sm2/3/4國家密碼算法,在主芯片內安裝解密引擎,將安全基因注入內存芯片,保護ssd的信息存儲、讀取和傳輸。

2023-07-20 10:42:48 507

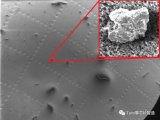

507 在芯片制造領域,顆粒的存在可能對生產過程產生巨大影響。

2023-07-08 09:28:09 567

567

公司對pcie ssd存儲器控制芯片及存儲器模塊的研究、開發及產業化項目的構建,根據不同市場層次的需要,開發出符合相關領域和場景的pcie存儲器控制芯片,提供集成產品服務。消費,商業級的需求,通過接近,市場拓展為基礎和潛力,技術升級情況相結合,逐步在公司產品結構高端產品所占的比率

2023-07-03 09:34:53 308

308 閃存存儲設備:NAND芯片作為主要的閃存存儲媒介,被廣泛用于固態硬盤(SSD)、USB閃存驅動器、內存卡(如SD卡、MicroSD卡)和閃存盤等。

2023-06-28 16:25:49 5198

5198 DMC4029SSD 產品簡介DIODES 的 DMC4029SSD 這款新一代 MOSFET 旨在最大限度地降低導通電阻 (R DS(ON) ),同時保持卓越的開關性能,使其成為高效電源

2023-06-26 22:18:58

在PCOEM前裝市場,PCIeSSD已成為主流存儲方案。近兩年,PCIeSSD價格逐漸下滑,PCOEM廠商采購成本也隨之降低,當前PC存儲應用正趨向于切換大容量、高性能的PCIe4.0SSD,其市場

2023-06-05 10:27:59 424

424

來自全球ICT產業的相關企業、專家、從業者,超過1000家企業將參加此次盛會。 ? ? 展會期間,得一微電子展示了包含SSD存儲(PCIe/SATA)、嵌入式存儲(UFS/eMMC/SPI-NAND

2023-06-02 15:03:10 577

577

又到了一年一度的京東618大促,長江存儲旗下唯一零售品牌致態也準備了給力優惠來回饋用戶。5月31日晚8點,京東正式開啟大促開門紅,致態SSD爆款產品直降,吐血推薦一定記得準時開搶! 全能戰士

2023-05-31 16:26:55 546

546

在PC OEM前裝市場,PCIe SSD已成為主流存儲方案。近兩年,PCIe SSD價格逐漸下滑,PC OEM廠商采購成本也隨之降低,當前PC存儲應用正趨向于切換大容量、高性能的PCIe 4.0

2023-05-27 14:35:01 290

290

SSD。這兩款產品通過降低運營成本并提高存儲效率,為數據中心帶來更多競爭優勢,以應對當今數據量急劇增長的趨勢。美光 6500 ION 是一款大容量的 SSD,能提供卓越的性能,并使數據中心更節能

2023-05-19 09:42:06 3904

3904 5月,芯盛智能發布基于RISC-V開源架構主控芯片的高性能PCIe SSD——EP2000Pro、MP2000Pro及EP3000,全面兼容3D TLC和QLC顆粒,并與國內主流CPU、OS、整機廠商適配兼容,以開源架構助力自研存儲創新升級,為用戶帶來安全高效的數據存儲體驗。

2023-05-16 11:54:25 400

400 如何使用 lua 腳本為 MQ7、MQ135 氣體傳感器和顆粒物傳感器編碼。

2023-04-27 07:23:12

監控客戶提供了更具市場競爭力的存儲選擇。 (FORESEE車載監控SSD) 貼合車載應用場景 解決多路監控痛點 對于PC用戶而言,一般情況下磁盤剩余空間較多,SSD常規 GC(

2023-04-21 19:30:02 366

366

存儲服務器的配置取決于您的需求和預算。一般來說,存儲服務器需要具備大容量、高可用性和可擴展性,因此需要考慮以下幾個方面: 1、存儲介質:存儲服務器可以使用硬盤或固態硬盤(SSD)作為存儲介質

2023-04-17 16:20:00 2567

2567 羅挺接受包括電子發燒友在內的媒體采訪,暢談得一微在新興應用的產品規劃與市場布局。 ? 得一微市場總監羅挺 ? 此前,得一微已推出多款PCIe、SATA SSD控制器。羅挺表示,PCIe3.0?SSD在未來一段時間仍是消費市場主流選擇。在企業級、數據中心市場,得

2023-04-13 00:50:00 1806

1806

隨著新興技術的發展,智慧家庭、工業物聯網、車聯網等行業的發展對存儲需求進行了新的定義,數據存儲形態呈現多樣化,人類已經進入大數據時代,多元化終端市場的增長拉動了嵌入式存儲需求。未來,數據存儲逐漸

2023-04-12 15:53:53 1830

1830 固態驅動器(SSD)是一個長得太大的USB記憶棒,存儲過程以電子方式進行。與磁盤驅動器相比,使用半導體芯片的優勢在于它們沒有高度敏感的設備,因此不易發生故障。這意味著SSD存儲設備對外部物理

2023-04-11 17:39:59 377

377 SSD2828QL9

2023-03-29 21:57:42

SSD2828QN4R

2023-03-29 21:53:56

SSD2543QN4

2023-03-29 21:46:17

SSD2829QL9

2023-03-29 21:46:17

SSD6250QN4R

2023-03-29 21:46:17

SSD1963QL9

2023-03-29 17:59:13

筆記本電腦SSD固態硬盤BGA芯片封裝加固用底部填充膠由漢思新材料提供客戶是一家研發、銷售、加工:電子產品、存儲卡,SSD(固態硬盤)的公司,其中筆記本電腦SSD(固態硬盤)用到漢思新材料的底部填充

2023-03-29 14:36:37 863

863

電子發燒友App

電子發燒友App

評論