彩燈作為一種景觀,安裝在建筑物的適當(dāng)?shù)胤揭皇亲鳛檠b飾增添節(jié)日氣氛,二是有一種廣告宣傳的作用,也可用在舞臺(tái)上增強(qiáng)晚會(huì)燈光效果。實(shí)現(xiàn)彩燈控制的方案很多,不同的控制方案,其設(shè)計(jì)方法和思路也不一樣。本文介紹一種彩燈控制器的設(shè)計(jì)方法。該系統(tǒng)基于可編程邏輯器件CPLD(Complex Programmable Logic Device)芯片,利用VHDL硬件描述語言設(shè)計(jì)系統(tǒng)核心部件,再配以適當(dāng)?shù)耐鈬娐窐?gòu)成。輸出為32路數(shù)字信號(hào),控制32路彩燈輸出,上電后,彩燈系統(tǒng)無需外加輸入信號(hào),能自動(dòng)循環(huán)演示十六種花型,彩燈明暗變換節(jié)拍為0.25秒和0.5秒,快慢兩種節(jié)拍自動(dòng)交替運(yùn)行。該系統(tǒng)較以前的傳統(tǒng)設(shè)計(jì),選用硬件電路簡(jiǎn)單、花型容量大,體積小,功耗低,可靠性高,特別是可以在使用一段時(shí)間后,不修改硬件電路的基礎(chǔ)上,僅通過更改軟件就可實(shí)現(xiàn)修改花型的編程控制方案。

1、 系統(tǒng)組成

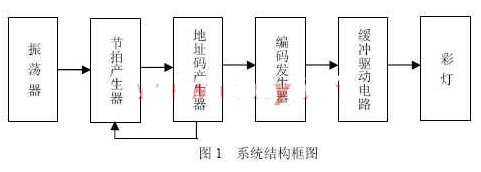

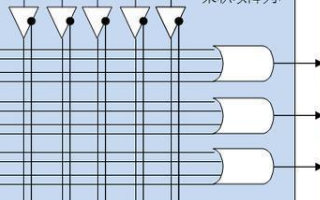

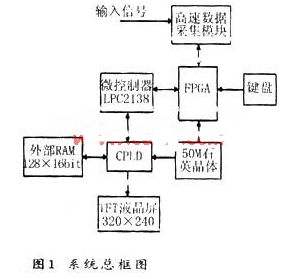

該彩燈控制器系統(tǒng)組成框圖如圖1所示。系統(tǒng)工作原理:彩燈控制器是以高、低電平控制燈的亮滅,按節(jié)拍改變送給各路的高、低電平,即l、0編碼,就可控制彩燈按預(yù)定的規(guī)律亮滅,從而顯示花型。彩燈控制器包括下列幾部分。振蕩器:提供系統(tǒng)工作的主時(shí)鐘。節(jié)拍產(chǎn)生器:產(chǎn)生系統(tǒng)要求的快、慢節(jié)拍脈沖PH、PL,并根據(jù)系統(tǒng)運(yùn)行情況,提供相應(yīng)節(jié)拍,使彩燈明暗變換以快、慢兩種節(jié)拍自動(dòng)交替運(yùn)行。地址碼產(chǎn)生器:為編碼發(fā)生器提供合適的地址碼,以保證按節(jié)拍讀出規(guī)定的編碼,復(fù)現(xiàn)預(yù)定的花型,并根據(jù)系統(tǒng)運(yùn)行情況,送節(jié)拍產(chǎn)生器反饋信號(hào),控制節(jié)拍按快慢兩種自動(dòng)交替運(yùn)行。編碼發(fā)生器:根據(jù)花型要求按節(jié)拍輸出32位狀態(tài)編碼信號(hào),以控制彩燈按規(guī)律亮滅。緩沖驅(qū)動(dòng)器:為彩燈提供需要的工作電壓和電流,隔離負(fù)載對(duì)系統(tǒng)工作的影響。

2、系統(tǒng)各單元設(shè)計(jì)

2.1 振蕩器

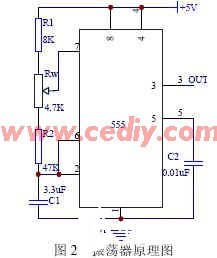

振蕩器提供系統(tǒng)工作的主時(shí)鐘。因彩燈控制器對(duì)定時(shí)要求不高,故選用簡(jiǎn)單易行的555定時(shí)振蕩器。系統(tǒng)彩燈明暗變換節(jié)拍為0.25秒和0.5秒,我們使振蕩器振蕩頻率為f = 4Hz,電路原理圖如圖2所示。圖中電阻R1=8K,Rw=4.7K, R2=47K,電容C1=3.3 uF,振蕩頻率輸出端OUT送“節(jié)拍產(chǎn)生器”的輸入端。

2.2節(jié)拍產(chǎn)生器

其作用產(chǎn)生系統(tǒng)要求的快、慢節(jié)拍脈沖,快節(jié)拍PH=0.25秒、慢節(jié)拍PL= 0.5秒。快節(jié)拍頻率直接由振蕩器的頻率傳入,慢節(jié)拍頻率將振蕩器輸出的頻率進(jìn)行二分頻得到。節(jié)拍選擇信號(hào)Pc由地址碼產(chǎn)生器產(chǎn)生,若第一輪花型循環(huán)輸出為慢節(jié)拍,Pc為低電平,則第二輪花型循環(huán),Pc為高電平,第三輪花型循環(huán),Pc又為低電平,如此反復(fù)。節(jié)拍產(chǎn)生器輸出節(jié)拍脈沖PP由PL和PH合成,![]() 。輸出節(jié)拍頻率PP送地址碼產(chǎn)生器。

。輸出節(jié)拍頻率PP送地址碼產(chǎn)生器。

該模塊VHDL程序如下(略去聲明部分):

ENTITY jpxz IS --節(jié)拍產(chǎn)生器

PORT ( clk: IN STD_LOGIC; --傳入振蕩器頻率

Pc : IN STD_LOGIC; --節(jié)拍選擇信號(hào)

PP : out STD_LOGIC);--輸出節(jié)拍頻率

end;

ARCHITECTURE jiep OF jpxz IS

signal PPL: STD_LOGIC;

signal PH: STD_LOGIC;--快節(jié)拍信號(hào)

signal PL: STD_LOGIC;--慢節(jié)拍信號(hào)

begin

fenp: process(clk) -- 將clk時(shí)鐘二分頻,得到節(jié)拍為0.5秒的慢節(jié)拍

BEGIN

IF clk‘EVENT AND clk = ’1‘

THEN PPL 《= NOT PPL;

END IF;

END PROCESS;

PH 《= clk;-- 快節(jié)拍的頻率等于振蕩器輸出的頻率

PL 《= PPL; -- 慢節(jié)拍

pp 《= (not Pc and PL) or (Pc and PH);

-- PP為輸出節(jié)拍信號(hào),Pc為高電平輸出快節(jié)拍,Pc為低電平輸出慢節(jié)拍

end;

2.3 地址碼產(chǎn)生器

其作用一是為編碼發(fā)生器提供合適的地址碼,二是為節(jié)拍產(chǎn)生器提供節(jié)拍控制信號(hào)。

該部分主要電路,一部分為地址計(jì)數(shù)器,利用進(jìn)程p01: process(ppclk)根據(jù)節(jié)拍產(chǎn)生器提供的節(jié)拍頻率PP產(chǎn)生地址碼,完成地址累加,實(shí)現(xiàn)預(yù)定花型的循環(huán)顯示,同時(shí)利用jiep信號(hào)記錄系統(tǒng)運(yùn)行情況,該32路彩燈控制器演示花型共16種,花型循環(huán)一周共243拍,地址計(jì)數(shù)器將地址碼累加到244,jiep值為‘1’,地址碼為其它值時(shí),jiep值為‘0’;另一部分內(nèi)容為利用進(jìn)程P02:process( jiep )將jiep信號(hào)進(jìn)行二分頻,使輸出花型在第一輪循環(huán)時(shí), 節(jié)拍選擇信號(hào)Pc為低電平,則第二輪花型循環(huán)時(shí),Pc為高電平,第三輪花型循環(huán),Pc又為低電平,如此反復(fù)。該模塊VHDL程序如下(略去聲明部分):

ENTITY cai_lizi IS --地址碼產(chǎn)生器;

PORT ( ppclk: IN STD_LOGIC; --節(jié)拍脈沖信號(hào),由節(jié)拍產(chǎn)生器傳入

dzout : out integer range 0 to 245;-- 地址碼輸出,16種花型運(yùn)行一次共243拍

Pc: out STD_LOGIC);--節(jié)拍選擇信號(hào),送節(jié)拍產(chǎn)生器

end;

ARCHITECTURE lizi OF cai_lizi IS

signal count: integer range 0 to 245;

signal jiep: STD_LOGIC;

begin

p01: process(ppclk) --產(chǎn)生地址碼

begin

if count=244 then count 《= 0; jiep 《= ’1‘; --16種花型運(yùn)行一次共243拍

elsif rising_edge(ppclk) then count 《= count + 1; jiep 《= ’0‘;

end if;

end process;

P02:process( jiep ) --將jiep信號(hào)進(jìn)行二分頻,產(chǎn)生節(jié)拍選擇信號(hào)Pc值

VARIABLE Count2 : STD_LOGIC;

BEGIN

IF jiep’EVENT AND jiep = ‘1’

THEN Count2 := NOT Count2;

END IF;

IF Count2 = ‘1’ THEN Pc 《= ‘1’;

ELSE PC 《= ‘0’;

END IF;

END PROCESS;

dzout 《= count;

end;

2.4 編碼發(fā)生器

地址碼產(chǎn)生器將輸出的地址碼送入編碼發(fā)生器,編碼發(fā)生器根據(jù)高、低電平控制燈的亮滅,即l、0編碼,依據(jù)花型要求按節(jié)拍輸出32位狀態(tài)編碼信號(hào),以控制彩燈按規(guī)律亮滅。

該模塊VHDL程序如下(略去聲明部分):

ENTITY cai_bmq IS

PORT ( dzout: IN integer range 0 to 245;-- 由地址碼產(chǎn)生器傳入地址碼

qout : OUT STD_LOGIC_VECTOR(31 DOWNTO 0));-- 輸出32位狀態(tài)編碼

END;

ARCHITECTURE bianma OF cai_bmq IS

begin

process(dzout)

begin

case dzout is

when 0 =》 qout 《= “10000000000000000000000000000000”;

when 1 =》 qout 《= “11000000000000000000000000000000”;

when 2 =》 qout 《= “11100000000000000000000000000000”;

……

when 241 =》 qout 《= “10010010010010010010010010010010”;

when 242 =》 qout 《= “01001001001001001001001001001001”;

when 243 =》 qout 《= “00100100100100100100100100100100”;

when others =》 qout 《= “10010010010010010010010010010010”;

end case;

end process;

end;

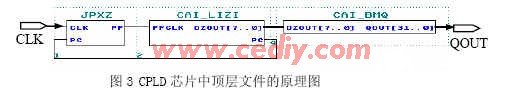

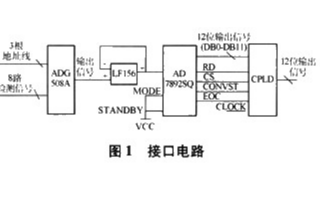

2.5 在CPLD芯片中頂層文件的原理圖,如圖3所示。

圖中JPXZ模塊為節(jié)拍產(chǎn)生器,輸入端CLK接振蕩器的輸出時(shí)鐘,頻率為4Hz,Pc為節(jié)拍選擇信號(hào),PP為輸出節(jié)拍。CAI_LIZI模塊為地址碼產(chǎn)生器,CAI_BMQ模塊為編碼發(fā)生器,輸出端QOUT[31..0] 輸出32位狀態(tài)編碼信號(hào), 接緩沖驅(qū)動(dòng)電路。

2.6 緩沖驅(qū)動(dòng)電路

該模塊為彩燈提供需要的工作電壓和電流,隔離負(fù)載對(duì)系統(tǒng)工作的影響。首先根據(jù)每路彩燈的功率選擇繼電器或雙向可控硅,再根據(jù)繼電器或雙向可控硅所需驅(qū)動(dòng)電壓和電流設(shè)計(jì)驅(qū)動(dòng)電路。詳細(xì)設(shè)計(jì)此處不再介紹。

3、系統(tǒng)仿真測(cè)試與實(shí)物測(cè)試

在基于MAX+PLUSⅡ軟件平臺(tái),對(duì)該系統(tǒng)程序各模塊進(jìn)行仿真測(cè)試,圖4所示為彩燈控制器頂層文件仿真波形圖。

圖中CLK為振蕩器產(chǎn)生系統(tǒng)的主時(shí)鐘,周期為0.25秒,qout[31..0]為彩燈控制器輸出的32路數(shù)字控制信號(hào)(32位狀態(tài)編碼),圖中所示當(dāng)系統(tǒng)以慢節(jié)拍(0.5秒,2個(gè)周期一拍)輸出最后一組編碼后,馬上以快節(jié)拍(0.25秒,1個(gè)周期一拍)開始下一輪花型循環(huán),達(dá)到設(shè)計(jì)要求。

將該系統(tǒng)程序下載到MAX7000S系列的EPM7128SLC84-15目標(biāo)芯片上,并配以外圍電路進(jìn)行實(shí)物測(cè)試( 以LED燈代替彩燈),滿足到設(shè)計(jì)要求。

4、結(jié)束語

本文作者創(chuàng)新點(diǎn):以VHDL 硬件描述語言進(jìn)行設(shè)計(jì),將彩燈控制器的核心部分集成在可編程邏輯器件CPLD芯片上,大大簡(jiǎn)化了外部電路,較以前的傳統(tǒng)設(shè)計(jì),既減少了所用芯片的種類和數(shù)量,縮小了體積,降低了功耗,提高了系統(tǒng)的整體性能,對(duì)系統(tǒng)在使用中的故障率大為減少。特別是,對(duì)花型設(shè)計(jì)方案的修改、增加花型數(shù)量都很方便,可以在不修改硬件電路的基礎(chǔ)上,僅通過更改軟件就可實(shí)現(xiàn),具有廣闊的應(yīng)用前景。

責(zé)任編輯:gt

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論