本文介紹的FPGA的特殊電源要求,說明了如何設(shè)計(jì)這些聰明的芯片的電源,然后回顧了一系列的針對(duì)FPGA應(yīng)用的電源模塊。

2015-11-24 18:01:01 1104

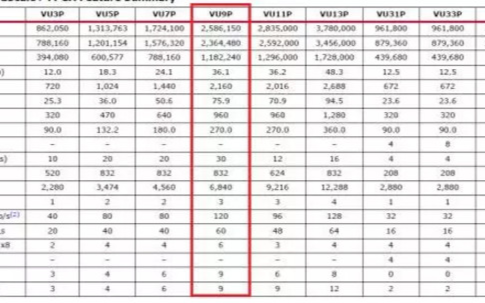

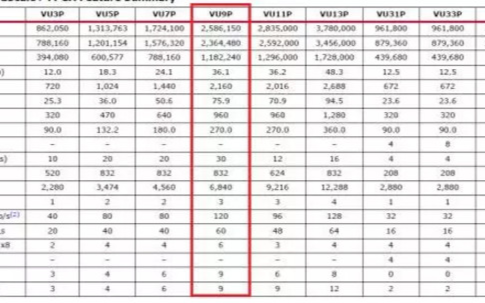

1104 以AMD-Xilinx FPGA為例,不同的制程工藝下針對(duì)用戶的各種需求,會(huì)規(guī)劃有多個(gè)產(chǎn)品系列,其中集成不同功能、不同性能的功能模塊,因此我們按照功能模塊劃分來描述AMD-Xilinx FPGA需要的各種供電電源,簡(jiǎn)單把電源種類分為PL供電電源、PS供電電源、集成功能塊供電電源。

2022-09-23 14:51:21 1932

1932 AGC電路在接收機(jī)中經(jīng)常用到,也很重要。那么AGC環(huán)路的實(shí)現(xiàn)方法是什么?

2021-04-14 06:56:01

幾個(gè)不錯(cuò)的資料哦,給大家共享下《FPGA系統(tǒng)設(shè)計(jì)的主要思路和方法初探》.pdf (766.25 KB )FPGA驗(yàn)證簡(jiǎn)介.pdf (255.69 KB )FPGA經(jīng)驗(yàn)總結(jié)(精華).doc (1.03

2019-05-27 02:11:57

芯片、FPGA1中的數(shù)據(jù)接口模塊、配置模塊、測(cè)試模塊和被測(cè)FPGA。軟件部分包含對(duì)實(shí)現(xiàn)FPGA配置部分的代碼和實(shí)現(xiàn)FPGA測(cè)試部分的代碼。FPGA1中的各硬件模塊通過EDA軟件以JTAG接口固化

2020-05-14 07:00:00

芯片中完成各類常用DSP模塊(包括基礎(chǔ)設(shè)計(jì)和高級(jí)設(shè)計(jì)兩大類)的高效開發(fā)技巧。? 課程內(nèi)容第二天以Xilinx器件的DSP系統(tǒng)開發(fā)技能為講課主線,分為下面4部分內(nèi)容:1. 基于FPGA

2009-07-21 09:22:42

調(diào)節(jié)LMT的增益,而數(shù)字部分的增益不變,這樣會(huì)使接收信號(hào)的信噪比變小,影響性能。 我的問題是: 在使用AGC的數(shù)字增益時(shí),怎樣能使AGC調(diào)節(jié)增益在能保證LMT、LPF的增益最大時(shí),首先調(diào)節(jié)數(shù)字部分的增益?

2018-09-18 11:16:02

BootLoarder是什么?BootLoader的操作模式有哪幾種呢?BootLoader啟動(dòng)過程分為哪幾個(gè)階段呢?

2021-11-30 07:02:07

IC的設(shè)計(jì)過程可分為哪幾個(gè)部分?前端設(shè)計(jì)的主要流程有哪些?Backend design flow后端設(shè)計(jì)流程有哪些?

2021-10-20 06:23:43

一、引言ASIC即(Application Specific Integrated Circuit)專用集成電路。IC設(shè)計(jì)可以分為兩個(gè)部分:前端設(shè)計(jì)(邏輯設(shè)計(jì))和后端設(shè)計(jì)(物理設(shè)計(jì)),這兩個(gè)部分

2021-07-29 08:18:53

Modbus-RTU下位機(jī)的實(shí)現(xiàn)主要包括以下幾個(gè)部分:串口數(shù)據(jù)收發(fā)接收幀超時(shí)處理請(qǐng)求命令解析響應(yīng)幀數(shù)據(jù)組裝用戶協(xié)議數(shù)據(jù)點(diǎn)表

2022-02-14 07:27:16

STM32的閃存模塊是由哪幾個(gè)部分組成的?SD卡可分為哪幾類?UCOSII是什么?有何優(yōu)點(diǎn)?

2021-10-15 07:03:02

STM32程序的編譯分為哪幾個(gè)步驟?

2021-11-26 06:15:24

高速模塊一般分為哪幾部分?USB芯片分為哪幾部分?

2021-10-25 06:50:35

WIFI無(wú)線接入的過程分為哪幾部分?WIFI無(wú)線接入的加密與認(rèn)證方式是如何去實(shí)現(xiàn)的?

2022-03-10 09:14:43

芯片中完成各類常用DSP模塊(包括基礎(chǔ)設(shè)計(jì)和高級(jí)設(shè)計(jì)兩大類)的高效開發(fā)技巧。? 課程內(nèi)容第二天以Xilinx器件的DSP系統(tǒng)開發(fā)技能為講課主線,分為下面4部分內(nèi)容:1. 基于FPGA

2009-07-21 09:20:11

芯片中完成各類常用DSP模塊(包括基礎(chǔ)設(shè)計(jì)和高級(jí)設(shè)計(jì)兩大類)的高效開發(fā)技巧。? 課程內(nèi)容第二天以Xilinx器件的DSP系統(tǒng)開發(fā)技能為講課主線,分為下面4部分內(nèi)容:1. 基于FPGA

2009-07-24 13:07:08

串口通訊是什么?stm32f103串口通訊可以分為哪幾個(gè)步驟呢?其代碼又該如何去實(shí)現(xiàn)呢?

2021-12-13 06:03:40

串口通信的硬件設(shè)計(jì)可以分為哪幾個(gè)部分呢?

2021-12-14 06:43:41

單片機(jī)引腳可分為哪幾部分?

2022-02-16 07:38:20

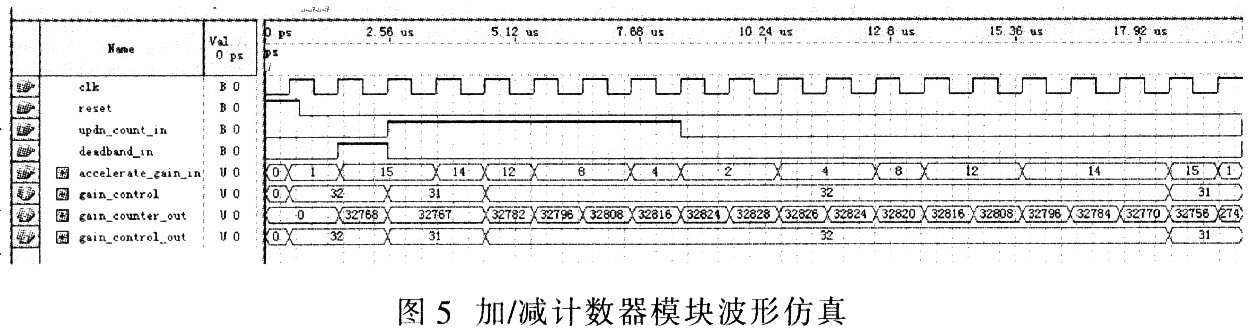

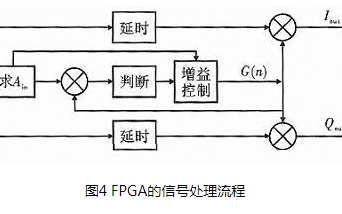

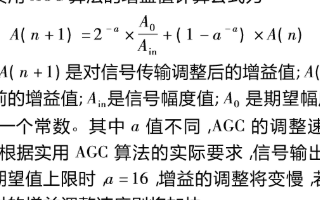

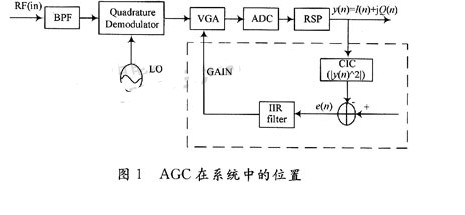

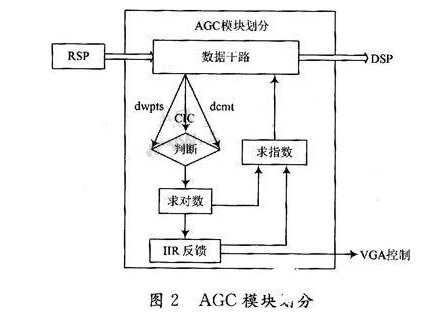

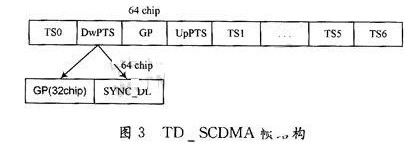

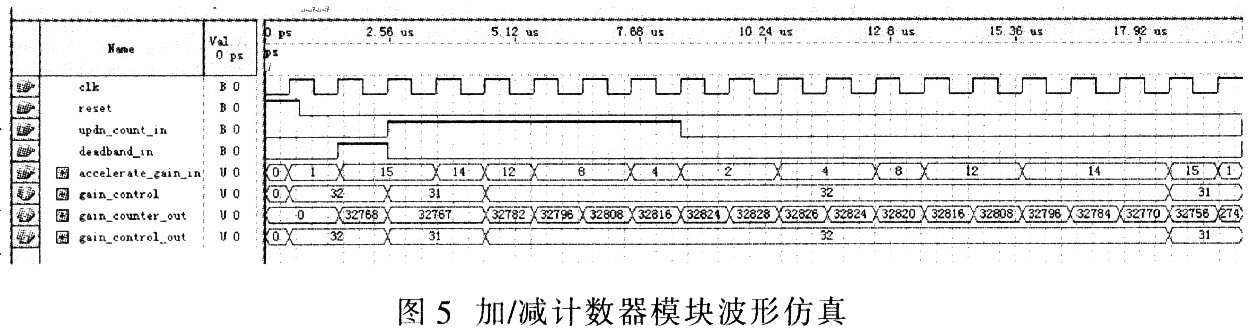

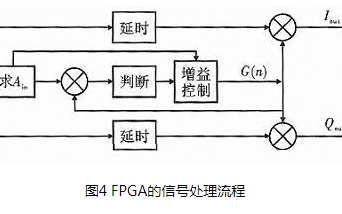

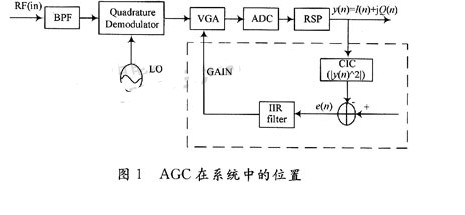

的 FPGA 實(shí)現(xiàn)根據(jù) AGC 所實(shí)現(xiàn)的功能,在 FPGA 中將 AGC 模塊分為如下幾個(gè)部分來實(shí)現(xiàn):3.1 數(shù)據(jù)千路模塊從 RSP 接口來 10 位二進(jìn)制補(bǔ)碼數(shù)據(jù) I1 和 Q1,與求指數(shù)模塊傳送來的預(yù)

2020-08-14 09:06:10

本文重點(diǎn)討論了如何根據(jù)射頻前端的輸出設(shè)計(jì)全數(shù)字AGC以擴(kuò)展接收機(jī)的動(dòng)態(tài)范圍,并給出了基于FPGA的外部AGC電路算法。

2021-04-30 06:57:26

內(nèi)容:1.掌握Verilog語(yǔ)法及使用方法,初步了解FPGA的基本工作原理及其他簡(jiǎn)單數(shù)字系統(tǒng)的系統(tǒng)級(jí)設(shè)計(jì)方法,學(xué)會(huì)如何利用FPGA實(shí)現(xiàn)實(shí)際的各種功能。 2.采用Labview實(shí)現(xiàn)上位機(jī)程序編寫,實(shí)現(xiàn)

2016-04-19 20:33:42

FPGA配置原理簡(jiǎn)介基于模塊化動(dòng)態(tài)部分重構(gòu)FPGA的設(shè)計(jì)方法如何去實(shí)現(xiàn)FPGA動(dòng)態(tài)部分的重構(gòu)?

2021-04-29 06:33:12

PADS是什么?PADS包括哪些部分?如何去安裝Pads VX.2軟件?主要分為哪幾個(gè)部分?

2021-06-30 06:18:51

如何在FPGA應(yīng)用程序中將固定點(diǎn)稱為重要的?以上來自于谷歌翻譯以下為原文How fixed point can be called important in FPGA Applications?

2019-02-18 13:24:43

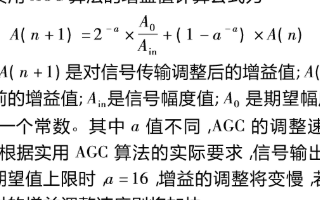

放大調(diào)整后,確保了通信系統(tǒng)信號(hào)輸出的幅度可基本維持在恒定的狀態(tài)。文中將AGC算法應(yīng)用于音頻信號(hào)處理中,可實(shí)現(xiàn)FPGA,并可有效降低音頻信號(hào)輸出時(shí)的干擾,保證信號(hào)的穩(wěn)定。2、 基于AGC算法的音頻信號(hào)處理

2020-10-21 16:42:15

嵌入式總共分為哪幾個(gè)主流方向?

2021-09-24 07:13:09

AGC中頻放大器模塊的主要特點(diǎn)AGC中頻放大器設(shè)計(jì)

2021-04-07 06:52:32

手指檢測(cè)心跳設(shè)計(jì)可分為幾個(gè)部分呢?

2021-12-20 07:58:17

數(shù)字示波器摘要:本次數(shù)字示波器設(shè)計(jì)分為輸入電路模塊,采樣保持模塊,AD采樣電路,FPGA與單片機(jī)結(jié)合的控制模塊等。本設(shè)計(jì)核心處理器采用單片機(jī)與FPGA相結(jié)合的方案,輸入信號(hào)首先進(jìn)入輸入電路模塊,通過

2021-08-09 06:25:55

說明:文章來源 EDN電子技術(shù)設(shè)計(jì):嵌入式程序開發(fā)需要知道的存儲(chǔ)器知識(shí)MCU 中常使用的存儲(chǔ)器類型有:FLASH、RAM、ROM(包括EEPROM) 在軟件角度來看,程序和數(shù)據(jù)的存儲(chǔ)分為以下幾個(gè)部分

2021-07-15 08:09:43

線控轉(zhuǎn)向轉(zhuǎn)向盤總成分為兩個(gè)部分,轉(zhuǎn)向盤至扭矩傳感器上部和扭矩傳感器下部至路感電機(jī),姑且稱之為轉(zhuǎn)向盤部分和路感電機(jī)部分。轉(zhuǎn)向盤部分對(duì)轉(zhuǎn)向盤與轉(zhuǎn)矩傳感器進(jìn)行動(dòng)力學(xué)分析,考慮轉(zhuǎn)向盤轉(zhuǎn)動(dòng)慣量與粘性阻尼,并將

2021-09-15 09:26:01

航模無(wú)刷電機(jī)大概分為哪幾個(gè)系列?分別是什么?有哪些特點(diǎn)?

2021-07-21 08:10:03

請(qǐng)問一下單片機(jī)的ram分為幾個(gè)部分呢?像stm32這種哈佛結(jié)構(gòu)的單片機(jī),除了堆,棧,和全局?jǐn)?shù)據(jù)部分之外,還有其他的部分嗎?還有就是如果我的程序里面定義的較大的局部數(shù)組,在MDK環(huán)境下就需要我手動(dòng)的修改棧的大小是嗎?請(qǐng)大家指導(dǎo)一下,謝謝。

2018-11-05 08:45:32

求解答這個(gè)電路分為幾個(gè)部分,每個(gè)部分的作用,以及整個(gè)電路原理

2020-06-28 19:27:04

主要介紹基于現(xiàn)場(chǎng)可編程門陣列(FPGA)的微波接力通信中FFT 模塊的設(shè)計(jì)與實(shí)現(xiàn)方案。提出一種全并行流水結(jié)構(gòu),采用新一代大容量的高速Stratix 系列FPGA 可以在N 個(gè)系統(tǒng)時(shí)鐘之內(nèi)

2009-11-24 12:13:19 19

19 摘 要:介紹了基于現(xiàn)場(chǎng)可編程門陣列(FPGA)的以太網(wǎng)MAC子層協(xié)議的硬件實(shí)現(xiàn)方法.硬件結(jié)構(gòu)上由控制模塊、發(fā)送模塊和接收模塊3個(gè)部分組成,發(fā)送模塊和接收模塊采用狀態(tài)機(jī)控制數(shù)據(jù)發(fā)

2010-07-15 11:27:29 24

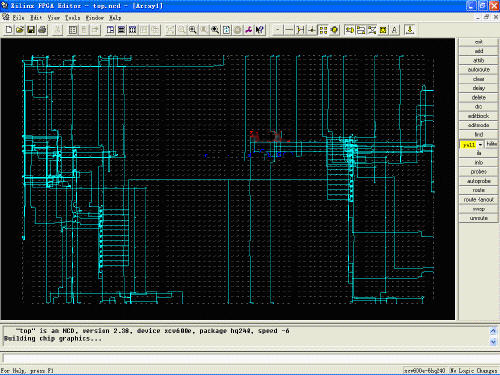

24 論述了某航天器DS-SS接收機(jī)外部AGC的設(shè)計(jì)原理和具體實(shí)現(xiàn),重點(diǎn)討論了如何根據(jù)射頻前端的輸出設(shè)計(jì)全數(shù)字AGC以擴(kuò)展接收機(jī)的動(dòng)態(tài)范圍,并給出了基于FPGA的外部AGC電路算法。計(jì)算機(jī)仿

2010-07-17 15:02:13 9

9 本文在研究了三層以太網(wǎng)交換技術(shù)后,設(shè)計(jì)了一種采用FPGA來實(shí)現(xiàn)以太口和ATM口之間的數(shù)據(jù)通道上HEC模塊的實(shí)現(xiàn)方法。文中給出了詳細(xì)的設(shè)計(jì)方案,并論述了采用FPGA設(shè)計(jì)的原因和思路

2010-08-09 15:20:33 16

16 采用Xlinx公司的Virtex5系列FPGA設(shè)計(jì)了一個(gè)用于多種高速串行協(xié)議的數(shù)據(jù)交換模塊,并解決了該模塊實(shí)現(xiàn)中的關(guān)鍵問題.該交換模塊實(shí)現(xiàn)4X模式RapidIO協(xié)議與4X模式PCI Express協(xié)議之間的數(shù)據(jù)交

2010-09-30 16:31:57 39

39 為了滿足某測(cè)控平臺(tái)的設(shè)計(jì)要求,設(shè)計(jì)并實(shí)現(xiàn)了基于FPGA的六通道HDLC并行通信系統(tǒng)。該系統(tǒng)以FPGA為核心,包括FPGA、DSP、485轉(zhuǎn)換接口等部分。給出了系統(tǒng)的電路設(shè)計(jì)、關(guān)鍵模塊及軟件

2010-09-30 16:49:30 43

43 :在模擬電路和數(shù)字信號(hào)處理兩方面簡(jiǎn)要地介紹音頻AGC的實(shí)現(xiàn)方法,并給出數(shù)字信號(hào)處理方式的理論分析和具體實(shí)現(xiàn)。關(guān)鍵詞:AGC(自動(dòng)增益控制);數(shù)字信號(hào)處理;希爾伯特變

2010-10-11 16:55:54 136

136 數(shù)字中頻接收機(jī)中,采用可變?cè)鲆娣糯笃鰽D603、數(shù)字可控增益放大器AD8320和FPGA實(shí)現(xiàn)大動(dòng)態(tài)范圍的數(shù)字自動(dòng)增益控制(AGC)。該設(shè)計(jì)充分利用AD9220的兩個(gè)指示輸入信號(hào)范圍的輸出端口

2010-12-28 10:31:07 34

34 為能充分利用數(shù)字技術(shù)可靠性高、靈活性強(qiáng)等優(yōu)點(diǎn),將自動(dòng)增益控制AGC引入數(shù)字域,并針對(duì)超聲波氣體流量計(jì)中接收信號(hào)的特點(diǎn),給出一種基于EP1K30TC144-3的全數(shù)字AGC設(shè)計(jì)方案。測(cè)試

2010-12-30 16:02:53 34

34 作者Email: shenggenhu@sohu.com huandy@126.com摘 要:本文主要分析自動(dòng)增益控制(AGC)的基本原理

2006-03-11 17:39:13 1257

1257

臺(tái)積電年中將為Altera試產(chǎn)28nm制程FPGA芯片

據(jù)業(yè)者透露,臺(tái)積電公司將于今年中期開始為Altera公司生產(chǎn)28nm制程FPGA芯片產(chǎn)品。這種FPGA芯片將集成有28Gbps收發(fā)器,產(chǎn)品面

2010-02-05 10:21:26 545

545 FPGA的超聲波氣體流量計(jì)中AGC的原理及設(shè)計(jì)實(shí)現(xiàn)

概述:為能充分利用數(shù)字技術(shù)可靠性高、靈活性強(qiáng)等優(yōu)點(diǎn),將自動(dòng)增益控制AGC引入數(shù)字域,并針對(duì)超

2010-03-17 11:33:30 1358

1358

FPGA實(shí)現(xiàn)與40G QSFP光學(xué)模塊的互操作性

Altera 公司 宣布其Stratix IV GT FPGA 實(shí)現(xiàn)了與Avago公司 的 40G 四通道小型可插

2010-04-02 10:49:21 2145

2145 定義

自動(dòng)增益控制(Automatic Gain Control)

使放大電路的增益自動(dòng)地隨信號(hào)強(qiáng)度而調(diào)整的自動(dòng)控制方法。

實(shí)現(xiàn)這種功能的電路簡(jiǎn)稱AGC環(huán)。AGC環(huán)

2010-08-19 15:42:45 2942

2942 動(dòng)態(tài)部分重構(gòu)可以通過兩種方法實(shí)現(xiàn):基于模塊化設(shè)計(jì)方法(Module-Based ParTIal Reconfiguration)和基于差別的設(shè)計(jì)方法(Difference-Based Partial Reconfiguration),本文以基于模塊化設(shè)計(jì)為例說

2010-08-23 10:35:47 554

554

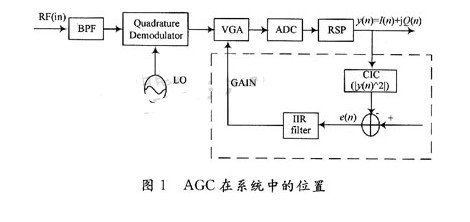

隨著軟件無(wú)線電技術(shù)和FPGA、DSP、AD 等技術(shù)的高速發(fā)展,數(shù)字接收機(jī)的應(yīng)用日益廣泛。為了擴(kuò)大數(shù)字接收機(jī)的ADC 動(dòng)態(tài)范圍,廣泛采用了自動(dòng)增益控制(AGC) ,使接收機(jī)的增益隨著信號(hào)的強(qiáng)弱

2011-10-11 18:30:03 3229

3229

針對(duì)調(diào)制樣式在不同環(huán)境下的變化,采用了FPGA部分動(dòng)態(tài)可重構(gòu)的新方法,通過對(duì)不同調(diào)制樣式信號(hào)的解調(diào)模塊的動(dòng)態(tài)加載,來實(shí)現(xiàn)了不同環(huán)境下針對(duì)不同調(diào)制樣式的解調(diào)。這種方式比傳

2012-06-18 13:42:13 33

33 為了實(shí)現(xiàn)電控噴油霧化檢測(cè)快速測(cè)量和處理大量的數(shù)據(jù)的要求,設(shè)計(jì)一種基于DSP和FPGA信號(hào)控制與實(shí)時(shí)數(shù)據(jù)處理系統(tǒng)的通信模塊。該通信模塊硬件部分主要用來實(shí)現(xiàn)開發(fā)板GN0204中DSP與FP

2013-08-07 19:26:49 35

35 空間太陽(yáng)望遠(yuǎn)鏡FPGA星載圖像壓縮模塊的設(shè)計(jì)與實(shí)現(xiàn)

2016-09-17 07:37:00 23

23 基于FPGA的高速DSP與液晶模塊接口的實(shí)現(xiàn)

2017-10-19 13:46:23 3

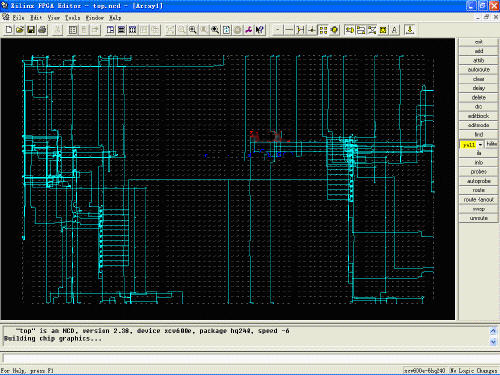

3 設(shè)計(jì),詳述了各子模塊的設(shè)計(jì)思路和方法,給出了它們的仿真時(shí)序圖。綜合實(shí)現(xiàn)后,將程序下載到FPGA芯片中,運(yùn)行正確無(wú)誤。又經(jīng)長(zhǎng)時(shí)間發(fā)送和接收測(cè)試,運(yùn)行穩(wěn)定可靠。

2017-11-18 11:33:01 5153

5153 與模擬AGC相比,數(shù)控AGC由于反饋部分的主要功能由數(shù)字部分實(shí)現(xiàn),故其AGC控制可以更加容易地得到實(shí)現(xiàn)。利用數(shù)字信號(hào)處理精度高的特點(diǎn),可以精確地實(shí)現(xiàn)數(shù)字增益補(bǔ)償,使系統(tǒng)具有快速收斂和精確地穩(wěn)態(tài)響應(yīng)等優(yōu)點(diǎn)。

2018-06-29 16:46:00 1651

1651

和指令通信下發(fā)阻塞嚴(yán)重等問題。為此,文中提出了在中間層增設(shè)方陣自動(dòng)發(fā)電控制(AGC)的分層分布式AGC系統(tǒng)結(jié)構(gòu)。文中研究了光伏方陣AGC -體化產(chǎn)品技術(shù)實(shí)現(xiàn)方案、方陣AGC的功率分配算法與策略,并分析給出了方陣AGC與廠站AGC系統(tǒng)的

2017-12-08 12:06:11 0

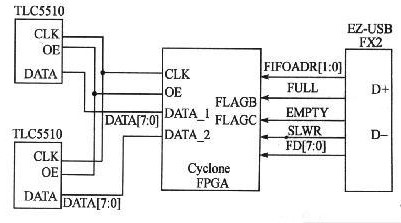

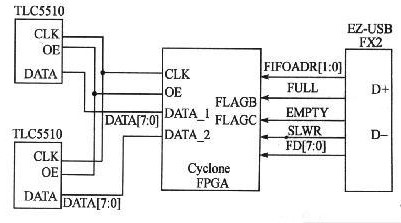

0 本系統(tǒng)主要分為兩個(gè)部分,一部分是由2片TLC5510和FPGA構(gòu)成的數(shù)據(jù)采集模塊,另一部分是由FPGA和EZ—USB FX2構(gòu)成的數(shù)據(jù)傳輸模塊。系統(tǒng)的框圖如圖1所示。

2019-05-08 08:10:00 3656

3656

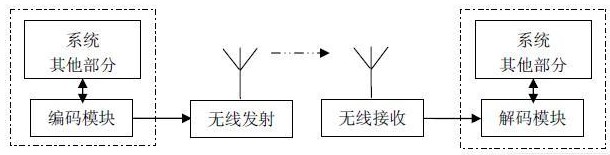

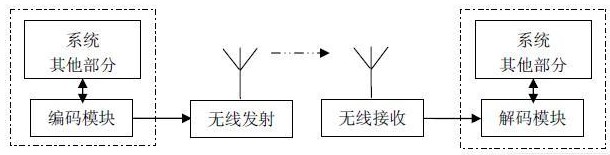

系統(tǒng)分為接收和發(fā)射兩部分,使用非編碼的無(wú)線發(fā)射模塊和接收模塊進(jìn)行無(wú)線數(shù)據(jù)的傳輸,發(fā)送和接收部分各自具有獨(dú)立的邏輯模塊進(jìn)行編碼或解碼,可以和系統(tǒng)其他部分進(jìn)行數(shù)據(jù)交互,如圖 1。

2019-05-10 08:30:00 2391

2391

實(shí)現(xiàn)RS-232電平和TTL/CMOS電平轉(zhuǎn)換可以用接口芯片來實(shí)現(xiàn),實(shí)現(xiàn)數(shù)據(jù)的串行到并行轉(zhuǎn)換用的是UART,它們是實(shí)現(xiàn)串行通信必不可少的兩個(gè)部分。雖然目前大部分處理器芯片中都集成了UART,但是一般

2019-10-18 07:54:00 2317

2317

中,采用AGC算法,可提高音頻信號(hào)系統(tǒng)和音頻信號(hào)輸出的穩(wěn)定性,解決了AGC調(diào)試后的信號(hào)失真問題。本文針對(duì)基于實(shí)用AGC算法的音頻信號(hào)處理方法與FPGA實(shí)現(xiàn),及其相關(guān)內(nèi)容進(jìn)行了分析研究。

2018-09-30 16:29:14 2957

2957

某魚雷聲自導(dǎo)的硬件系統(tǒng)使用了百兆網(wǎng)絡(luò)交換機(jī)實(shí)現(xiàn)DSP之間的互聯(lián)。交換機(jī)在MAC和PHY之間的接I=I是RMII,但DSP沒有相應(yīng)的外圍設(shè)備與它匹配。因此必須在FPGA中設(shè)計(jì)RMII的通訊模塊,完成DSP數(shù)據(jù)格式向RMII數(shù)據(jù)格式的轉(zhuǎn)化。在設(shè)計(jì)中將該通訊模塊分為發(fā)送狀態(tài)機(jī)和接收狀態(tài)機(jī)兩部分

2018-10-18 16:46:51 64

64 本文在研究了三層以太網(wǎng)交換技術(shù)后,設(shè)計(jì)了一種采用 FPGA 來實(shí)現(xiàn)以太口和ATM口之間的數(shù)據(jù)通道上HEC 模塊的實(shí)現(xiàn)方法。文中給出了詳細(xì)的設(shè)計(jì)方案,并論述了采用FPGA 設(shè)計(jì)的原因和思路。最后對(duì)設(shè)計(jì)的HEC 模塊進(jìn)行了測(cè)試,通過對(duì)測(cè)試結(jié)果的分析,對(duì)設(shè)計(jì)與實(shí)現(xiàn)的情況給予了總體評(píng)估。

2018-11-30 15:41:47 7

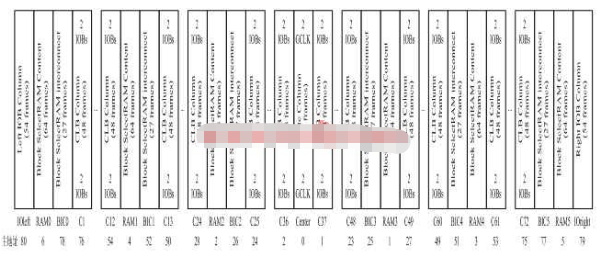

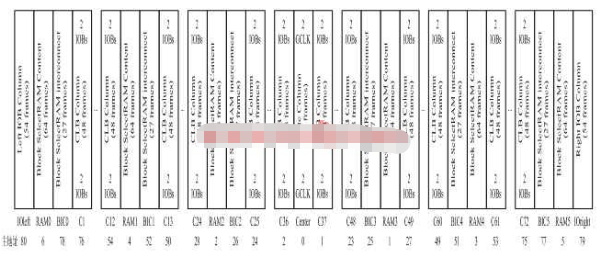

7 CLB(Configurable Logic Block):FPGA最基本的組成單元,可以實(shí)現(xiàn)基本的組合邏輯和時(shí)序電路。其中,LUT(Lookup Tables)是實(shí)現(xiàn)組合邏輯的部分,可以實(shí)現(xiàn)n個(gè)輸入的任意組合邏輯運(yùn)算(不同型號(hào)的FPGA有所不同,下圖的例子中為6個(gè)輸入)。

2019-09-27 15:18:06 7663

7663

中,采用AGC算法,可提高音頻信號(hào)系統(tǒng)和音頻信號(hào)輸出的穩(wěn)定性,解決了AGC調(diào)試后的信號(hào)失真問題。本文針對(duì)基于實(shí)用AGC算法的音頻信號(hào)處理方法與FPGA實(shí)現(xiàn),及其相關(guān)內(nèi)容進(jìn)行了分析研究。

2020-03-12 10:10:41 8301

8301

的實(shí)現(xiàn)方法,具體描述了發(fā)送、接收等模塊的設(shè)計(jì),恰當(dāng)使用了有限狀態(tài)機(jī),實(shí)現(xiàn)了FPGA上的UART的設(shè)計(jì),給出仿真結(jié)果。

2020-07-07 17:28:03 10

10 應(yīng)用FPGA動(dòng)態(tài)部分重構(gòu)功能使硬件設(shè)計(jì)更加靈活,可用于硬件的遠(yuǎn)程升級(jí)、系統(tǒng)容錯(cuò)和演化硬件以及通信平臺(tái)設(shè)計(jì)等。動(dòng)態(tài)部分重構(gòu)可以通過兩種方法實(shí)現(xiàn):基于模塊化設(shè)計(jì)方法(Module-Based

2020-07-29 17:10:33 1887

1887

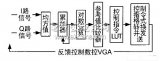

信號(hào)處理器)處理輸出為 IF 數(shù)字信號(hào)。IF 信號(hào)可以經(jīng)過 AGC 控制算法處理后控制 VGA 的增益。AGC 增益控制算法在數(shù)字部分來實(shí)現(xiàn),在本設(shè)計(jì)中,AGC 電路可以有效提高鏈路的動(dòng)態(tài)范圍(+25

2020-08-13 17:02:18 561

561

信號(hào)處理器)處理輸出為 IF 數(shù)字信號(hào)。IF 信號(hào)可以經(jīng)過 AGC 控制算法處理后控制 VGA 的增益。AGC 增益控制算法在數(shù)字部分來實(shí)現(xiàn),在本設(shè)計(jì)中,AGC 電路可以有效提高鏈路的動(dòng)態(tài)范圍(+25

2020-08-28 15:26:59 614

614

PCBA報(bào)價(jià)就一定是由這3部分來決定的。那么今天靖邦電子小編跟大家來分解一下,希望我得講解能夠?yàn)槟鷮?duì)于報(bào)價(jià)周期是多久有個(gè)簡(jiǎn)單的了解。 一、PCB板塊:PCB報(bào)價(jià)需要的制板資料和制板說明文件。如果資料齊全,把所有的資料梳理好,特殊工藝需要單獨(dú)收費(fèi)要多少錢

2020-09-08 11:29:42 1971

1971 本文接續(xù)上一篇《FPGA雜記基礎(chǔ)篇》,繼續(xù)為大家分享IP例化和幾個(gè)基于FPGA芯片實(shí)現(xiàn)的Demo工程。IP例化IP即是一個(gè)封裝好的模塊,集成在相應(yīng)的開發(fā)環(huán)境里面,以安路的TD軟件為例,不同系列的芯片集成了不同的IP模塊,可以通過軟件例化調(diào)用

2020-12-24 12:58:51 1048

1048 介紹了一種基于FPGA的多幅圖像融合疊加的設(shè)計(jì)與實(shí)現(xiàn),給出了其實(shí)現(xiàn)原理和模塊設(shè)計(jì)。設(shè)計(jì)包含12C控制器、數(shù)據(jù)緩沖和融合疊加處理輸出三部分。融合疊加處理包含絕對(duì)坐標(biāo)生成子模塊、相對(duì)坐標(biāo)生成與判斷子模塊

2021-01-26 15:57:00 18

18 介紹了一種電力線載波線路調(diào)制的現(xiàn)場(chǎng)可編程門陣列(FPGA)實(shí)現(xiàn)方案,并著重介紹了實(shí)現(xiàn)該方案的關(guān)鍵技術(shù)——積分梳狀(CIC)濾波器、有限沖擊響應(yīng)(FIR)濾波器和自動(dòng)增益控制(AGC)的FPGA實(shí)現(xiàn)。實(shí)踐表明,該方案切實(shí)可行,具有較強(qiáng)的實(shí)用性。

2021-01-27 16:38:02 17

17 針對(duì)圖像信號(hào)的基本特征設(shè)計(jì)了對(duì)于四路間歇性數(shù)據(jù)并行存儲(chǔ)方案,整個(gè)圖像采集存儲(chǔ)系統(tǒng)分為控制模塊和存儲(chǔ)模塊兩個(gè)部分:控制模塊主要是采用FPGA對(duì)圖像數(shù)據(jù)進(jìn)行并行接收、數(shù)據(jù)編碼、控制存儲(chǔ)、全程工作控制

2021-01-29 15:27:00 6

6 前幾天,臨危受命,幫幾個(gè)初學(xué)者的學(xué)生寫一個(gè)簡(jiǎn)易AM信號(hào)的FPGA實(shí)現(xiàn),以幫助他們搭建一個(gè)相對(duì)完整的系統(tǒng),測(cè)試他們的低速ADC,高速DAC,AGC控制等等模塊。本文的FPGA代碼已經(jīng)經(jīng)過上板測(cè)試,由于

2021-03-29 11:40:48 1943

1943

為了解決抗干擾導(dǎo)航接收機(jī)中數(shù)字干擾對(duì)消結(jié)果的動(dòng)態(tài)范圍過大問題,提出一種新的全數(shù)字式前饋?zhàn)詣?dòng)增益控制(AGC)算法.研究了算法中各個(gè)參數(shù)的設(shè)置方法,并指出現(xiàn)場(chǎng)可編程門陣列(FPGA)實(shí)現(xiàn)技巧.仿真

2021-04-01 10:27:31 21

21 功能.文中將軟硬件實(shí)現(xiàn)的順序形態(tài)圖像處理圖片在處理效果和速度兩個(gè)方面作了比較.算法在FPGA芯片上的高速實(shí)現(xiàn)特征使數(shù)學(xué)形態(tài)學(xué)在圖像實(shí)時(shí)處理領(lǐng)域的應(yīng)用成為可能。

2021-04-01 11:21:46 8

8 基于FPGA的UART模塊設(shè)計(jì)與實(shí)現(xiàn)介紹說明。

2021-06-01 09:43:30 19

19 FPGA-SoC芯片中EDAC模塊的設(shè)計(jì)與實(shí)現(xiàn)(深圳市宇衡源電源技術(shù))-該文檔為FPGA-SoC芯片中EDAC模塊的設(shè)計(jì)與實(shí)現(xiàn)簡(jiǎn)介文檔,是一份還算不錯(cuò)的參考文檔,感興趣的可以下載看看,,,,,,,,,,,,,,,,,

2021-09-27 14:32:18 13

13 DDS基于FPGA的DDSSPI系統(tǒng)結(jié)構(gòu)功能實(shí)現(xiàn):在SPI接口下掛接上DDS模塊,通過單片機(jī)向FPGA發(fā)送頻率字實(shí)現(xiàn)任意頻率正弦波的波形,并通過DAC模塊輸出單片機(jī)部分通過按鍵輸入待產(chǎn)生的信號(hào)頻率

2021-12-01 17:36:17 9

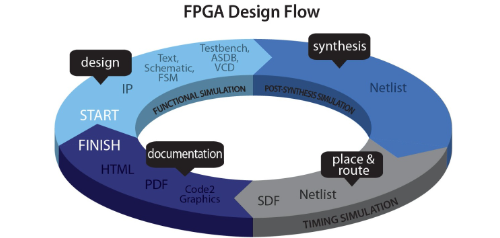

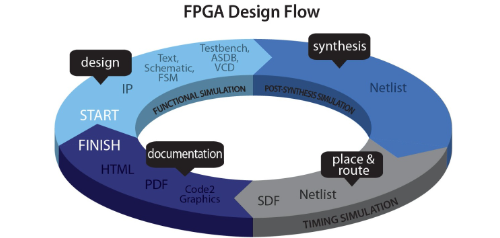

9 FPGA是一種可編程芯片,因此FPGA的設(shè)計(jì)方法包括硬件設(shè)計(jì)和軟件設(shè)計(jì)兩部分。硬件包括FPGA芯片電路、存儲(chǔ)器、輸入輸出接口電路等器件。軟件是對(duì)應(yīng)的VHDL程序和VerilogHDL程序。FPGA

2023-07-03 14:35:58 1101

1101

高通今年8月發(fā)表了不冷不熱的銷售展望,預(yù)告了智能手機(jī)需求的蕭條。高通表示,正在采取節(jié)省費(fèi)用的措施,并已經(jīng)開始裁員。高通上季度的結(jié)構(gòu)調(diào)整費(fèi)用為2.85億美元,其中大部分來自退休金,預(yù)計(jì)還會(huì)有追加裁員。

2023-10-13 11:23:18 469

469

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論