Verilog語言和VHDL語言是兩種不同的硬件描述語言,但并非所有人都同時(shí)精通兩種語言,所以在某些時(shí)候,需要把Verilog代碼轉(zhuǎn)換為VHDL代碼。本文以通用的XHDL工具為例對(duì)Verilog轉(zhuǎn)換

2020-11-10 15:41:11 10083

10083

我是剛開始學(xué)FPGA,現(xiàn)在對(duì)其verilog語言還不是很懂。下面題目:設(shè)計(jì)一個(gè)十進(jìn)制的加法計(jì)數(shù)器,功能包含復(fù)位信號(hào),置位信號(hào),每個(gè)時(shí)鐘的正跳變沿計(jì)數(shù)器加一。計(jì)數(shù)0-99即可。請(qǐng)幫忙給個(gè)參考的程序。

2012-05-11 23:03:24

個(gè)微型電腦,FPGA就是是一種邏輯電路。由于后者是硬件電路,通電了就運(yùn)行。所以其速度比單片機(jī)快得多了。常常應(yīng)用于處理數(shù)據(jù)需求較高的器件上。編程語言區(qū)別:FPGA是用Verilog或VHDL 硬件描述語言

2019-09-23 11:07:31

Verilog HDL硬件描述語言

2013-01-13 14:40:20

Verilog HDL硬件描述語言(非常經(jīng)典的教材)FPGA軟件無線電開發(fā)(全階視頻教程+開發(fā)板+實(shí)例)詳情鏈接:http://url.elecfans.com/u/5e4a12f2ba

2013-07-22 14:50:03

Verilog HDL語言有什么優(yōu)越性Verilog HDL語言在FPGA/CPLD開發(fā)中的應(yīng)用

2021-04-23 07:02:03

關(guān)鍵字:Altera 、FPGA、軟硬件協(xié)調(diào)設(shè)計(jì)(Verilog & C)、CPU、總線、外設(shè)FPGA硬件結(jié)構(gòu)知識(shí)Verilog HDL語言編程基礎(chǔ)FPGA常用開發(fā)工具 SOPC硬件系統(tǒng)開發(fā)SOPC軟件系統(tǒng)開發(fā)Avalon總線規(guī)范Nios II外設(shè)及其編程 七段數(shù)碼管時(shí)鐘...

2021-12-22 08:06:06

Verilog語言在FPGA中運(yùn)用的簡單實(shí)例有什么,求舉例?

2016-03-16 00:59:00

在看FPGA的資料,有一個(gè)關(guān)于Verilog語言的問題突然想不明白~{:16:}關(guān)于時(shí)序的,Verilog中,判斷if成立的條件是當(dāng)前值(感覺是電平式),還是過去值(感覺是時(shí)序)?例如:if(a==2) out

2013-03-25 21:31:58

Verilog_HDL硬件描述語言 FPGA的資料

2013-02-26 14:03:42

本帖最后由 lee_st 于 2017-10-31 08:46 編輯

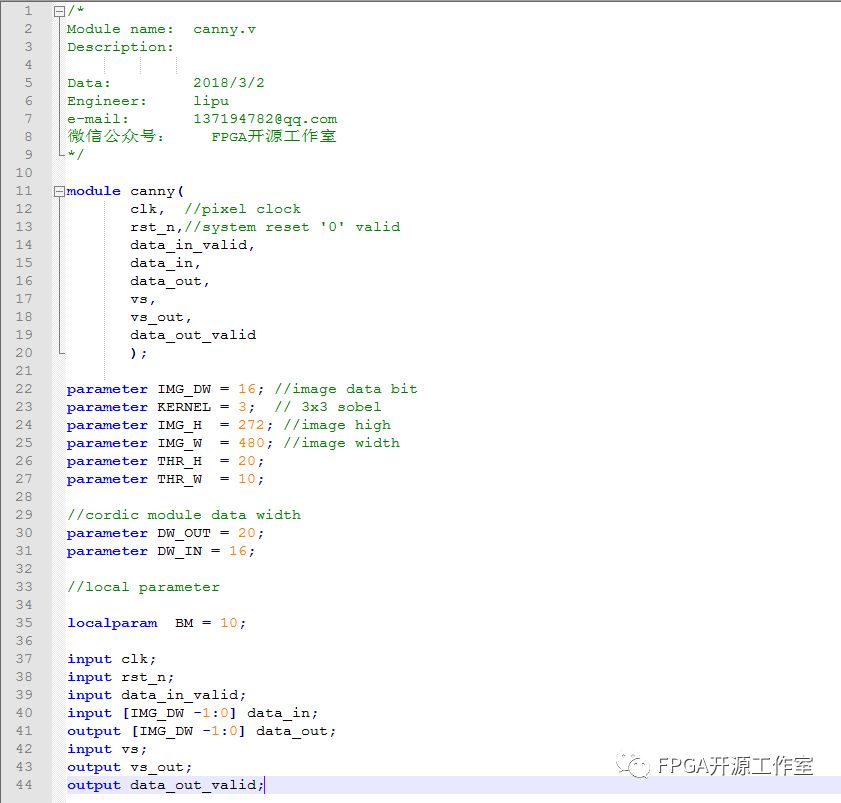

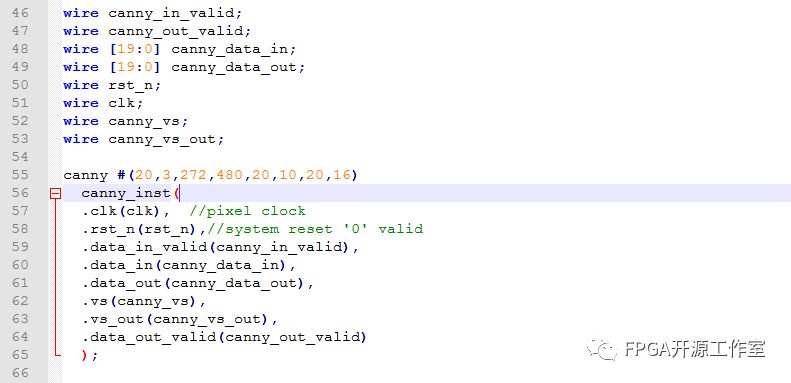

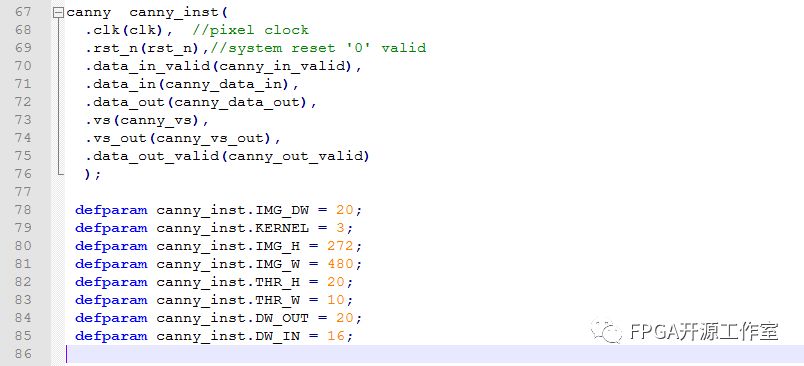

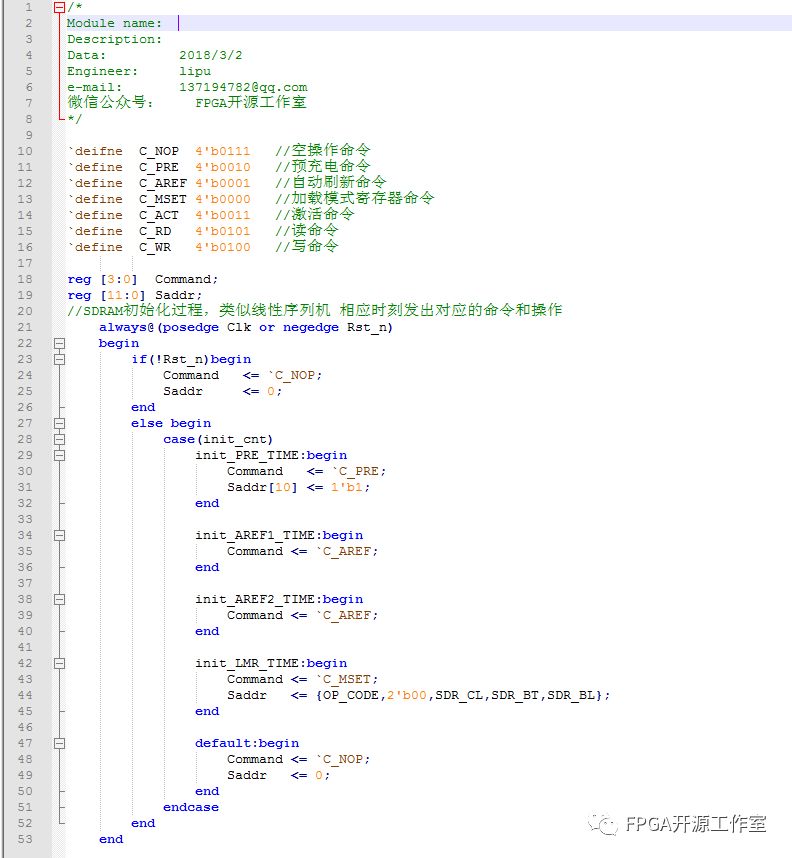

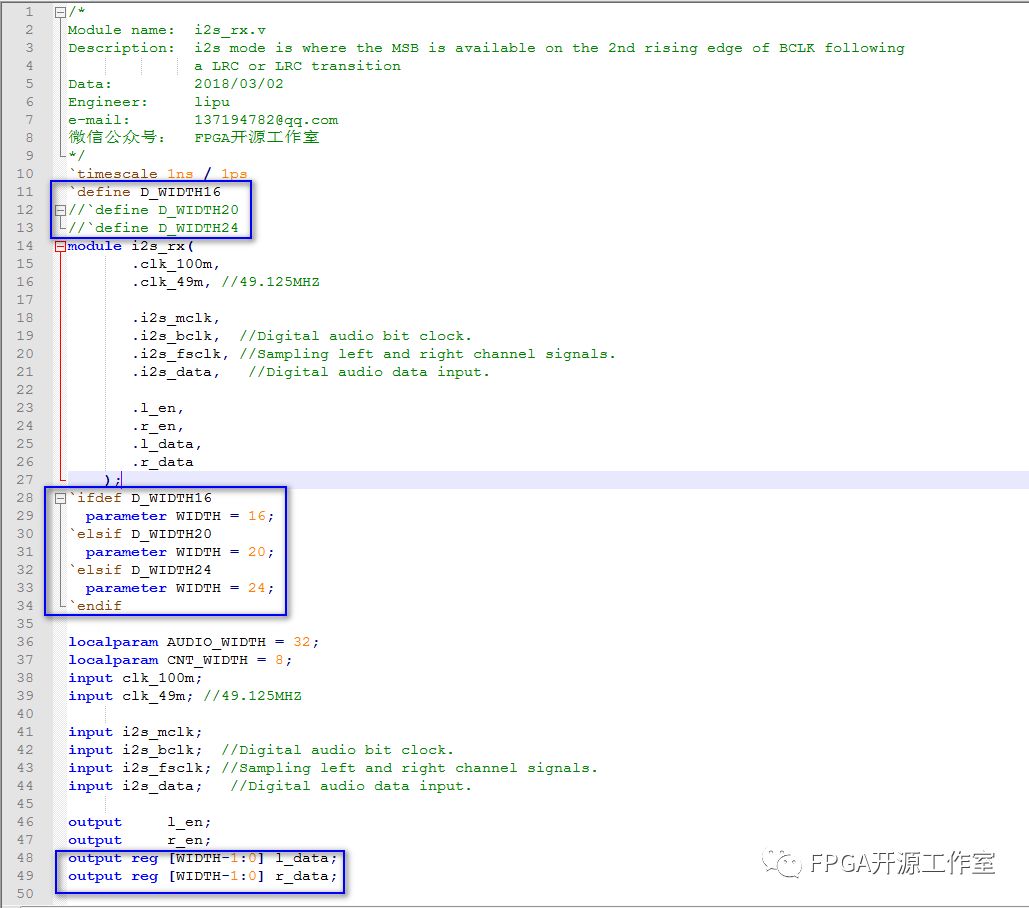

Verilog語法基礎(chǔ)講解之參數(shù)化設(shè)計(jì)

2017-10-21 20:56:17

verilog+hdl硬件描述語言 初學(xué)者的福音 幫助廣大初學(xué)者步入此行

2013-08-12 23:47:12

verilog硬件描述語言課程講義

2012-08-06 11:35:33

硬件描述語言Verilog(第四版)

2017-09-26 15:27:49

請(qǐng)問一下,現(xiàn)在c語言編程FPGA并不是十分的廣泛,那么,以后未來的趨勢是不是使用c語言來進(jìn)行FPGA編程,就是DSP,ARM一樣呢?那Verilog和vhdl會(huì)不會(huì)被淘汰啊?

2015-04-15 16:44:11

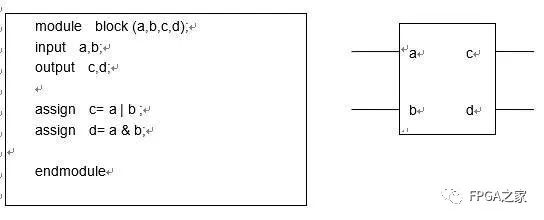

。Verilog HDL 之所以成為和 VHDL 并駕齊驅(qū)的硬件描述語言,是因?yàn)樗哂腥缦绿攸c(diǎn):? 基本邏輯門和開關(guān)級(jí)基本結(jié)構(gòu)模型都內(nèi)置在語言中;? 可采用多種方式對(duì)設(shè)計(jì)建模,這些方式包括行為描述方式

2018-09-18 09:33:31

`【5G關(guān)鍵技術(shù)】FPGA無線通信開發(fā)第3期:Verilog——最“硬”的語言免費(fèi)報(bào)名鏈接:http://t.elecfans.com/live/841.html課程主題簡介及亮點(diǎn):直播主題

2019-05-17 17:17:03

硬件描述語言Verilog,西安科大教學(xué)課件,總共包括完整八個(gè)章節(jié)學(xué)習(xí)內(nèi)容。具體每章節(jié)內(nèi)容如下第一章:Verilog HDL數(shù)字集成電路設(shè)計(jì)方法概述第二章:Verilog HDL基礎(chǔ)知識(shí)第三章

2021-03-30 14:31:41

VHDL不是很直觀,一般認(rèn)為至少要半年以上的專業(yè)培訓(xùn)才能掌握。近10年來,EDA界一直在對(duì)數(shù)字邏輯設(shè)計(jì)中究竟用哪一種硬件描述語言爭論不休,目前在美國,高層次數(shù)字系統(tǒng)設(shè)計(jì)領(lǐng)域中,應(yīng)用Verilog和VHDL

2020-09-21 16:48:48

本帖最后由 鋯石科技 于 2016-11-15 16:22 編輯

本文檔主要包含了 Verilog HDL語言 的八個(gè)關(guān)鍵問題它們分別是:① Verilog的抽象級(jí)別② Verilog的模塊化

2016-08-17 05:56:55

FPGA為平臺(tái)怎么測量脈沖寬度的verilog語言

2017-03-21 15:16:01

超過VHDL。從學(xué)習(xí)的角度來講,Verilog相對(duì)VHDL有著快速上手、易于使用的特點(diǎn),博得了更多工程師的青睞。即便是從來沒有接觸過Verilog的初學(xué)者,只要憑著一點(diǎn)C語言的底子加上一些硬件

2017-09-26 21:07:34

`相對(duì)于C語言,基于繁瑣的VHDL等等,圖像化編程語言可以開發(fā)FPGA,完成信號(hào)的觸發(fā)以及數(shù)據(jù)的采集等等內(nèi)容`

2017-01-20 11:40:02

基于Verilog語言的實(shí)用FPGA設(shè)計(jì)(美)科夫曼

2017-09-30 09:18:21

介紹了等精度測量頻率的原理,利用Verilog硬件描述語言設(shè)計(jì)實(shí)現(xiàn)了頻率計(jì)內(nèi)部功能模塊,對(duì)傳統(tǒng)的等精度測量方法進(jìn)行了改進(jìn),增加了測量脈沖寬度的功能;采用AT89S51單片機(jī)進(jìn)行數(shù)據(jù)運(yùn)算處理,利用

2011-03-07 12:44:31

有沒有人對(duì)如何用參數(shù)化加法器樹編寫Verilog有任何建議,輸入參數(shù)是操作數(shù)的數(shù)量?加布里埃爾以上來自于谷歌翻譯以下為原文Does anyone have any suggestions

2019-04-25 13:28:42

學(xué)習(xí)fpga我用的verilog語言,怎么模塊化呢????

2013-11-21 23:11:32

本人小菜鳥,開始學(xué)FPGA的時(shí)候?qū)W的Verilog語言,后來因?yàn)檎n題組前期的工作都是VHDL就該學(xué)VHDL了。最近聽了幾個(gè)師兄的看法,說國內(nèi)用VHDL的已經(jīng)很少了,建議我還是堅(jiān)持用Verilog,小菜現(xiàn)在好糾結(jié),請(qǐng)問到底應(yīng)該用哪種語言呢?望各位大神指點(diǎn)!

2015-07-08 10:07:56

最近在做個(gè)課題,需要用FPGA中的verilog語言實(shí)現(xiàn)BPSK調(diào)制,fpga不是很會(huì),望大神指導(dǎo)下,急求代碼啊!謝謝

2013-03-06 18:12:36

)領(lǐng)域中的一種半定制電路而出現(xiàn)的,既解決了定制電路的不足,又克服了原有可編程器件門電路數(shù)有限的缺點(diǎn)。HDL硬件描述語言(HDL)是一種用來設(shè)計(jì)數(shù)字邏輯系統(tǒng)和描述數(shù)字電路的語言,常用的主要有VHDL、Verilog HDL、System Verilog 和 System C。VHDL是一種用于電路設(shè)計(jì)的高級(jí)

2021-12-22 07:39:43

在本篇里,我們討論 Verilog 語言的綜合問題,Verilog HDL (Hardware Description Language) 中文名為硬件描述語言,而不是硬件設(shè)計(jì)語言。這個(gè)名稱提醒我們

2021-07-29 07:42:25

如何使用Verilog硬件描述語言實(shí)現(xiàn)AES密碼算法?

2021-04-14 06:29:10

本書簡要介紹了Verilog硬件描述語言的基礎(chǔ)知識(shí),包括語言的基本內(nèi)容和基本結(jié)構(gòu) ,以及利用該語言在各種層次上對(duì)數(shù)字系統(tǒng)的建模方法。書中列舉了大量實(shí)例,幫助讀者掌握語

2006-03-27 23:44:08 101

101 本書簡要介紹了Verilog硬件描述語言的基礎(chǔ)知識(shí),包括語言的基本內(nèi)容和基本結(jié)構(gòu) ,以及利用該語言在各種層次上對(duì)數(shù)字系統(tǒng)的建模方法。書中列舉了大量實(shí)例,幫助讀者掌握語言

2009-07-20 11:36:35 0

0 This manual describes the Verilog portion of Synopsys FPGACompiler II / FPGA Express application

2009-07-23 10:01:29 79

79 采用 Verilog HDL 語言在Altera 公司的FPGA 芯片上實(shí)現(xiàn)了RISC_CPU 的關(guān)鍵部件狀態(tài)控制器的設(shè)計(jì),以及在與其它各種數(shù)字邏輯設(shè)計(jì)方法的比較下,顯示出使用Verilog HDL語言的優(yōu)越性.關(guān)鍵詞

2009-08-21 10:50:05 69

69 本書簡要介紹了Verilog 硬件描述語言的基礎(chǔ)知識(shí),包括語言的基本內(nèi)容和基本結(jié)構(gòu),以及利用該語言在各種層次上對(duì)數(shù)字系統(tǒng)的建模方法。書中列舉了大量實(shí)例,幫助讀者掌握

2010-07-02 14:55:51 124

124 摘 要:通過設(shè)計(jì)實(shí)例詳細(xì)介紹了用Verilog HDL語言開發(fā)FPGA/CPLD的方法,并通過與其他各種輸入方式的比較,顯示出使用Verilog HDL語言的優(yōu)越性。

2009-06-20 11:51:28 1857

1857

Verilog HDL語言簡介

1.什么是Verilog HDLVerilog HDL是硬件描述語言的一種,用于數(shù)

2010-02-09 08:59:33 3609

3609 VHDL和Verilog HDL語言對(duì)比

Verilog HDL和VHDL都是用于邏輯設(shè)計(jì)的硬件描述語言,并且都已成為IEEE標(biāo)準(zhǔn)。VHDL是在1987年成為IEEE標(biāo)準(zhǔn),Verilog HDL

2010-02-09 09:01:17 10317

10317 Verilog HDL與VHDL及FPGA的比較分析. Verilog HDL優(yōu)點(diǎn):類似C語言,上手容易,靈活。大小寫敏感。在寫激勵(lì)和建模方面有優(yōu)勢。

2011-01-11 10:45:29 1182

1182 在我國使用Verilog HDL的公司比使用VHDL的公司多。從EDA技術(shù)的發(fā)展上看,已出現(xiàn)用于CPLD/FPGA設(shè)計(jì)的硬件C語言編譯軟件,雖然還不成熟,應(yīng)用極少,但它有可能會(huì)成為繼VHDL和Verilog之后,設(shè)計(jì)大規(guī)模CPLD/FPGA的又一種手段。

2011-03-12 11:21:20 1686

1686 給出了一種基于FPGA的分頻電路的設(shè)計(jì)方法.根據(jù)FPGA器件的特點(diǎn)和應(yīng)用范圍,提出了基于Verilog的分頻方法.該方法時(shí)于在FPGA硬件平臺(tái)上設(shè)計(jì)常用的任意偶數(shù)分頻、奇數(shù)分頻、半整數(shù)分頻

2011-11-09 09:49:33 355

355 verilog硬件描述語言課程講義

2012-05-21 15:01:29 33

33 電子發(fā)燒友網(wǎng)站提供《最新版硬件描述語言Verilog (第四版).txt》資料免費(fèi)下載

2014-08-14 17:52:40 0

0 Verilog硬件描述語言參考手冊(cè),Verilog語法內(nèi)容介紹

2015-11-12 17:20:37 0

0 基于verilog語言的數(shù)字頻率計(jì)設(shè)計(jì)基于verilog語言的數(shù)字頻率計(jì)設(shè)計(jì)基于verilog語言的數(shù)字頻率計(jì)設(shè)計(jì)基于verilog語言的數(shù)字頻率計(jì)設(shè)計(jì)

2015-12-08 15:57:23 0

0 Verilog HDL硬件描述語言

有需要的下來看看

2015-12-29 15:31:27 0

0 本章介紹Verilog HDL語言的發(fā)展歷史和它的主要能力。verilog相關(guān)教程材料,有興趣的同學(xué)可以下載學(xué)習(xí)

2016-04-25 16:09:32 14

14 本章介紹Verilog HDL的基本要素,包括標(biāo)識(shí)符、注釋、數(shù)值、編譯程序指令、系統(tǒng)任務(wù)和系統(tǒng)函數(shù)。另外,本章還介紹了Verilog硬件描述語言中的兩種數(shù)據(jù)類型。verilog相關(guān)教程材料,有興趣的同學(xué)可以下載學(xué)習(xí)。

2016-04-25 16:09:32 16

16 VHDL語言編程學(xué)習(xí)Verilog硬件描述語言

2016-09-01 15:27:27 0

0 Verilog HDL硬件描述語言,感興趣的小伙伴們可以瞧一瞧。

2016-11-11 11:20:11 11

11 硬件描述語言Verilog(第四版),感興趣的小伙伴們可以瞧一瞧。

2016-11-11 11:20:11 0

0 因?yàn)?b class="flag-6" style="color: red">Verilog是一種硬件描述語言,所以在寫Verilog語言時(shí),首先要有所要寫的module在硬件上如何實(shí)現(xiàn)的概念,而不是去想編譯器如何去解釋這個(gè)module

2017-02-11 16:18:11 2780

2780

本章介紹Verilog HDL的基本要素,包括標(biāo)識(shí)符、注釋、數(shù)值、編譯程序指令、系統(tǒng)任務(wù)和系統(tǒng)函數(shù)。另外,本章還介紹了Verilog硬件描述語言中的兩種數(shù)據(jù)類型。

3.1 標(biāo)識(shí)符

2017-02-11 17:01:07 1713

1713

基于FPGA Verilog-HDL語言的串口設(shè)計(jì)

2017-02-16 00:08:59 35

35 詳細(xì)介紹了verilog語言,很容易看懂,并配有示例

2017-05-03 09:09:57 0

0 FPGA verilog 相關(guān)設(shè)計(jì)實(shí)踐

2017-09-06 11:19:34 32

32 Verilog HDL是一種硬件描述語言,以文本形式來描述數(shù)字系統(tǒng)硬件的結(jié)構(gòu)和行為的語言,用它可以表示邏輯電路圖、邏輯表達(dá)式,還可以表示數(shù)字邏輯系統(tǒng)所完成的邏輯功能。而C語言是一門通用計(jì)算機(jī)編程語言,應(yīng)用廣泛。

2017-12-08 16:43:30 11805

11805 Verilog HDL作為現(xiàn)在最流行的FPGA開發(fā)語言,當(dāng)然是入門基礎(chǔ)。

2019-02-18 14:47:00 10320

10320 中國大學(xué)MOOC

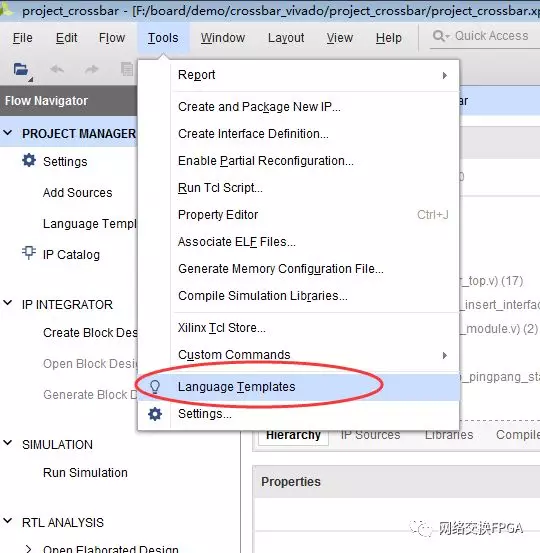

本課程以目前流行的Xilinx 7系列FPGA的開發(fā)為主線,全面講解FPGA的原理及電路設(shè)計(jì)、Verilog HDL語言及VIVADO的應(yīng)用,并循序漸進(jìn)地從組合邏輯、時(shí)序邏輯的開發(fā)開始,深入到FPGA的基礎(chǔ)應(yīng)用、綜合應(yīng)用和進(jìn)階應(yīng)用。

2019-08-06 06:12:00 3450

3450

本課程以目前流行的Xilinx 7系列FPGA的開發(fā)為主線,全面講解FPGA的原理及電路設(shè)計(jì)、Verilog HDL語言及VIVADO的應(yīng)用,并循序漸進(jìn)地從組合邏輯、時(shí)序邏輯的開發(fā)開始,深入到FPGA的基礎(chǔ)應(yīng)用、綜合應(yīng)用和進(jìn)階應(yīng)用。

2019-12-05 07:06:00 2166

2166

大家都知道軟件設(shè)計(jì)使用軟件編程語言,例如我們熟知的C、Java等等,而FPGA設(shè)計(jì)使用的是HDL語言,例如VHDL和Verilog HDL。說的直白點(diǎn),FPGA的設(shè)計(jì)就是邏輯電路的實(shí)現(xiàn),就是把我們

2019-12-05 07:11:00 1497

1497

Verilog與C語言還是存在許多差別。另外,作為一種與普通計(jì)算機(jī)編程語言不同的硬件描述語言,它還具有一些獨(dú)特的語言要素,例如向量形式的線網(wǎng)和寄存器、過程中的非阻塞賦值等。總的來說,具備C語言的設(shè)計(jì)人員將能夠很快掌握Verilog硬件描述語言。

2019-12-11 07:02:00 1446

1446

本課程以目前流行的Xilinx 7系列FPGA的開發(fā)為主線,全面講解FPGA的原理及電路設(shè)計(jì)、Verilog HDL語言及VIVADO的應(yīng)用,并循序漸進(jìn)地從組合邏輯、時(shí)序邏輯的開發(fā)開始,深入到FPGA的基礎(chǔ)應(yīng)用、綜合應(yīng)用和進(jìn)階應(yīng)用。

2019-12-02 07:10:00 2914

2914

大家都知道軟件設(shè)計(jì)使用軟件編程語言,例如我們熟知的C、Java等等,而FPGA設(shè)計(jì)使用的是HDL語言,例如VHDL和Verilog HDL。說的直白點(diǎn),FPGA的設(shè)計(jì)就是邏輯電路的實(shí)現(xiàn),就是把我們

2019-12-05 07:10:00 2977

2977

本文檔的主要內(nèi)容詳細(xì)介紹的是基于Verilog硬件描述語言的IEEE標(biāo)準(zhǔn)硬件描述語言資料合集免費(fèi)下載:1995、2001、2005;SystemVerilog標(biāo)準(zhǔn):2005、2009

2020-06-18 08:00:00 10

10 Verilog HDL簡稱Verilog,它是使用最廣泛的硬件描述語言。

2020-03-22 17:29:00 4357

4357 Verilog是硬件描述語言,在編譯下載到FPGA之后,會(huì)生成電路,所以Vreilog是并行運(yùn)行的; C語言是軟件編程語言,編譯下載到單片機(jī)之后,是存儲(chǔ)器中的一組指令。而單片機(jī)處理軟件指令需要

2020-05-13 08:00:00 13

13 經(jīng)常看到不少人在論壇里發(fā)問,FPGA是不是用C語言開發(fā)的?國外有些公司專注于開發(fā)解決編譯器這方面問題,目的讓其能夠達(dá)到用C語言替代VHDL語言的目的,也開發(fā)出了一些支持用c語言對(duì)FPGA進(jìn)行編程的開發(fā)工具。但在使用多的FPGA編程語言還是verilog和VHDL語言,一般不使用C語言進(jìn)行編程。

2020-07-29 16:37:37 23118

23118 的是硬件描述語言。最為流行的硬件描述語言有兩種Verilog HDL/VHDL,均為IEEE標(biāo)準(zhǔn)。Verilog HDL具有C語言基礎(chǔ)就很容易上手,而VHDL語言則需要Ada編程基礎(chǔ)。另外Verilog

2020-09-01 11:47:09 4002

4002

Verilog是一種流行的硬件描述語言,他是由工業(yè)界開發(fā)的,1984年,Verilog作為一種私用的硬件描述語言,由Gateway Design Automation公司給出,1988

2020-09-11 17:24:00 12

12 本文檔的主要內(nèi)容詳細(xì)介紹的是Verilog硬件描述語言的學(xué)習(xí)課件免費(fèi)下載。

2021-01-22 12:13:40 17

17 本Verilog 硬件描述語言參考手冊(cè)是根據(jù)IEEE 的標(biāo)準(zhǔn)“Verilog 硬件描述語言參考手冊(cè)1364-1995”編寫的。OVI (Open Verilog International) 根據(jù)

2021-02-05 16:24:00 72

72 眾所周知,用于FPGA開發(fā)的硬件描述語言(HDL)主要有兩種:Verilog和VHDL。

2021-06-15 16:12:04 4293

4293 VHDL與Verilog硬件描述語言在數(shù)字電路的設(shè)計(jì)中使用的非常普遍,無論是哪種語言,仿真都是必不可少的。而且隨著設(shè)計(jì)復(fù)雜度的提高,仿真工具的重要性就越來越凸顯出來。在一些

2021-08-04 14:16:44 3307

3307 知乎上刷到一個(gè)問題,問性能最強(qiáng)的編程語言是什么?看到高贊回答到是Verilog,然后在評(píng)論區(qū)就引發(fā)了一場Verilog到底算不算編程語言的爭論,我覺得比較有意思,所以就也打算嘮嘮這個(gè)事情。 趁著最近

2021-08-23 14:30:49 5558

5558 FPGA CPLD中的Verilog設(shè)計(jì)小技巧(肇慶理士電源技術(shù)有限)-FPGA CPLD中的Verilog設(shè)計(jì)小技巧? ? ? ? ? ? ? ? ?

2021-09-18 16:49:18 35

35 要想深入理解Verilog就必須正視Verilog語言同時(shí)具備硬件特性和軟件特性。

2022-07-07 09:54:48 1124

1124 HDLBits 是一組小型電路設(shè)計(jì)習(xí)題集,使用 Verilog/SystemVerilog 硬件描述語言 (HDL) 練習(xí)數(shù)字硬件設(shè)計(jì)~

2022-08-31 09:06:59 1168

1168 FPGA需要良好的數(shù)電模電基礎(chǔ),verilog需要良好C語言基礎(chǔ)。

2023-05-11 17:30:07 1308

1308

FPGA需要良好的數(shù)電模電基礎(chǔ),verilog需要良好C語言基礎(chǔ)。

2023-05-22 15:04:29 484

484

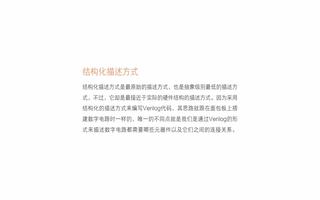

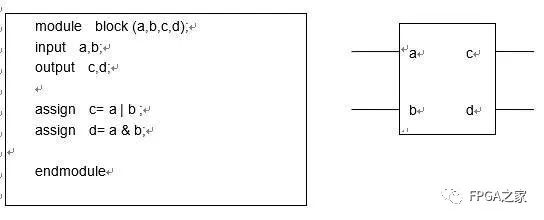

Verilog HDL是一種用于數(shù)字系統(tǒng)設(shè)計(jì)的語言。用Verilog HDL描述的電路設(shè)計(jì)就是該電路的Verilog HDL模型也稱為模塊。Verilog HDL既是一種行為描述的語言也是一種結(jié)構(gòu)

2023-05-22 15:52:42 557

557

Verilog HDL是一種用于數(shù)字系統(tǒng)設(shè)計(jì)的語言。用Verilog HDL描述的電路設(shè)計(jì)就是該電路的Verilog HDL模型也稱為模塊。Verilog HDL既是一種行為描述的語言也是一種結(jié)構(gòu)

2023-05-22 15:53:23 531

531

要想深入理解Verilog就必須正視Verilog語言同時(shí)具備硬件特性和軟件特性。在當(dāng)下的教學(xué)過程中,教師和教材都過于強(qiáng)調(diào)Verilog語言的硬件特性和可綜合特性。將Verilog語言的行為級(jí)語法

2023-05-25 15:10:21 642

642

要想深入理解Verilog就必須正視Verilog語言同時(shí)具備硬件特性和軟件特性。在當(dāng)下的教學(xué)過程中,教師和教材都過于強(qiáng)調(diào)Verilog語言的硬件特性和可綜合特性。將Verilog語言的行為級(jí)語法

2023-05-25 15:10:44 576

576

本專題為FPGA設(shè)計(jì)語言技術(shù)專題,像 Verilog 和 VHDL 之類的硬件描述語言 (HDL) 主要用于描述硬件行為,以便將其轉(zhuǎn)換為由組合門電路和時(shí)序元件組成的數(shù)字塊。為了驗(yàn)證 HDL 中的硬件

2023-10-07 16:30:33

Verilog是一種硬件描述語言,用于描述數(shù)字電路的行為和結(jié)構(gòu)。與其他編程語言相比,Verilog具有與硬件緊密結(jié)合的特點(diǎn),因此其接口機(jī)制也有一些與眾不同之處。本文將詳細(xì)介紹Verilog與其他編程

2024-02-23 10:22:37 145

145 FPGA芯片主要使用的編程語言包括Verilog HDL和VHDL。這兩種語言都是硬件描述語言,用于描述數(shù)字系統(tǒng)的結(jié)構(gòu)和行為。

2024-03-14 16:07:38 85

85 fpga用的是什么編程語言 FPGA(現(xiàn)場可編程邏輯門陣列)主要使用的編程語言是硬件描述語言(HDL)。在眾多的HDL中,Verilog HDL和VHDL是最常用的兩種。 Verilog HDL

2024-03-14 17:09:32 223

223 FPGA(現(xiàn)場可編程門陣列)的編程主要使用硬件描述語言(HDL),其中最常用的是Verilog HDL和VHDL。

2024-03-14 18:17:17 549

549 FPGA(現(xiàn)場可編程門陣列)的編程涉及到三種主要的硬件描述語言(HDL):VHDL(VHSIC Hardware Description Language)、Verilog以及SystemVerilog。這些語言在FPGA設(shè)計(jì)和開發(fā)過程中扮演著至關(guān)重要的角色。

2024-03-15 14:36:01 89

89 FPGA(現(xiàn)場可編程門陣列)的通用語言主要是指用于描述FPGA內(nèi)部邏輯結(jié)構(gòu)和行為的硬件描述語言。目前,Verilog HDL和VHDL是兩種最為廣泛使用的FPGA編程語言。

2024-03-15 14:36:34 87

87 功能,從而實(shí)現(xiàn)對(duì)數(shù)字電路的高效定制。FPGA語言主要包括VHDL(VHSIC Hardware Description Language)和Verilog等,這些語言具有強(qiáng)大的描述能力,能夠精確地定義硬件的每一個(gè)細(xì)節(jié),從而實(shí)現(xiàn)復(fù)雜的數(shù)字系統(tǒng)設(shè)計(jì)。

2024-03-15 14:50:26 166

166

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論