在規(guī)劃電源系統(tǒng)時,設計人員必須考慮電壓軌、電壓電平以及大電流需求。負載點轉(zhuǎn)換器將是重要組件。

隨著半導體公司不斷推出更加高級的器件,電路設計人員要找到確保其設計支持最高性能的最佳途徑、充分發(fā)揮這些全新IC的優(yōu)勢,將不斷面臨各種挑戰(zhàn)。為了充分發(fā)揮最高級FPGA器件的最佳性能,在系統(tǒng)中創(chuàng)建穩(wěn)健可靠的電源是一經(jīng)常被忽視,卻又至關(guān)重要的步驟。

賽靈思7系列FPGA可提供前所未有的低功耗與高性能以及移植設計的便捷路徑。該創(chuàng)新系列FPGA采用28納米TSMC HPL(高性能低功耗)工藝,與同類競爭FPGA相比,功耗銳降50%。

但隨著FPGA容量與性能的提升,F(xiàn)PGA的I/O資源正日益成為主要性能瓶頸。雖然實際晶體管數(shù)量每年都在翻番,但FPGA晶片尺寸卻或多或少地保持不變。這對將信號從芯片輸入輸出的I/O來說是個問題,因為I/O只能以線性方式增長,這為設法創(chuàng)建更大帶寬系統(tǒng)的設計人員帶來了大量的布局、信號完整性以及功耗挑戰(zhàn)。為解決這些問題,賽靈思在其業(yè)界一流的器件中采用極其高級的數(shù)千兆位收發(fā)器(MGT)I/O模塊。例如,Virtex?-7 HT FPGA使用96個13.1Gbps收發(fā)器集提供2.78Tbps的最大帶寬。

隨著FPGA的功能日益強大,電源要求也變得更加復雜。對于當前設計而言,各團隊必須考慮對應每個電路與功能模塊的多個電壓軌、電壓電平以及大電流需求。下面我們將深入討論有關(guān)Virtex-7 FPGA的電源需求。

輸出電壓設置的準確性

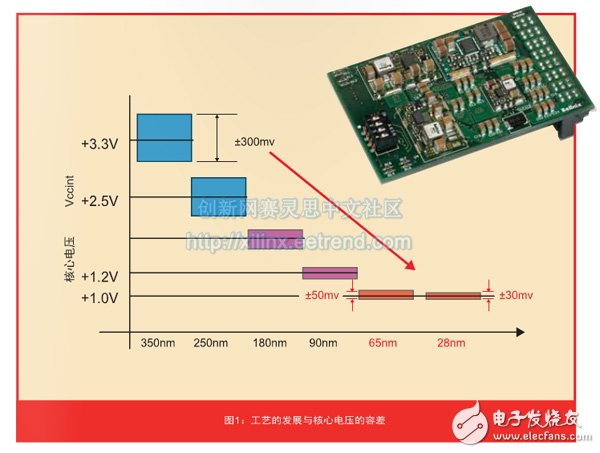

隨著半導體制造工藝技術(shù)的不斷發(fā)展,半導體的密度與性能,尤其是FPGA的密度和性能,取得了長足發(fā)展。同時,半導體公司也一直在降低其器件的核心電壓。

這兩個因素進一步為電源設計帶來了挑戰(zhàn),使設計人員難以選擇合適的電源電路。電路板布局與制造技術(shù)不足以管理幾毫伏內(nèi)的電壓,但電源系統(tǒng)必須具備可測量的準確性與可靠性。如此一來,設計團隊在設計電源系統(tǒng)時,就必須將電源特性與器件特性納入綜合考慮事項。。例如,1V核心電壓具有+/-30 mV的電壓容差,如果電流以10A為單位進行變化,就會在5毫歐電源線上出現(xiàn)50mV的壓降(見圖1)。這樣在電路板設計過程中,就不容易在所有環(huán)境下管理電源電壓,使之不超過容差值。此外,如果設計團隊在使用負載點(POL)電源,它們不但需要極高的精確度,不超出+/-1%,而且還要具備高速瞬態(tài)響應。由于這些原因及其它原因,設計團隊在構(gòu)建電路板之前,應充分了解設計以及提供給他們的各種選項。

在為其電源系統(tǒng)選擇電路時,設計團隊需要清楚的首要事項之一是:FPGA設計有嚴格的啟動順序要求。例如,Virtex-7 FPGA加電順序有下列兩種選擇:VCCINT_VMGTAVCC_VMGTAVTT 或VMGTAVCC_VCCINT_VMGTAVTT。

同時,電源關(guān)斷順序還應該與所選擇的加電順序正好相反。如果器件加電或關(guān)電順序與推薦的相左,在加電和電源關(guān)斷過程中,來自VMGTAVTT的平緩電流就會超出該規(guī)范。要滿足這種順序規(guī)則,設計人員可使用專用排序IC,也可使用POL的PGood及開關(guān)特性。

使用FPGA進行設計的電源系統(tǒng)還需要包含便于開發(fā)團隊監(jiān)控輸出電壓的電路。一般來說,設計人員不但可檢查產(chǎn)品精調(diào)階段的輸出電壓,而且還可通過調(diào)節(jié)輸出電壓來管理壓降。設計人員通常可使用POL調(diào)節(jié)電壓,但這當然也意味著設計中使用的POL需要具有輸出電壓調(diào)節(jié)特性。此外,電源系統(tǒng)還應提供監(jiān)控設計電壓電流的功能,以便檢查實時偏差和電源異常,更好地預測故障。

高速SERDES需要大電流,因為它們具有多個通道和一個高工作頻率。工程師用于為之供電的低壓差(LDO)穩(wěn)壓器會因低效率而產(chǎn)生大量熱量,因此對于需要大流耗的電路而言,它們并不是理想的電源解決方案。高速SERDES對電源電路中噪聲造成的抖動非常敏感。高抖動會降低信號質(zhì)量,導致數(shù)據(jù)錯誤。對于SERDES而言,擁有極好的信號完整性也非常重要,這可實現(xiàn)良好的高速數(shù)據(jù)通信。這當然也意味著設計人員在選擇POL時,應確保其POL無噪聲。

選擇高精度POL轉(zhuǎn)換器

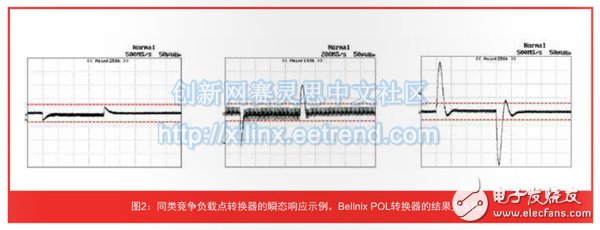

構(gòu)建最佳Virtex-7 FPGA電源系統(tǒng)的重要步驟是確保POL轉(zhuǎn)換器滿足給定器件要求。在大電流、電流變動劇烈的設計中,快速瞬態(tài)響應的POL轉(zhuǎn)換器非常適用。這些支持快速瞬態(tài)響應的高精度POL轉(zhuǎn)換器不僅有助于管理FPGA不斷變化的核心電壓,還有助于管理MGT的VMGTAVCC和VMGTAVTT。圖2是幾個POL轉(zhuǎn)換器動態(tài)負載變化電壓響應的測量結(jié)果。為公正起見,我們讓所有POL轉(zhuǎn)換器都工作在相同的條件下。唯一不同的是:我們使用了每一款POL轉(zhuǎn)換器制造商文獻資料推薦的電容器。

? 輸入電壓:5 V(固定值)

? 輸出電壓:1 V(固定值)(Virtex-7 核心電壓)

? 負載電流:0~10 A

? 電流變化斜率(單位時間電流變化率):5 A/μs

流媒體數(shù)據(jù)及數(shù)值處理可帶來FPGA的動態(tài)電流變化。我們的結(jié)果顯示,某些POL轉(zhuǎn)換器發(fā)生了輸出電壓過沖和下沖現(xiàn)象,超出了賽靈思針對Virtex-7 FPGA推薦的VCCINT和VMGTAVCC電壓,超出1 V(±30 mV)。當然,該數(shù)值可能會根據(jù)使用、電路板布局以及POL和FPGA周邊的去藕電容有所變化。但是很顯然,我們要到達Virtex-7 FPGA的推薦工作電壓范圍,就需要極好的電源充分滿足其大量電流快速變化(10A和5A/μs )的需求。Bellnix BSV系列能夠滿足這些要求,并支持快速瞬態(tài)響應,是高端FPGA以及分立式DSP與CPU等其它高速器件的必備產(chǎn)品。

輸出電壓及排序程序

如上文所述,隨著FPGA工藝技術(shù)的不斷縮小,其電源電壓也隨之降低,但功能數(shù)卻和其性能一樣,不斷提高。這會帶來電流的快速變化,提高電源要求。對設計工程師來說,要讓電壓保持在FPGA要求的允許容差范圍內(nèi),難度越來越大。這不僅對FPGA的核心電壓如此,對FPGA的高速SERDES也是如此。要讓Virtex-7收發(fā)器發(fā)揮最高性能優(yōu)勢,需要考慮幾個與電源有關(guān)的要點。例如,在因電源線電阻而產(chǎn)生壓降時,需要調(diào)整POL輸出電壓。與之類似,極限測試也需要輸出電壓調(diào)節(jié)功能。此外,設計人員還需要監(jiān)控和調(diào)整POL的輸出電壓,才能迅速評估系統(tǒng)。

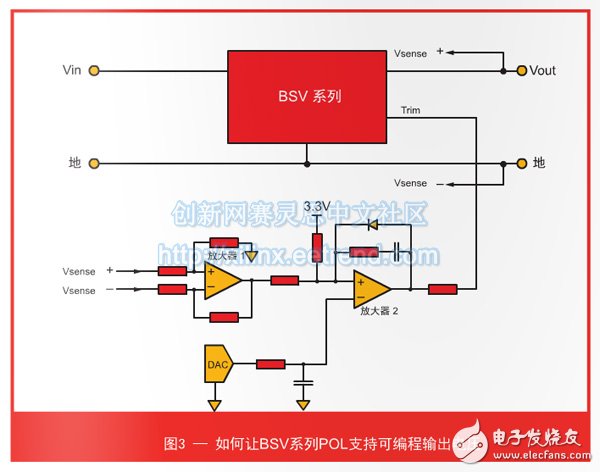

這里有一種可使用CPU程序調(diào)節(jié)輸出電壓的方法,其可充分滿足Virtex-7的電源要求。用戶可使用圖3所示的電路圖讓BSV系列POL支持可編程輸出電壓。

在本圖中,放大器1可檢測輸出電壓。用戶可通過差分放大器遠程傳感,實現(xiàn)對輸出電壓的精確控制,并可將POL轉(zhuǎn)換器連接至負載,抵消壓降。放大器2可使用放大器1檢測到的輸出電壓與D/A轉(zhuǎn)換器的輸出電壓進行比較。我們將放大器2的輸出連接到POL轉(zhuǎn)換器的調(diào)節(jié)引腳。POL轉(zhuǎn)換器的輸出電壓會隨調(diào)節(jié)引腳的輸入電壓變化而變化。這樣負載電壓和D/A轉(zhuǎn)換器的輸出就可匹配。

用戶可通過使用CPU控制D/A轉(zhuǎn)換器來設置輸出電壓。首先,在接通POL轉(zhuǎn)換器時,用戶必須先將D/A轉(zhuǎn)換器的輸出設置為0V,而后將開關(guān)控制設置為“開”,并將D/A轉(zhuǎn)換器的輸出設定為所需的值。如果正相輸入電壓為高,而放大器2的反相輸入電壓為0V(當輸出關(guān)閉時),放大器2就會試圖提升調(diào)節(jié)引腳上的輸出電壓,導致接通POL轉(zhuǎn)換器時的過壓。此外,用戶還必須在D/A轉(zhuǎn)換器的輸出端連接RC電路,以免放大器2的正相輸出引腳電壓快速上升,導致過沖。

在Bellnix,我們已經(jīng)為賽靈思7系列GTX/GTH FPGA開發(fā)出名為BPE-37的評估電源模塊。BPE-37不僅采用上述電路,而且還具有4個MGT所需的POL轉(zhuǎn)換器。這4個POL轉(zhuǎn)換器均為BSV系列POL,具有高精度、快速瞬態(tài)響應以及低紋波噪聲特性。BPE37使用微控制器控制D/A轉(zhuǎn)換器,將每個輸出電壓設置在適當?shù)乃缴稀4送猓撐⒖刂破鬟€使用其開關(guān)引腳,通過啟動和停止POL轉(zhuǎn)換器來實現(xiàn)對排序的控制。該技術(shù)有助于設計團隊通過PMBus串行通信修改輸出電壓,改變排序和監(jiān)控輸出電壓及電流。

BPE-37的電路配置可實現(xiàn)將數(shù)字功能添加至常規(guī)模擬類POL,充分滿足賽靈思Virtex-7系列的所有電源需求。這些FPGA中的GTX/GTH收發(fā)器要求POL支持最快的瞬態(tài)響應。表1所示為BPE-37的主要規(guī)范。

電子發(fā)燒友App

電子發(fā)燒友App

評論