在《數(shù)字電路之如雷貫耳的“邏輯電路”》、《數(shù)字電路之?dāng)?shù)字集成電路IC》之后,本文是數(shù)字電路入門3,將帶來「時序電路」的講解,及其核心部件觸發(fā)器的工作原理。什么是時序電路?

2016-08-01 10:58:48 18171

18171

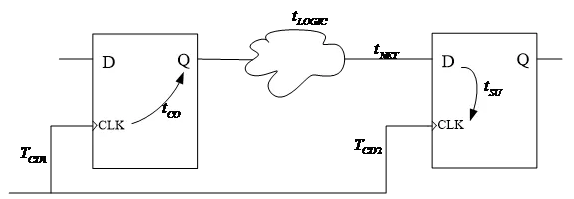

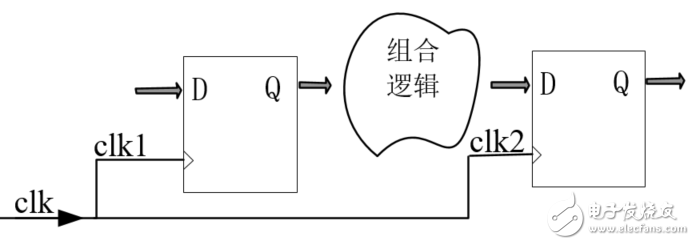

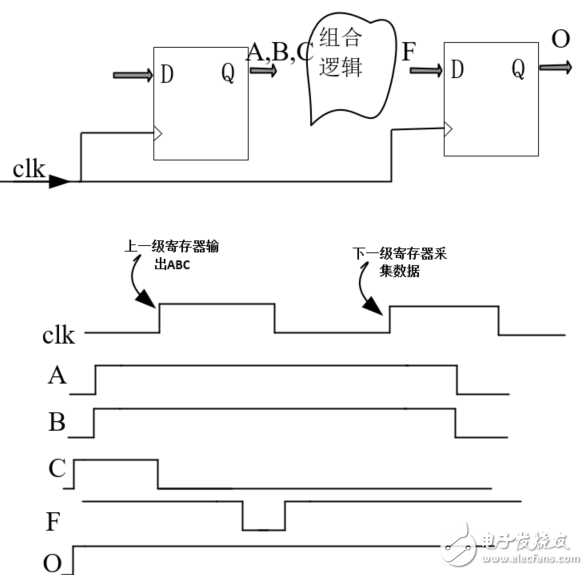

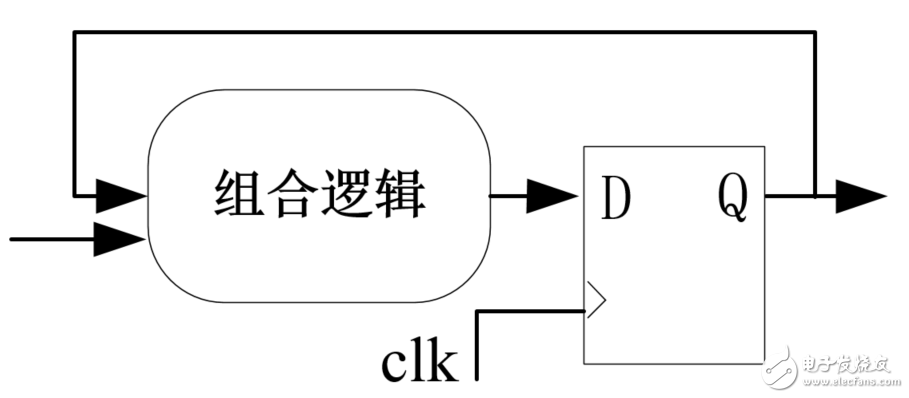

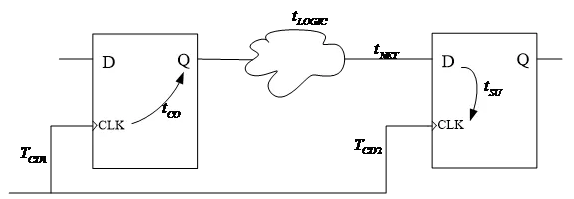

表。 這4類路徑中,我們最為關(guān)心是②的同步時序路徑,也就是FPGA內(nèi)部的時序邏輯。 時序模型 典型的時序模型如下圖所示,一個完整的時序路徑包括源時鐘路徑、數(shù)據(jù)路徑和目的時鐘路徑,也可以表示為觸發(fā)器+組合邏輯+觸發(fā)器的模型。 該

2020-11-17 16:41:52 2768

2768

時序電路 首先來看兩個問題: 1.為什么CPU要用時序電路,時序電路與普通邏輯電路有什么區(qū)別。 2.觸發(fā)器、鎖存器以及時鐘脈沖對時序電路的作用是什么,它們是如何工作的。 帶著這兩個問題,我們從頭了解

2020-11-20 14:27:09 3998

3998

對于絕大部分的電路來說輸出不僅取決于當(dāng)前的輸入值,也取決于原先的輸入值,也就是說電路具有記憶功能,這屬于同步時序電路。

2020-12-07 15:00:15 6297

6297

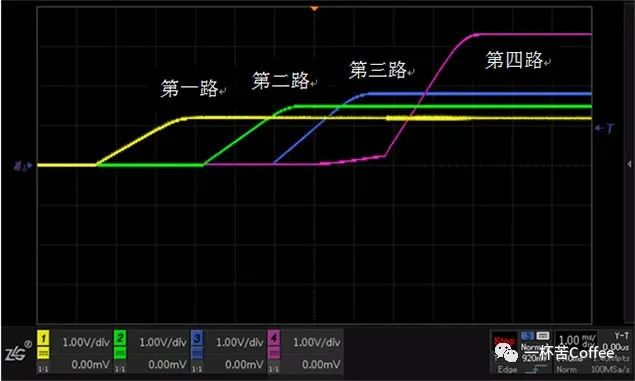

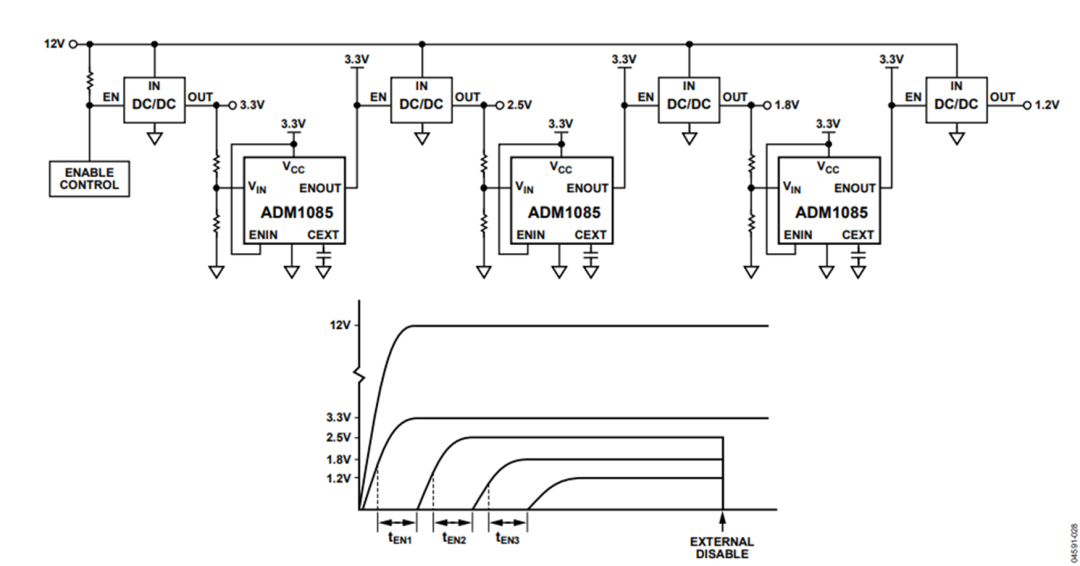

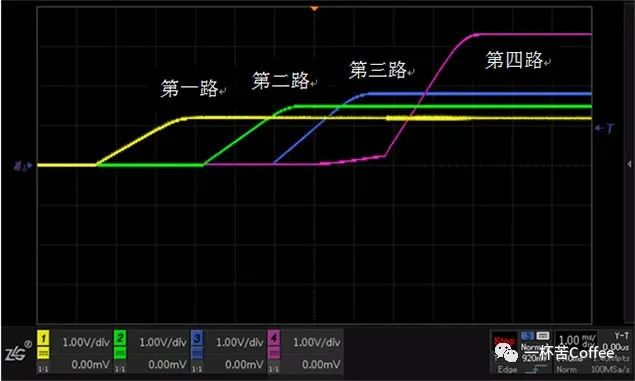

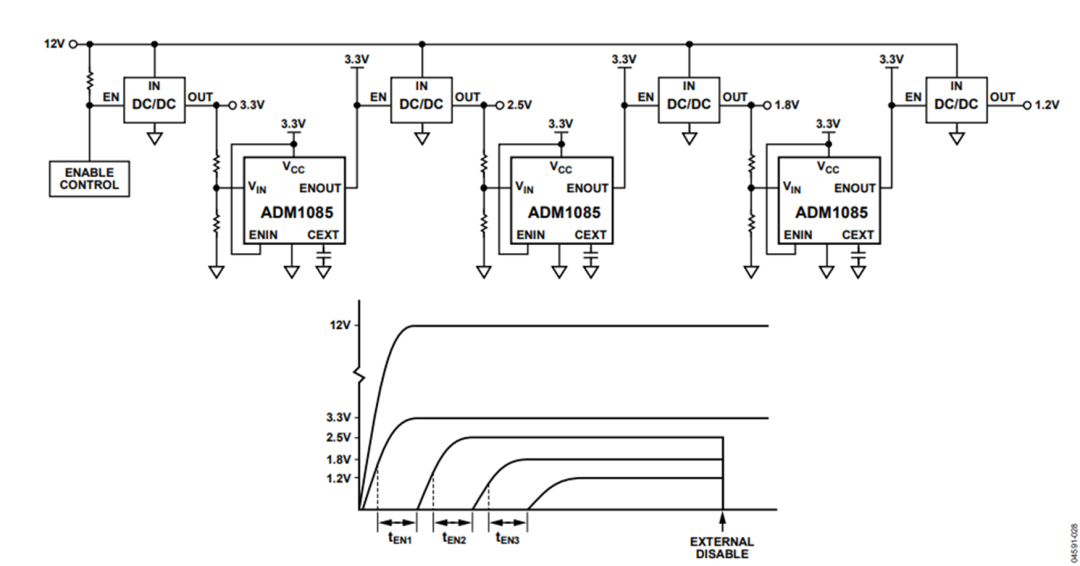

上電時序(Power-up Sequeence)是指各電源軌上電的先后關(guān)系。 與之對應(yīng)的是下電時序,但是在電路設(shè)計(jì)過程中,一般不會去考慮下電時序(特殊的場景除外)。今天,我們主要了解一下上電時序控制相關(guān)內(nèi)容。

2023-12-11 18:17:05 784

784

穩(wěn)定性。9、異步電路和同步時序電路的區(qū)別異步電路:電路核心邏輯有用組合電路實(shí)現(xiàn);異步時序電路的最大缺點(diǎn)是容易產(chǎn)生毛刺;不利于器件移植;不利于靜態(tài)時序分析(STA)、驗(yàn)證設(shè)計(jì)時序性能。同步時序電路:電路

2019-05-04 08:00:00

時間的重要性不言而喻,加上時間這個維度就如同X-Y的平面加上了一個Z軸,如同打開了一個新的世界。所以今天我們就要來聊聊時序電路。在時序電路中,電路任何時刻的穩(wěn)定狀態(tài)輸出不僅取決于當(dāng)前的輸入,還與前

2021-07-04 08:00:00

FPGA重要設(shè)計(jì)思想及工程應(yīng)用之時序及同步設(shè)計(jì)希望對大家有用

2016-04-24 22:31:46

什么是中斷?為什么CPU要用時序電路?時序電路與普通邏輯電路有什么區(qū)別呢?

2021-10-29 07:03:45

時序電路測試及應(yīng)用一、實(shí)驗(yàn)?zāi)康?.掌握常用時序電路分析,設(shè)計(jì)及測試方法。2.訓(xùn)練獨(dú)立進(jìn)行實(shí)驗(yàn)的技能.二、實(shí)驗(yàn)儀器及材料1.雙蹤示波器 2.

2009-08-20 18:55:27

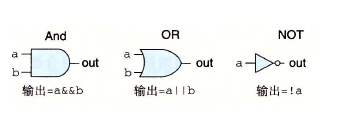

邏輯電路分為組合邏輯電路和時序邏輯電路。第四章已經(jīng)學(xué)習(xí)了組合邏輯電路的分析與設(shè)計(jì)的方法,這一章我們來學(xué)習(xí)時序電路的分析與設(shè)計(jì)的方法。在學(xué)習(xí)時序邏輯電路時應(yīng)注意的重點(diǎn)是常用時序部件的分析與設(shè)計(jì)這一

2018-08-23 10:28:59

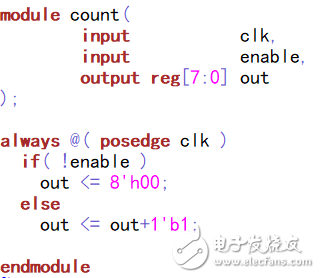

Verilog 設(shè)計(jì)初學(xué)者例程一 時序電路設(shè)計(jì) By 上海 無極可米 12/13/2001 ---------基礎(chǔ)-----------1. 1/2分頻器module halfclk(reset

2018-08-23 13:43:31

什么是時序電路?時序電路核心部件觸發(fā)器的工作原理

2021-03-04 06:32:49

什么是時序電路?SRAM是觸發(fā)器構(gòu)成的嗎?

2021-03-17 06:11:32

摘要:RS 232接口是現(xiàn)在最常用的一種通信接口。隨著FPGA技術(shù)的高速發(fā)展,一些常見的接口電路的時序電路可以通過FPGA實(shí)現(xiàn),通過這種設(shè)計(jì)可減少電路系統(tǒng)元件的數(shù)量,提高系統(tǒng)集成度和可靠性。詳細(xì)闡述

2019-06-19 07:42:37

實(shí)驗(yàn)二 基本時序電路設(shè)計(jì)(1)實(shí)驗(yàn)?zāi)康模菏煜uartusⅡ的VHDL文本設(shè)計(jì)過程,學(xué)習(xí)簡單時序電路的設(shè)計(jì)、仿真和硬件測試。(2)實(shí)驗(yàn)內(nèi)容:Ⅰ.用VHDL設(shè)計(jì)一個帶異步復(fù)位的D觸發(fā)器,并利用

2009-10-11 09:21:16

根據(jù)波形圖設(shè)計(jì)異步時序電路 急 求大神

2017-12-08 23:07:44

本文利用CPLD數(shù)字控制技術(shù)對時序電路進(jìn)行改進(jìn)。CPLD(Complex Programmable Logic Device)是新一代的數(shù)字邏輯器件,具有速度快、集成度高、可靠性強(qiáng)、用戶可重復(fù)編程或

2021-05-06 09:44:24

;nbsp; 4、理解時序電路和同步計(jì)數(shù)器加譯碼電路的聯(lián)系,設(shè)計(jì)任意編碼計(jì)數(shù)器。

2009-10-10 11:47:02

設(shè)計(jì)一個同步時序電路:只有在連續(xù)三個或者三個以上時針作用期間兩個輸入信號相同時,其輸出為1,其余情況下輸出為0。

2013-03-22 10:44:50

FPGA外部的芯片,可能是FPGA內(nèi)部的硬核。對于FPGA design來說,必須要關(guān)注在指定要求下,它能否正常工作。這個正常工作包括同步時序電路的工作頻率,以及輸入輸出設(shè)備的時序要求。在FPGA

2019-07-09 09:14:48

PLD練習(xí)2(時序電路)

2006-05-26 00:14:19 20

20 時序電路測試生成算法產(chǎn)生的向量存在冗余。針對此問題提出一種壓縮算法,減少測試序列的總長度,從而減少了仿真的時間和ATE 設(shè)備的測試的時間,加速了測試的流程。實(shí)驗(yàn)結(jié)果

2009-08-29 11:00:38 8

8 時序電路設(shè)計(jì)實(shí)例 (Sequential-Circuit Design Examples):We noted in previous chapters that we typically deal

2009-09-26 13:01:04 37

37 為解決TDI-CCD 作為遙感相機(jī)的圖像傳感器在使用中所面臨的時序電路設(shè)計(jì)問題,文中較為詳細(xì)地介紹了TDI-CCD 的結(jié)構(gòu)和工作原理,并根據(jù)工程項(xiàng)目所使用的ILE2TDI-CCD 的特性,設(shè)

2010-01-12 09:54:50 21

21 FPGA重要設(shè)計(jì)思想及工程應(yīng)用之時序及同

在FPGA設(shè)計(jì)中最好的時鐘方案 是: 由專用的全局時鐘輸入引腳 動單個 主時鐘去控制設(shè)計(jì)項(xiàng)目中的每一個觸發(fā) 器

2010-02-09 10:29:36 51

51 采用三相交流電源的低功耗絕熱時序電路

研究采用三相交流電源的絕熱時序電路。首先介紹了采用三相交流電源的雙傳輸門絕熱電路并分析其工作原理, 在此基

2010-02-22 15:41:56 15

15 摘要:通用教材<數(shù)字電子技術(shù)>中介紹的傳統(tǒng)的時序電路設(shè)計(jì)方法——狀態(tài)表及狀態(tài)圖法過于簡單,很難滿足較復(fù)雜電路的設(shè)計(jì)要求。介紹一種新的方法——MDS圖法,該方法具有

2010-04-28 08:38:27 20

20 摘要:分析了“數(shù)字電路與邏輯設(shè)計(jì)”課程中“一般時序電路設(shè)計(jì)”的內(nèi)容的地位與作用,指出傳統(tǒng)教學(xué)方法在設(shè)計(jì)較復(fù)雜電路時的局限性,為此完善了教材對該部分內(nèi)容的講解,

2010-05-08 08:42:54 0

0 摘要:針對同步時序電路的初始化問題,提出了一種新的實(shí)現(xiàn)方法。當(dāng)時序電路中有未確定狀態(tài)的觸發(fā)器時,就不能順利完成該電路的測試生成,因此初始化是時序電路測試生成中

2010-05-13 09:36:52 6

6 本文介紹將量子進(jìn)化算法應(yīng)用在時序電路測試生成的研究結(jié)果。結(jié)合時序電路的特點(diǎn),本文將量子計(jì)算中的量子位和疊加態(tài)的概念引入傳統(tǒng)的測試生成算法中,建立了時序電路的量

2010-08-03 15:29:01 0

0 本章內(nèi)容:q 鏡像電路q 準(zhǔn)nMOS電路q 三態(tài)電路q 鐘控CMOS電路q 動態(tài)CMOS電路q 雙軌邏輯電路q 時序電路

2010-08-13 14:44:30 0

0 在討論時序邏輯電路的分析與設(shè)計(jì)之前,讓我們先回顧一下在第四章中介紹過的時序電路結(jié)構(gòu)框圖和一些相關(guān)術(shù)語。時序電路的結(jié)構(gòu)框圖如圖5.1所示.。

2010-08-13 15:24:35 69

69 一、基本要求1、理解R-S觸發(fā)器、J-K觸發(fā)器和D觸發(fā)器的邏輯功能;2、掌握觸發(fā)器構(gòu)成的時序電路的分析,并了解其設(shè)計(jì)方法;3、理解計(jì)數(shù)器和寄存器的概念和功能,并掌握它

2010-08-26 11:40:22 57

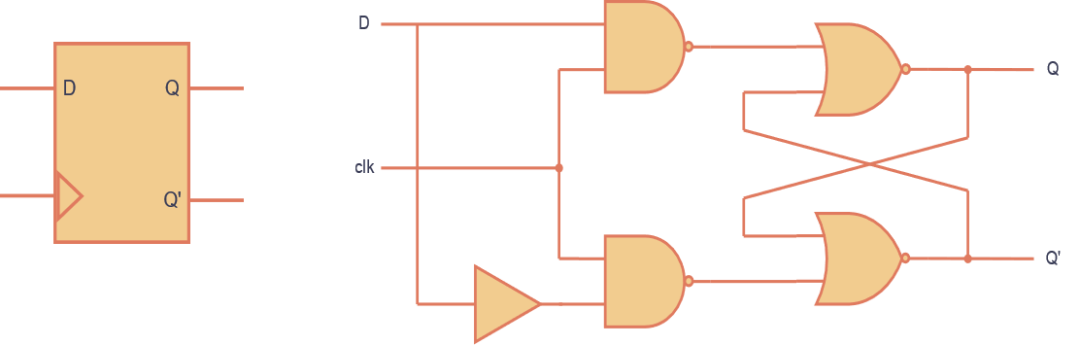

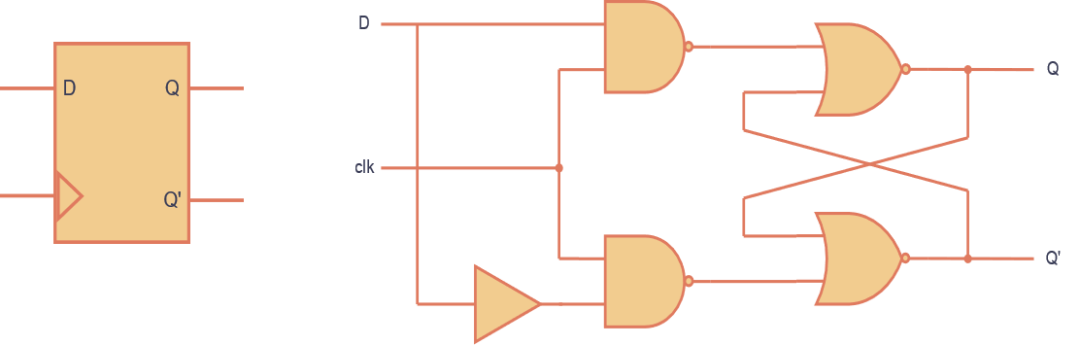

57 組合電路和時序電路是數(shù)字電路的兩大類。門電路是組合電路的基本單元;觸發(fā)器是時序電路的基本單元。

2010-08-29 11:29:04 67

67

時序電路設(shè)計(jì)串入/并出移位寄存器一 實(shí)驗(yàn)?zāi)康?掌握VHDL語言的基本描述語句的使用方法。2掌握使用VHDL語言進(jìn)行時序電路設(shè)計(jì)的方法。

2009-03-13 19:29:51 5733

5733

時序電路設(shè)計(jì)串入/并出移位寄存器一 實(shí)驗(yàn)?zāi)康?掌握VHDL語言的基本描述語句的使用方法。2掌握使用VHDL語言進(jìn)行時序電路設(shè)計(jì)的方法。

2009-03-13 19:29:52 2024

2024

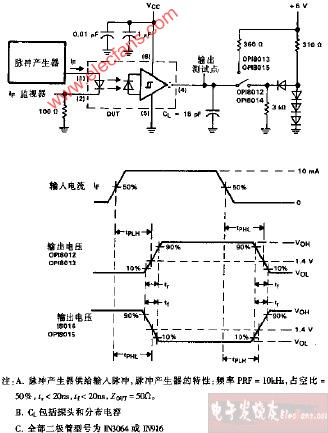

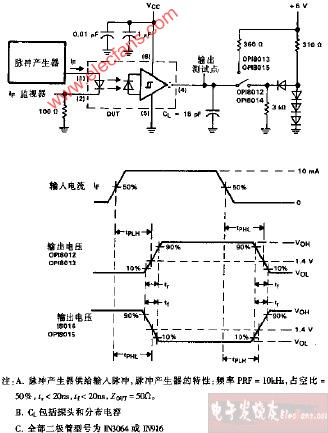

OPI812-OP1815開關(guān)時序電路及波形電路圖

2009-07-01 11:22:24 962

962

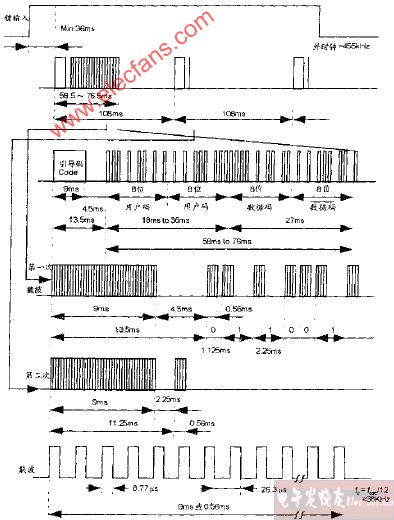

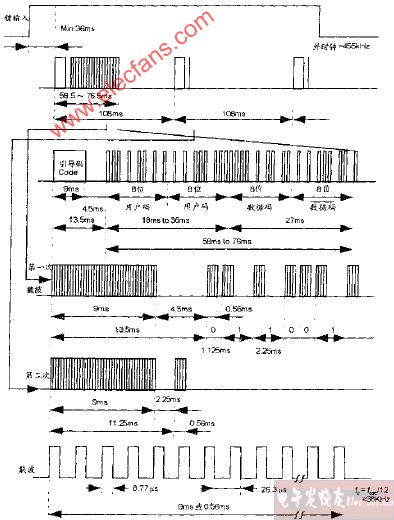

BLO508 A1輸出波形,單鍵操作時序電路圖

2009-07-02 10:54:11 542

542

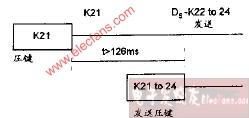

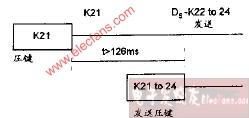

BLO508 A1型雙鍵操作時序電路圖

2009-07-02 10:56:00 526

526

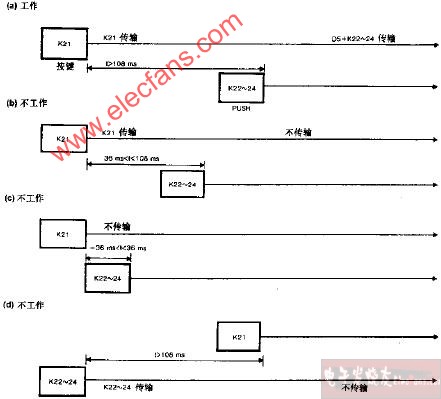

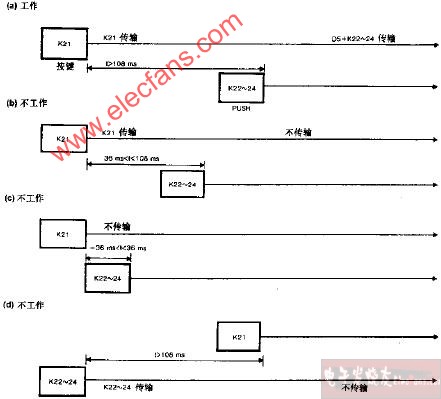

GM3043雙鍵工作時序電路圖

2009-07-02 11:07:30 424

424

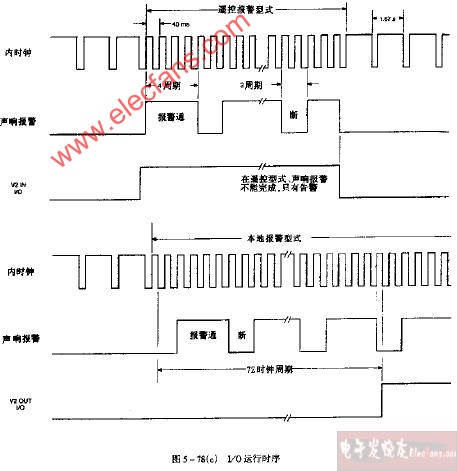

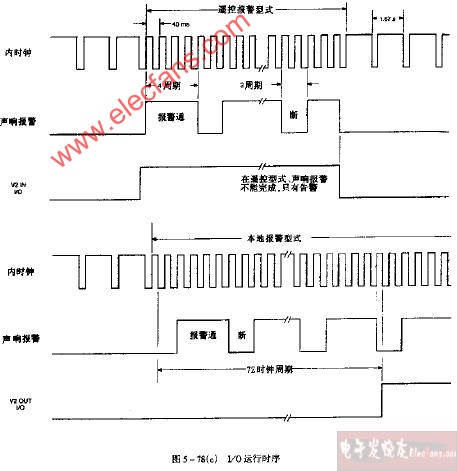

A5347 IO運(yùn)行時序電路圖

2009-07-03 12:03:29 440

440

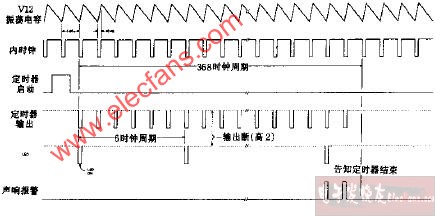

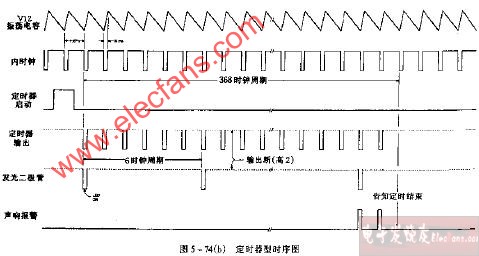

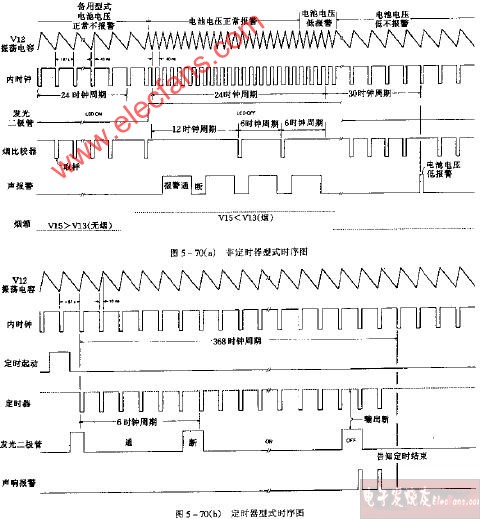

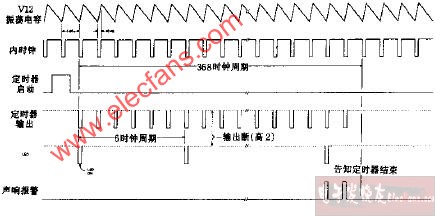

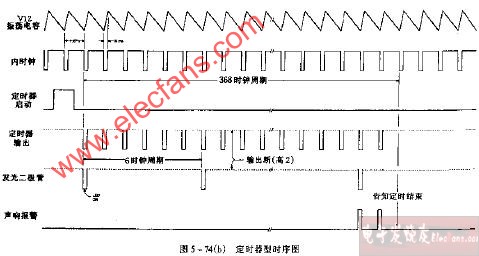

A5347定時器型時序電路圖

2009-07-03 12:09:08 546

546

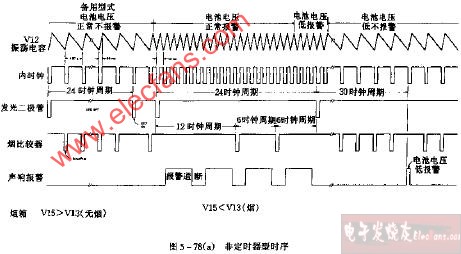

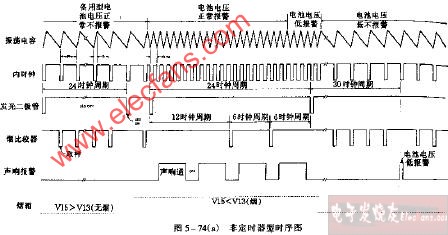

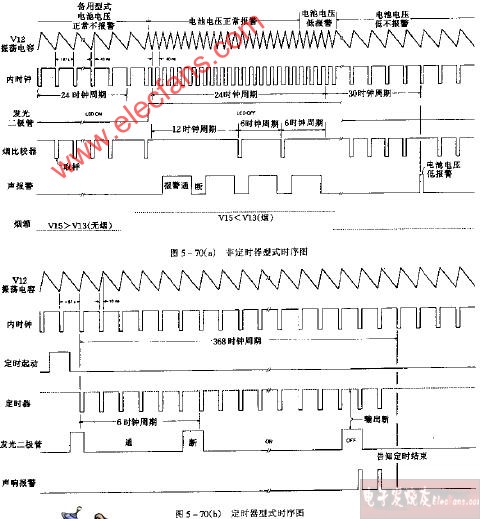

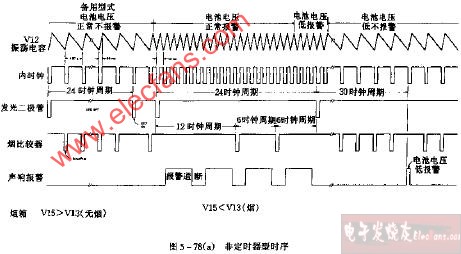

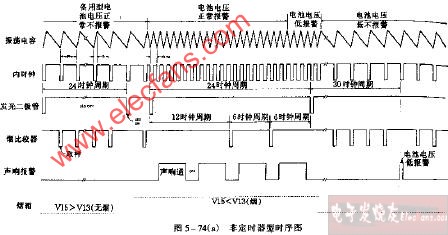

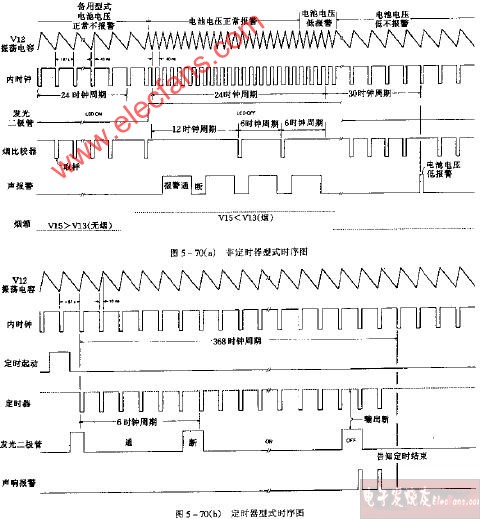

A5347非定時器型時序電路圖

2009-07-03 12:09:32 450

450

A5348 IO運(yùn)行時序電路圖

2009-07-03 12:11:10 393

393

0

A5348定時器型時序電路圖

2009-07-03 12:12:17 413

413

A5348非定時器型時序電路圖

2009-07-03 12:12:59 453

453

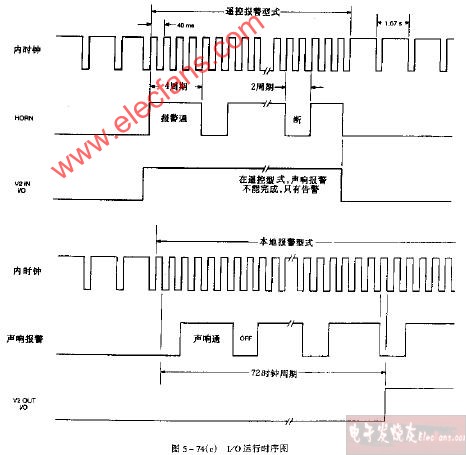

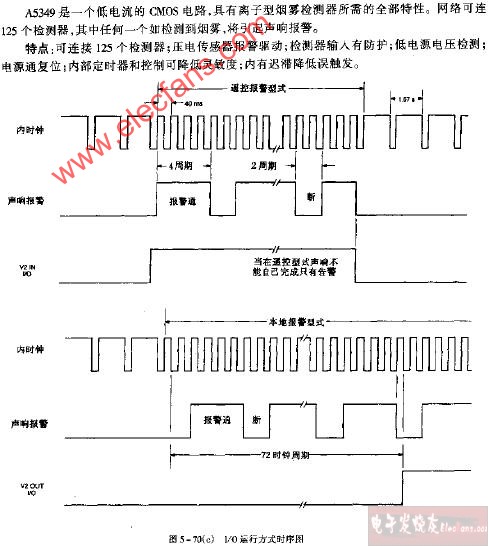

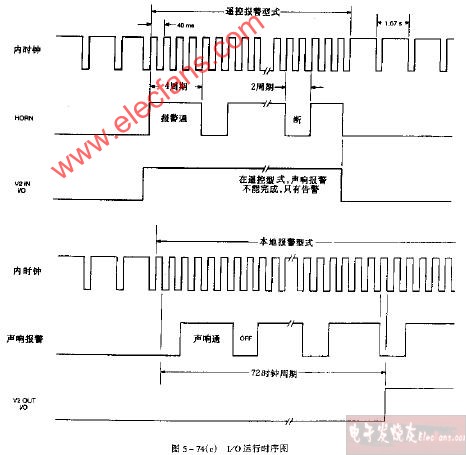

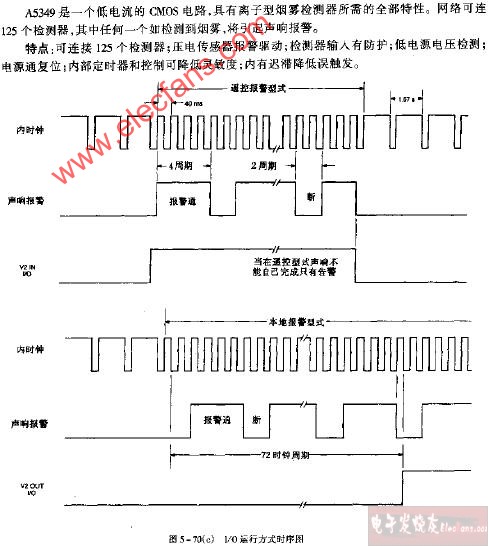

A5349 VO運(yùn)行方式時序電路圖

2009-07-03 12:14:37 603

603

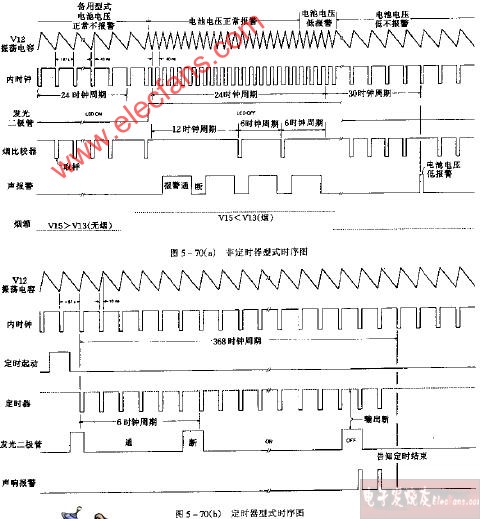

A5349定時器型式時序電路圖

2009-07-03 12:18:14 443

443

A5349非定時器型式時序電路圖

2009-07-03 12:18:51 461

461

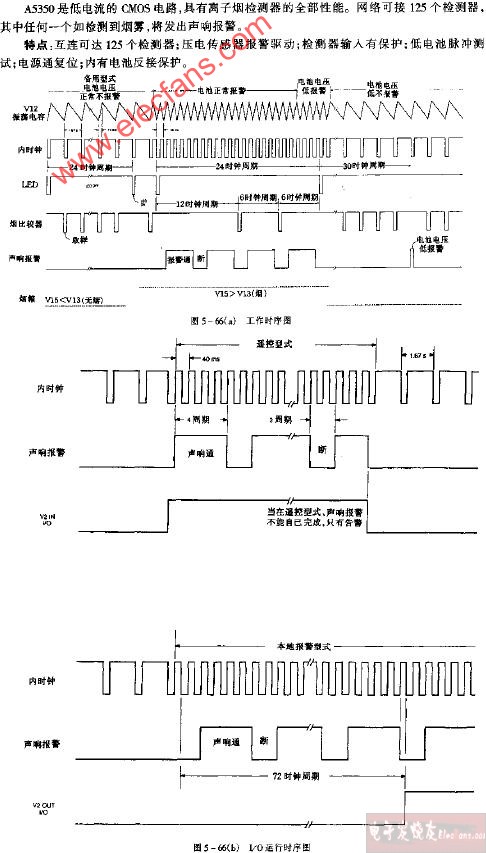

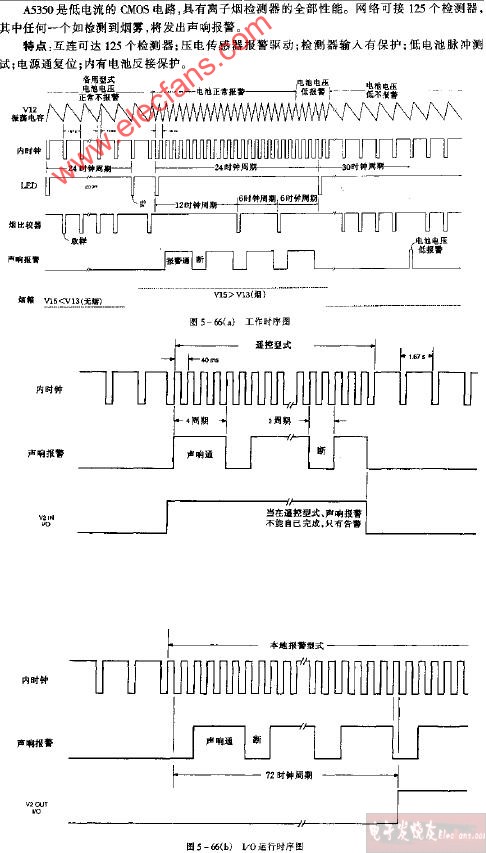

A5350 IO運(yùn)行時序電路圖

2009-07-03 12:20:26 484

484

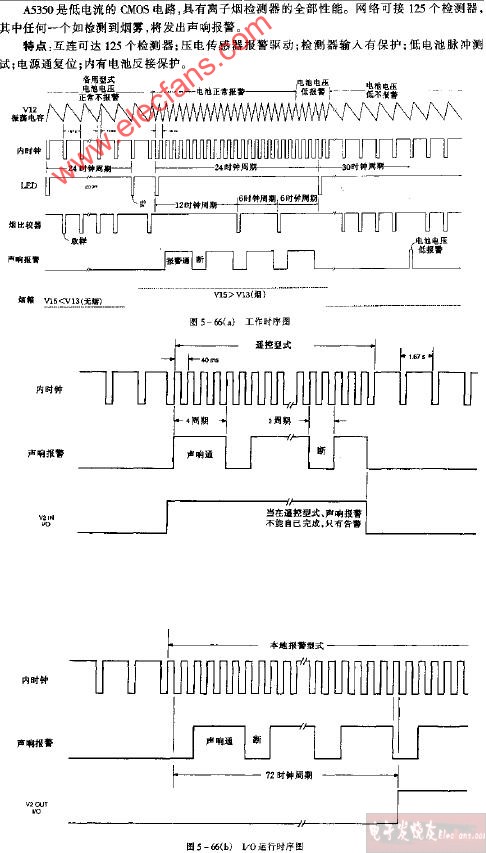

A5350工作時序電路圖

2009-07-03 12:22:16 652

652

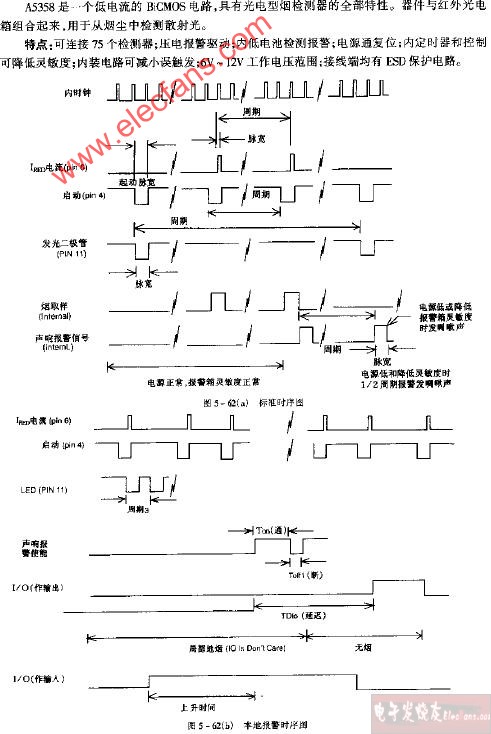

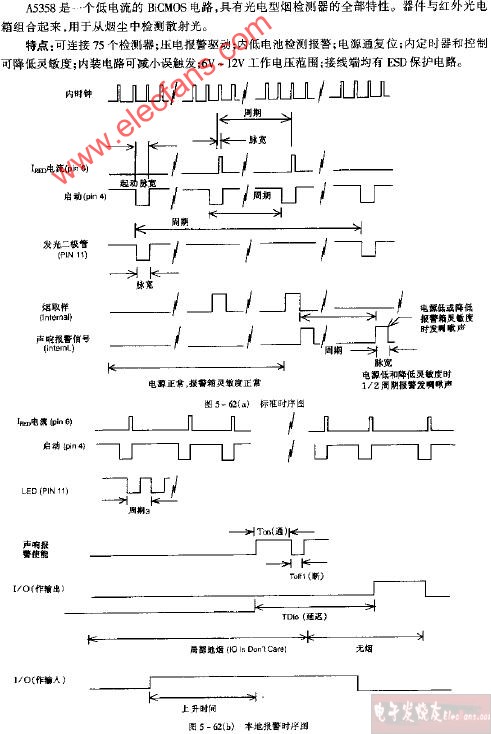

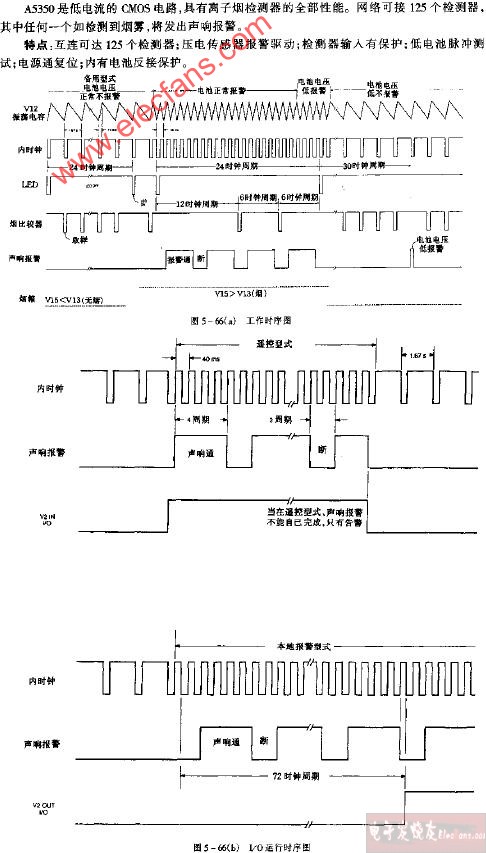

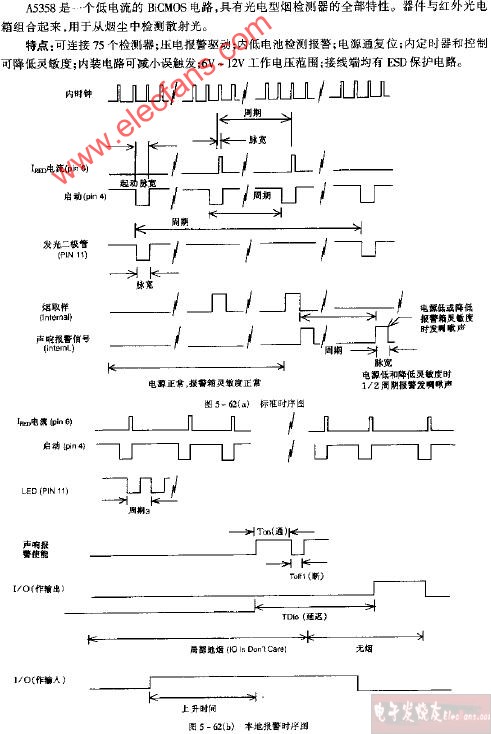

A5358本地報警時序電路圖

2009-07-03 12:23:28 944

944

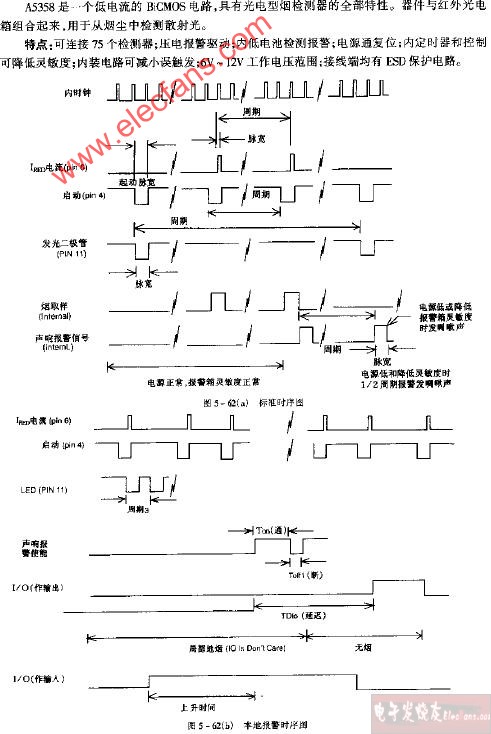

A5358標(biāo)準(zhǔn)時序電路圖

2009-07-03 12:30:49 806

806

同步時序電路

4.2.1 同步時序電路的結(jié)構(gòu)和代數(shù)法描述

2010-01-12 13:31:55 4672

4672

什么是時序電路

任意時刻的穩(wěn)定輸出,不僅與該時刻的輸入有關(guān),而且還

2010-01-12 13:23:14 8109

8109

為了實(shí)現(xiàn)時序電路狀態(tài)驗(yàn)證和故障檢測,需要事先設(shè)計(jì)一個輸入測試序列。基于二叉樹節(jié)點(diǎn)和樹枝的特性,建立時序電路狀態(tài)二叉樹,按照電路二叉樹節(jié)點(diǎn)(狀態(tài))與樹枝(輸入)的層次邏輯

2012-07-12 13:57:40 0

0 電子發(fā)燒友網(wǎng)核心提示 :RS 232接口是現(xiàn)在最常用的一種通信接口。隨著FPGA技術(shù)的高速發(fā)展,一些常見的接口電路的時序電路可以通過FPGA實(shí)現(xiàn),通過這種設(shè)計(jì)可減少電路系統(tǒng)元件的數(shù)量

2012-11-27 10:28:11 5937

5937 FPGA重要設(shè)計(jì)思想及工程應(yīng)用之時序及同步設(shè)計(jì)

2016-05-10 11:24:33 16

16 基于FPGA技術(shù)的RS232接口時序電路設(shè)計(jì)方案

2017-01-26 11:36:55 29

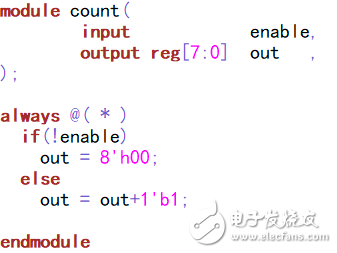

29 計(jì)數(shù)器的方法。

4、理解時序電路和同步計(jì)數(shù)器加譯碼電路的聯(lián)系,設(shè)計(jì)任意編碼計(jì)數(shù)器。

5、了解同步芯片和異步芯片的區(qū)別。

2022-07-10 14:37:37 15

15 在傳統(tǒng)設(shè)計(jì)中,所有計(jì)算機(jī)運(yùn)算(算法邏輯和存儲進(jìn)程) 都參考時鐘同步執(zhí)行,時鐘增加了設(shè)計(jì)中的時序電路數(shù)量。在這個電池供電設(shè)備大行其道的移動時代,為了節(jié)省每一毫瓦(mW) 的功耗,廠商間展開了殘酷的競爭

2017-10-25 15:41:59 25

25 在傳統(tǒng)設(shè)計(jì)中,所有計(jì)算機(jī)運(yùn)算(算法、邏輯和存儲進(jìn)程)都參考時鐘同步執(zhí)行,時鐘增加了設(shè)計(jì)中的時序電路數(shù)量。在這個電池供電設(shè)備大行其道的移動時代,為了節(jié)省每一毫瓦(mW)的功耗,廠商間展開了殘酷的競爭

2017-11-15 15:40:13 12

12 CCD驅(qū)動 電路的實(shí)現(xiàn)是CCD應(yīng)用技術(shù)的關(guān)鍵問題。以往大多是采用普通數(shù)字芯片實(shí)現(xiàn)驅(qū)動電路,CCD外圍電路復(fù)雜,為了克服以上方法的缺點(diǎn),利用VHDL硬件描述語言.運(yùn)用FPGA技術(shù)完成驅(qū)動時序電路的實(shí)現(xiàn)

2017-11-24 18:55:51 1523

1523

的數(shù)量,可以用消耗的觸發(fā)器和查找表的個數(shù)或者是等效邏輯門數(shù)來衡量;速度是指一個設(shè)計(jì)在FPGA上穩(wěn)定運(yùn)行時所能 達(dá)到的最高頻率,由設(shè)計(jì)時序狀態(tài)決定。 關(guān)于面積和速度的折衷,應(yīng)在滿足設(shè)計(jì)時序和工作頻率要求的前提下,占用最小的芯片面積;或者在所規(guī)定

2017-11-25 03:57:01 802

802

“時鐘是時序電路的控制者” 這句話太經(jīng)典了,可以說是FPGA設(shè)計(jì)的圣言。FPGA的設(shè)計(jì)主要是以時序電路為主,因?yàn)榻M合邏輯電路再怎么復(fù)雜也變不出太多花樣,理解起來也不沒太多困難。但是時序電路就不

2018-07-21 10:55:37 4504

4504 組合電路和時序電路是計(jì)算機(jī)原理的基礎(chǔ)課,組合電路描述的是單一的函數(shù)功能,函數(shù)輸出只與當(dāng)前的函數(shù)輸入相關(guān);時序電路則引入了時間維度,時序電路在通電的情況下,能夠保持狀態(tài),電路的輸出不僅與當(dāng)前的輸入有關(guān),而且與前一時刻的電路狀態(tài)相關(guān),如我們個人PC中的內(nèi)存和CPU中的寄存器,均為時序電路。

2018-09-25 09:50:00 24779

24779 關(guān)鍵詞:時序電路 , 同步 同步時序電路設(shè)計(jì) 1.建立原始狀態(tài)圖. 建立原始狀態(tài)圖的方法是: 確定輸入、輸出和系統(tǒng)的狀態(tài)函數(shù)(用字母表示). 根據(jù)設(shè)計(jì)要求,確定每一狀態(tài)在規(guī)定條件下的狀態(tài)遷移方向

2018-10-31 18:14:01 1097

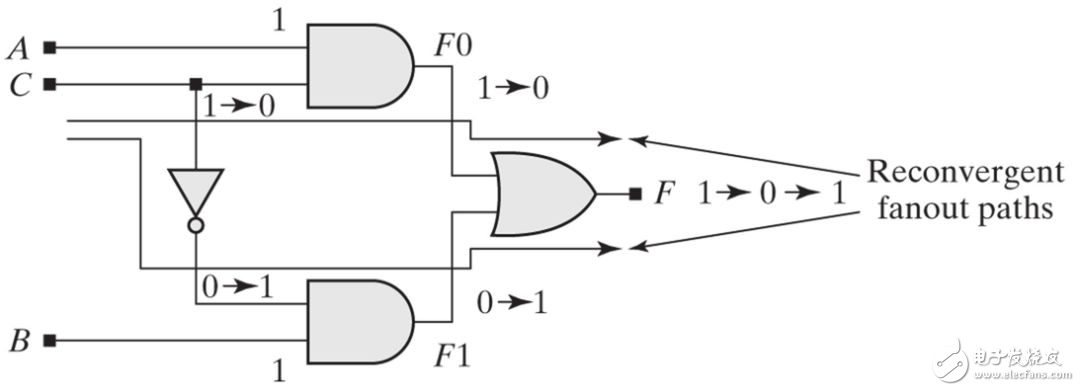

1097 本文檔的主要內(nèi)容詳細(xì)介紹的是數(shù)字電路教程之時序邏輯電路課件的詳細(xì)資料免費(fèi)下載主要內(nèi)容包括了:一 概述,二 時序邏輯電路的分析方法,三 若干常用的時序邏輯電路,四 時序邏輯電路的設(shè)計(jì)方法,五 時序邏輯電路中的競爭冒險現(xiàn)象

2018-12-28 08:00:00 12

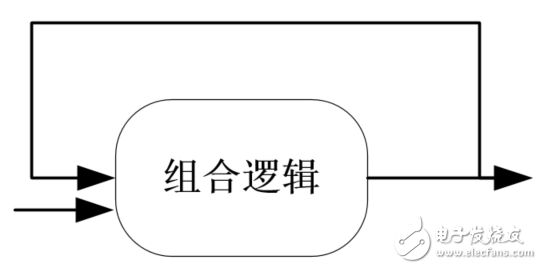

12 時序電路,是由最基本的邏輯門電路加上反饋邏輯回路(輸出到輸入)或器件組合而成的電路,與組合電路最本質(zhì)的區(qū)別在于時序電路具有記憶功能。

2019-09-27 07:10:00 2169

2169

時序電路,是由最基本的邏輯門電路加上反饋邏輯回路(輸出到輸入)或器件組合而成的電路,與組合電路最本質(zhì)的區(qū)別在于時序電路具有記憶功能。

2019-12-13 07:07:00 1743

1743

時序電路,是由最基本的邏輯門電路加上反饋邏輯回路(輸出到輸入)或器件組合而成的電路,與組合電路最本質(zhì)的區(qū)別在于時序電路具有記憶功能。

2019-09-23 07:08:00 2068

2068

本文檔的主要內(nèi)容詳細(xì)介紹的是數(shù)碼管與分析儀的時序電路原理圖免費(fèi)下載。

2019-12-13 15:17:11 8

8 本文檔的主要內(nèi)容詳細(xì)介紹的是模擬電路教程之時序邏輯電路的課件資料免費(fèi)下載包括了:1 概述,2 時序邏輯電路的分析方法,3 若干常用的時序邏輯電路,4 時序邏輯電路的設(shè)計(jì)方法。

2020-06-22 08:00:00 13

13 時序電路是數(shù)字電路的基本電路,也是FPGA設(shè)計(jì)中不可缺少的設(shè)計(jì)模塊之一。

2020-09-08 14:21:22 6067

6067

時間的重要性不言而喻,加上時間這個維度就如同X-Y的平面加上了一個Z軸,如同打開了一個新的世界。所以今天我們就要來聊聊時序電路。 在時序電路中,電路任何時刻的穩(wěn)定狀態(tài)輸出不僅取決于當(dāng)前的輸入,還與

2021-01-06 17:07:22 4371

4371 本文章探討一下FPGA的時序約束步驟,本文章內(nèi)容,來源于配置的明德?lián)P時序約束專題課視頻。

2022-03-16 09:17:19 3255

3255

上一篇《FPGA時序約束分享01_約束四大步驟》一文中,介紹了時序約束的四大步驟。

2022-03-18 10:29:28 1323

1323

“時鐘是時序電路的控制者”這句話太經(jīng)典了,可以說是FPGA設(shè)計(jì)的圣言。FPGA的設(shè)計(jì)主要是以時序電路為主,因?yàn)榻M合邏輯電路再怎么復(fù)雜也變不出太多花樣,理解起來也不沒太多困難。

2022-04-14 10:56:29 1609

1609 組合邏輯和時序邏輯電路是數(shù)字系統(tǒng)設(shè)計(jì)的奠基石,其中組合電路包括多路復(fù)用器、解復(fù)用器、編碼器、解碼器等,而時序電路包括鎖存器、觸發(fā)器、計(jì)數(shù)器、寄存器等。 在本文中,小編簡單介紹關(guān)于時序電路的類型和特點(diǎn)等相關(guān)內(nèi)容。

2022-09-12 16:44:00 7234

7234

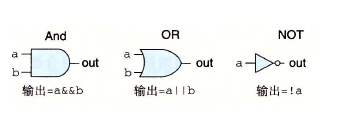

從今天開始新的一章-Circuits,包括基本邏輯電路、時序電路、組合電路等。

2022-10-10 15:39:01 875

875 “時鐘是時序電路的控制者”這句話太經(jīng)典了,可以說是FPGA設(shè)計(jì)的圣言。FPGA的設(shè)計(jì)主要是以時序電路為主,因?yàn)榻M合邏輯電路再怎么復(fù)雜也變不出太多花樣,理解起來也不沒太多困難。

2022-12-02 09:53:11 473

473 那么,如何才能將過去的輸入狀態(tài)反映到現(xiàn)在的輸出上呢?「時序電路」到底需要些什么呢?人類總是根據(jù)過去的經(jīng)驗(yàn),決定現(xiàn)在的行動,這時我們需要的就是—記憶。同樣,「時序電路」也需要這樣的功能。這種能夠?qū)崿F(xiàn)人類記憶功能的元器件就是觸發(fā)器。

2023-03-24 10:48:58 818

818

同步和異步時序電路都是使用反饋來產(chǎn)生下一代輸出的時序電路。根據(jù)這種反饋的類型,可以區(qū)分這兩種電路。時序電路的輸出取決于當(dāng)前和過去的輸入。時序電路分為同步時序電路和異步時序電路是根據(jù)它們的觸發(fā)器來完成的。

2023-03-25 17:29:52 17514

17514

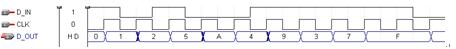

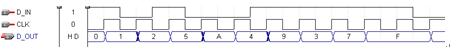

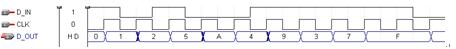

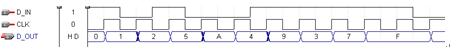

對于DFF,之前理解的,DFF在時鐘的上升沿進(jìn)行對D端的數(shù)據(jù)采集,再下一個時鐘的上升沿來臨,Q端輸出D端采集的數(shù)據(jù)。

2023-05-10 09:02:32 1800

1800

時間的重要性不言而喻,加上時間這個維度就如同X-Y的平面加上了一個Z軸,如同打開了一個新的世界。所以今天我們就要來聊聊時序電路。

2023-06-20 16:59:50 252

252

一種基于電流源基準(zhǔn)型LDO的放大器供電時序電路的應(yīng)用

2023-11-23 09:04:52 272

272

時序電路是由觸發(fā)器等時序元件組成的數(shù)字電路,用于處理時序信號,實(shí)現(xiàn)時序邏輯功能。根據(jù)時序元件的類型和組合方式的不同,時序電路可以分為同步時序電路和異步時序電路。本文將從這兩個方面詳細(xì)介紹時序電路

2024-02-06 11:22:30 291

291 時序電路是一種能夠按照特定的順序進(jìn)行操作的電路。它以時鐘信號為基準(zhǔn),根據(jù)輸入信號的狀態(tài)和過去的狀態(tài)來確定輸出信號的狀態(tài)。時序電路廣泛應(yīng)用于計(jì)算機(jī)、通信系統(tǒng)、數(shù)字信號處理等領(lǐng)域。根據(jù)不同的分類標(biāo)準(zhǔn)

2024-02-06 11:25:21 399

399 時序電路基本原理是指電路中的輸出信號與輸入信號的時間相關(guān)性。簡單來說,就是電路的輸出信號要依賴于其輸入信號的順序和時間間隔。 時序電路由時鐘信號、觸發(fā)器和組合邏輯電路組成。時鐘信號是時序電路的重要

2024-02-06 11:30:00 344

344

電子發(fā)燒友App

電子發(fā)燒友App

評論