DSP這幾年有點背,逐漸遠離主流 話題 ,所以有人就有了這樣的問題:DSP會被FPGA取代嗎? 網友一:獨立的DSP不會被FPGA替代,但是會被增強了信號處理功能的 ARM 處理器替代。現在基本已

2022-11-29 10:25:02 4007

4007

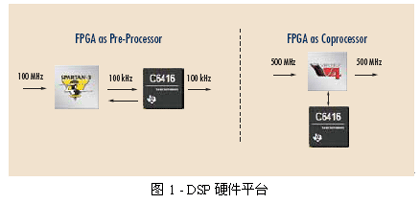

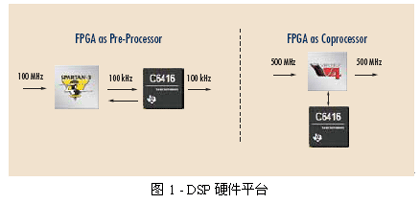

傳統的、基于通用DSP處理器并運行由C語言開發的算法的高性能DSP平臺,正在朝著使用FPGA預處理器和/或協處理器的方向發展。這一最新發展能夠為產品提供巨大的性能、功耗和成本優勢。 盡管優勢如此明顯

2023-10-21 16:55:02 1498

1498

近幾年,搭乘新興市場(智能工業、物聯網等)和先進半導體技術快速發展先機,FPGA憑借其性能優勢不斷入侵并蠶食著DSP市場,以Altera和Xilinx主導的PLD廠商在各領域攻城拔寨勢如破竹,喜訊

2013-12-27 14:47:49 9229

9229 的方法彌補單DSP核心的缺陷。DSP+FPGA的結構能將DSP從繁瑣的外部接口管理中解放出來,充分發揮DSP的運算優勢,提高運算效率的同時易于維護和擴展。DSP通過XINTF接口與FPGA通信。DSP

2016-09-24 10:41:18

大家好,我現在在畫一塊28335的板子,想實現與FPGA之間的通信,但是不知道該怎樣設計,包括FPGA與DSP連接的引腳、通過內部什么模塊實現數據通信,現在一頭霧水,請大家幫忙。謝謝。

2018-12-03 15:55:34

隨著模擬IC市場中眾多垂直細分行業的飛速發展,傳統DSP器件遭遇了各種替代性信號處理平臺的競爭,FPGA即為典型代表。憑借高密度、低功耗和低成本的優勢,FPGA不僅在通信、消費類、嵌入式等廣泛

2019-06-27 07:06:16

DSP和FPGA之間串口通信研究

2015-03-16 15:44:52

FPGA CPLD同步設計若干問題淺析摘要:針對FPGA/CPLD同步設計過程中一些容易被忽視的問題進行了研究,分析了問題產生的原因、對可靠性的影響,并給出了解決方案。關鍵詞:FPGA/CPLD

2009-04-21 16:42:01

對售后產品設計進行修改的ASIC和ASSP來說,這是FPGA特有的一個優勢。由于FPGA可編程的靈活性以及近年來電子技術領域的快速發展,FPGA也正在向高集成、高性能、低功耗、低價格的方向發展,并且

2021-11-02 06:30:00

TigerSHARC系列DSP芯片與外部進行數據通信主要有兩種方式:總線方式和鏈路口方式。鏈路口方式更適合于FPGA與DSP之間的實時通信。隨著實時信號處理運算量的日益增加,多DSP并行處理的方式被

2019-06-21 05:00:07

FPGA是一種可編程的硅芯片,DSP是數字信號處理,當系統設計人員在項目的架構設計階段就面臨到底采用FPGA還是DSP的重要問題。本文將首先分別介紹FPGA和DSP的特點,然后再從內部資源、編程語言

2019-05-07 01:28:40

在雷達信號處理、數字圖像處理等領域中,信號處理的實時性至關重要。由于FPGA芯片在大數據量的底層算法處理上的優勢及DSP芯片在復雜算法處理上的優勢,DSP+FPGA的實時信號處理系統的應用越來越廣泛

2018-12-04 10:39:29

在雷達信號處理、數字圖像處理等領域中,信號處理的實時性至關重要。由于FPGA芯片在大數據量的底層算法處理上的優勢及DSP芯片在復雜算法處理上的優勢,DSP+FPGA的實時信號處理系統的應用越來越廣泛

2019-06-19 05:00:08

CCS5.5DSP 6657FPGA XC7Z030FPGA 與 FPGA 之間SRIO傳輸成功;DSP 與 DSP 之間SRIO傳輸成功;問題 : FPGA 與 DSP 之間 ,PORT OK 可以通過,可是就是無法正確傳輸成功。 這會是什么問題呢?會是什么原因導致的呢?需要注意什么地方呢?

2019-01-10 11:17:28

`電子發燒友網12月《處理器與DSP特刊》火熱下載 {:4_129:}近幾年,搭乘新興市場(智能工業、物聯網等)和先進半導體技術快速發展先機,FPGA憑借其性能優勢不斷入侵并蠶食著DSP市場,以

2014-01-09 17:52:31

具有比較強的事務管理功能,可以用來跑界面以及應用程序等,其優勢主要體現在控制方面,而DSP主要是用來計算的,比如進行加密解 密、調制解調等,優勢是強大的數據處理能力和較高的運行速度。FPGA可以用

2014-06-26 14:23:43

見的短期培訓業務中也分別有針對ARM、DSP、FPGA的培訓課程。 區別是什么?:ARM具有比較強的事務管理功能,可以用來跑界面以及應用程序等,其優勢主要體現在控制方面,而DSP主要是用來計算的,比如

2013-05-06 15:56:02

傳統的、基于通用DSP處理器并運行由C語言開發的算法的高性能DSP平臺,正在朝著使用FPGA預處理器和/或協處理器的方向發展。這一最新發展能夠為產品提供巨大的性能、功耗和成本優勢。

2011-09-29 16:28:38

摘要:在雷達信號處理、數字圖像處理等領域中,信號處理的實時性至關重要。由于FPGA芯片在大數據量的底層算法處理上的優勢及DSP芯片在復雜算法處理上的優勢,DSP+FPGA的實時信號處理系統

2019-06-21 05:00:04

,SDRAM 由于其性能價格比的優勢,而被 DSP 開發者所青睞。DSP 與 SDRAM 直接接口是不可能的。FPGA(現場可編程門陣列)由于其具有使用靈活、執行速度快、開發工具豐富的特點而越來越多地出現在

2020-04-23 08:00:00

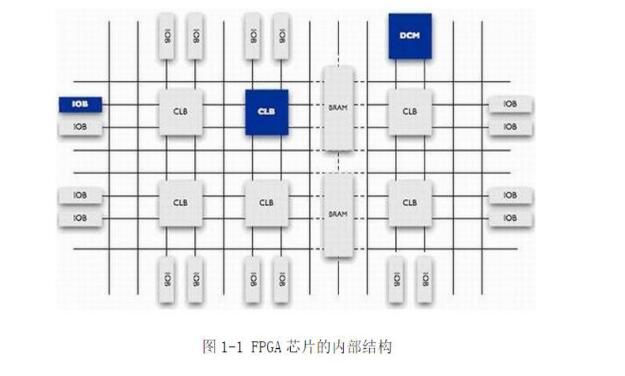

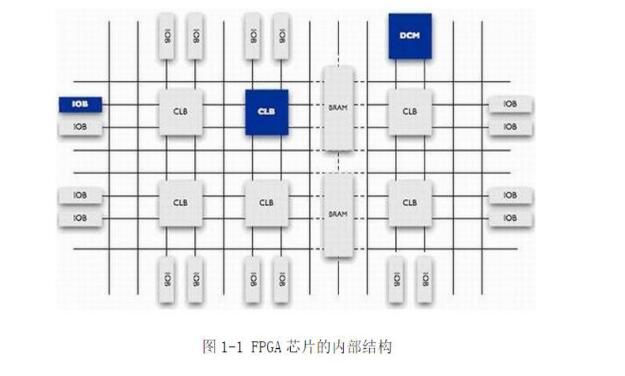

FPGA的基本特點是什么?FPGA有什么優勢?FPGA的應用方向是什么?

2021-10-08 06:43:45

FPGA的方案選擇 幸運的是,需要高性能DSP功能的便攜式設備設計者還有其它選擇。最近FPGA開始達到了應用所要求的成本競爭力。優選的FPGA方案可用來處理計算量繁重的高端DSP算法,同時還可

2011-02-17 11:21:37

端口的數量。同樣,DSP算法轉移至FPGA可顯著提升數據吞吐量和控制功能的執行 速度。然而,可能會有一些靈活性方面的損失。不過,通常DSP開發人員可以利用FPGA的優勢,因為這些功能可以用VHDL或

2012-08-11 11:27:45

需要把在DSP中采集到的數據發送到FPGA中進行處理,這部分語句(接受從DSP發送來的數據)怎么用verilog語言編寫??是編寫個RAM模塊嗎??

2017-10-10 21:43:41

進行高速數據傳輸有幾種方案我知道可以用雙口RAM 或者協議的方式 但是不知道還有沒有其他的方式要求之間的通信速度要快 相互之間進行數據的交換其實就是FPGA把數據交給DSP進行處理 處理完了之后再有FPGA進行實時的圖像顯示而已

2012-08-06 10:56:57

ARM、DSP及FPGA的技術特點和區別

2019-10-12 07:13:50

ARM/DSP/FPGA之間有什么聯系?區別是什么?

2021-10-25 07:54:17

實時處理,就是同一時間內能完成多個任務,而且不會互相影響。DSP主要是用來計算的,比如進行加密解密、調制解調等,優勢是強大的數據處理能力和較高的運行速度;FPGA可以用VHDL或verilog HDL來編程

2021-09-08 17:49:20

設計集成、可重新編程能力等優勢,有效協助系統開發商的產品更快速地推向市場,逐漸進入傳統MCU和DSP占主要份額的領域。初露頭角的FPGA已能窺見其背后廣闊的市場前景,隨著系統復雜度的提高,FPGA還能

2014-07-24 11:18:05

MCU、DSP與FPGA三者之間有何關系?MCU、DSP與FPGA的優缺點有哪些?

2021-09-24 06:53:19

請問:C6000系列的DSP在矩陣求逆計算時,計算速度和功耗方面,與Xilinx Virtex5的FPGA相比,是否會有優勢?

2018-12-25 11:20:12

UltraScale DSP48 Slice架構的優勢是什么?UltraScale內存架構的優勢是什么?

2021-05-24 06:34:00

本文主要介紹說明XQ6657Z35-EVM 高速數據處理評估板ZYNQ(FPGA)與DSP之間GPIO通信的功能、使用步驟以及各個例程的運行效果。1.1 ZYNQ與DSP之間GPIO通信1.1.1

2023-06-16 16:02:47

1 ZYNQ與DSP之間通信例程1.1 ZYNQ與DSP之間SRIO通信1.1.1 例程位置ZYNQ例程保存在資料盤中的Demo\ZYNQ\PL\srio_gen2_0_ex文件夾下。DSP例程保存

2023-02-02 21:43:20

受到影響。2. FPGA技術的五大優勢性能-利用硬件并行的優勢,FPGA打破了順序執行的模式,在每個時鐘周期內完成更多的處理任務,超越了數字信號處理器(DSP)的運算能力。 著名的分析與基準測試公司BDTI

2019-04-28 10:04:13

目前已調試完成兩片DSP之間的SRIO通信,在進行DSP與FPGA之間的SRIO。現在遇到了如下幾個問題。希望TI的工程師們有時間的時候給點幫助,不勝感激。1.DSP之間傳輸時一切正常,但是

2018-12-27 11:16:03

`FPGA是一種可編程的硅芯片,DSP是數字信號處理,當系統設計人員在項目的架構設計階段就面臨到底采用FPGA還是DSP的重要問題。本文將首先分別介紹FPGA和DSP的特點,然后再從內部資源、編程

2016-12-23 16:56:04

本文闡述了Spartan-3 FPGA針對DSP而優化的特性,并通過實現示例分析了它們在性能和成本上的優勢。

2019-10-18 07:11:35

在芯片設計中FPGA的優勢是什么?基于FPGA的芯片設計方法及流程是怎樣的?

2021-05-10 07:06:05

大家說在控制領域DSP和FPGA那個有優勢

2013-07-28 17:33:35

、成本上的優勢是巨大的。 除了上述兩種方案,還有DSP+FPGA方案,以及選擇內部嵌入DSP模塊的FPGA實現系統的方案。

2019-06-19 08:02:03

的DSP涉及最多的是一些基本的BIOS操作系統之間的任務調度,以及算法改進與優化等待, DSP的關鍵優勢包括其對于新型及復雜算法時的更短的開發時間,以及能夠運行多種算法的靈活性。 而對于FPGA來說,你

2018-10-10 18:02:03

是可編程邏輯器件,側重時序,可構建從小型到大型的幾乎所有數字電路系統,DSP主要完成復雜的數字信號處理,如fft,通常一個復雜系統可以由單片機、arm、FPGA、dsp中的一種或幾種構成,各有優勢和不足。...

2021-12-15 09:06:11

請教各位大神!是否可以通過FPGA內核配置的雙口RAM,實現FPGA與DSP之間的數據交換?可以的話怎么實現?怎么設置FPGA的內核RAM?如何連接DSP的外部存儲器XINTF的引腳和FPGA的引腳?謝謝!

2017-12-07 15:44:03

DSP48A的SPARTAN 3A DSP FPGA之間存在什么形式的通信?它是基于公交車的嗎?有仲裁嗎?他們的溝通協議是什么?以上來自于谷歌翻譯以下為原文What form

2019-06-28 06:19:32

請教,一般DSP與FPGA之間EMIF通訊需要做數據校驗嗎?如果需要的話采用什么校驗方式呢?如果DSP采用的是DMA讀寫,那傳錯一個數據就得把那一堆數據重新傳了,這樣會不會影響實時性呢?

2020-07-30 06:24:46

請問一下單片機、ARM、MCU、DSP、FPGA、嵌入式之間有什么關系?

2021-09-18 06:34:03

本帖最后由 一只耳朵怪 于 2018-6-25 11:01 編輯

你好!我目前正在實現6657DSP 評估板與xilinx kintex7 FPGA之間的PCIE連接,其中DSP作為Root

2018-06-25 05:14:40

看到ADI的blackfin系列的DSP基本都有40位ALU,不知道這個在做視頻處理時有什么優勢?剛開始接觸視頻處理方面,對這個的基礎算法不太清楚,不知這個40位有什么特殊之處?如果用FPGA代替DSP外接40位DDR是否有用?

2018-09-30 11:37:09

功能轉為多個處理器與內核之間的任務調度。這樣會產生大量額外的代碼,而且這些代碼會成為系統開銷,而非用于解決眼前的數字信號處理問題。FPGA 技術的引入是解決 DSP 實現方案日益增長的復雜性的福音

2018-08-15 09:46:21

本文介紹了DSP 和FPGA 在數字電子設計中的優勢,并結合雷達模擬系統的硬件設計實例,重點闡述了相應的硬件與軟件實現方法。關鍵詞:DSP FPGA 數字電路設計雷達模擬系統

2009-08-25 14:33:01 15

15 FPGA實現DSP應用

摘要:具有系統級性能的FPGA在半導體工藝的線寬達到深亞微米后更進一步按信號處理的要求改進器件結構和性能,不僅可實現VLSI DSP,且具有系統

2010-04-01 15:39:54 14

14 FPGA的DSP應用

近年來由于多媒體技術和無線通信的發展,對DSP應用的要求不斷地增長,但是這些應用對信號處理要求高,需要采用處理速度高的硬件來實現DSP,所以,隨著CMOS工藝的

2010-04-07 14:25:58 16

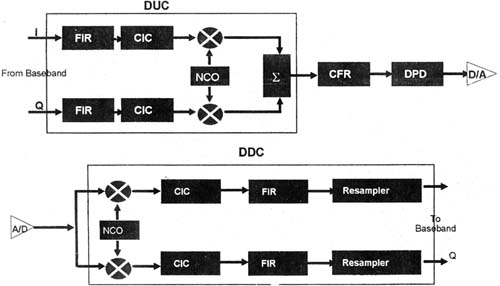

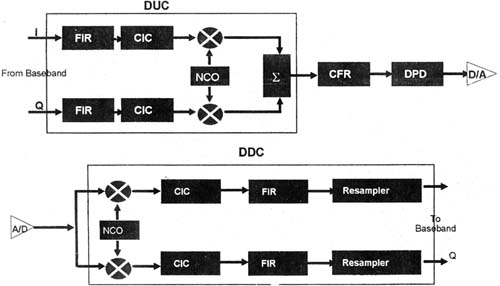

16 FPGA和DSP組合在無線基站中的應用

在自動控制產品中,CPD+DSP+MCU的構架是目前最為流行的成熟方案,而在通訊產品中,大量使用FPGA設計,合理使用FPGA

2009-10-12 11:20:11 975

975

基于DSP和FPGA的通用圖像處理平臺設計

摘要:設計一種基于DSP和FPGA架構的通用圖像處理平臺,運用FPGA實現微處理器接口設計,并對圖像數據進行簡單預處理,利用DSP

2010-02-01 11:10:21 1379

1379

淺析DSP智能攝像機發展的必然方向 (1)

隨著現代科學技術的發展,視頻監控系統也向智能化發展,而監控用的攝像機也必須智能化。DSP攝像機有普通

2010-03-25 14:23:30 979

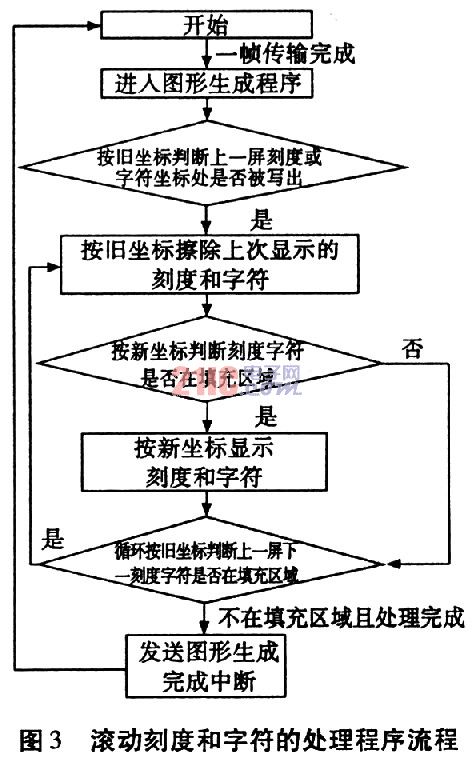

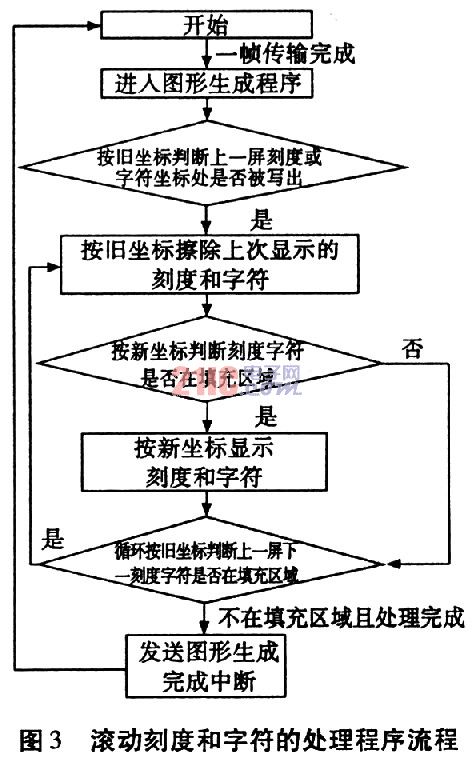

979 本文設計了基于DSP與FPGA的系統結構,采用了軟硬件填充的圖形處理方法,先由DSP軟件完成圖形輪廓生成,然后FPGA硬件圖形處理器根據圖形輪廓完成耗時的圖形填充,使系統在實時性

2010-07-01 11:02:38 988

988

摘要:為了實現高速HDLC通訊協議,設計了DSP+FPGA結構的485通訊接口,接口包括DSP、FPGA、485轉換等硬件電路,以及DSP與FPGA之間的數據交換程序和FPGA內部狀態機;其中DSP用于實現數據控制,FPGA用于實現HDLC通訊協議,DSP與FPGA之間采用XINTF方式,通過雙FI

2011-02-25 17:24:34 98

98 摘要:根據衛星數傳系統的要求,考慮FPGA的單拉子效應,提出一種多。印DSP+FPGA的衛星數據壓縮機的硬件結構。介紹了CCD相機與教據壓縮機之間的LVDS接口、數據壓縮機與綜合處理器之間的遙控遙測接口、硬件內部DSP與FPGA之間的串行EDMA方式通信接口的實現方法,

2011-02-27 23:08:56 61

61 【摘要】本文論述了FPGA在DSP應用上的優缺點,比較了FPGA芯片和DSP芯片之間的差別,介紹了解決隔閡的方案--Xtreme DSP軟件包和平臺級的Virtex Ⅱ芯片。最后,對Xtreme和VirtexⅡ芯片的特點進行了詳細說明。 關鍵詞:數字信號處理;可編程門陣列;芯片

2011-02-28 13:09:41 59

59 System Generator 工具由 MathWorks 與 Xilinx 合作開發而成,DSP 設計人員可使用 MATLAB 和Simulink 工具在 FPGA 內進行開發和仿真來完善 DSP 設計。 該工具為系統級 DSP 設計與 FPGA 硬件實現的融合起

2011-05-11 18:36:23 224

224 電子發燒友為您提供了ARM、DSP、FPGA三者的定義與其之間的區別!

2011-06-23 10:34:39 3665

3665 為滿足導航系統設計的小型化、實時性要求,本文提出了一種基于FPGA + DSP 的實現方案。該方案的設計思路是:將FPGA 映射到DSP EMIF 的一段地址空間,并用FPGA 來完成多通道信號的采集; DSP 根

2011-09-13 14:32:08 77

77 Alter FPGA的設計流程以及DSP設計.

2012-03-16 15:52:07 127

127 在雷達信號處理、數字圖像處理等領域中,信號處理的實時性至關重要。由于FPGA芯片在大數據量的底層算法處理上的優勢及DSP芯片在復雜算法處理上的優勢,DSP+FPGA的實時信號處理系統

2012-07-05 15:01:40 7272

7272

介紹了一種基于DSP和FPGA的磁鐵電源控制器的設計方案,闡述了該控制器硬件系統的組成,包括信號調理電路、中間數據處理部分、后端的驅動電路。同時給出了DSP和FPGA之間通過SPI接口

2012-07-27 16:20:31 36

36 設計了一種基于DSP與FPGA的運動控制器。該控制器以DSP為控制核心,用FPGA構建運動控制器與傳感器以及電機驅動器的接口電路。充分發揮了DSP強大的運算能力和FPGA的并行處理能力。具有

2012-10-26 15:21:51 93

93 如何在不同照明亮度、不同天氣以及攝像機本身震動等條件下對交通運行情況進行有效的探測和正確的反饋是亟待解決的難題。DSP與FPGA孰優孰劣的討論由來已久,筆者以智能交通視頻分析為主線,分析FPGA相較DSP方案,在攻克智能交通視頻分析難題中將發揮何種優勢。

2013-10-31 15:35:40 6722

6722 dsp fpga 電路 打標機上用的主板

2016-06-27 15:24:08 7

7 FPGA與ARM、DSP的區別

2017-03-15 08:00:00 9

9 在自動控制產品中,CPD+DSP+MCU的構架是目前最為流行的成熟方案,而在通訊產品中,大量使用FPGA設計,合理使用FPGA和DSP的組合,FPGA和DSP之間的智能配分可使無線系統設計師獲得最佳

2017-10-25 11:41:07 0

0 摘要 利用異步FIFO實現FPGA與DSP進行數據通信的方案。FPGA在寫時鐘的控制下將數據寫入FIFO,再與DSP進行握手后,DSP通過EMIFA接口將數據讀入。文中給出了異步FIFO的實現

2017-10-30 11:48:44 1

1 今天,FPGA越來越多地應用在多種DSP中。我們預計這一趨勢在未來幾年會更加明顯。美國調查機構Berkeley設計技術公司做了上述預測。以Xilinx和Altera為主的兩大FPGA廠商多年前就涉足

2017-11-06 10:48:09 1

1 今天,FPGA越來越多地應用在多種DSP中。我們預計這一趨勢在未來幾年會更加明顯。美國調查機構Berkeley設計技術公司做了上述預測。以Xilinx和Altera為主的兩大FPGA廠商多年前就涉足

2017-11-06 13:58:57 7

7 設計所需的足夠的可定制性。 市場研究公司Forward Concepts 2005年發表的一則調查報告稱,選擇處理器和FPGA的主要標準不是器件本身,而是開發它們的工具。這一概念對于包含FPGA和DSP處理器的平臺亦應成立。 在DSP處理器和FPGA之間,傳統的DSP開發者通常選

2017-11-06 13:59:42 2

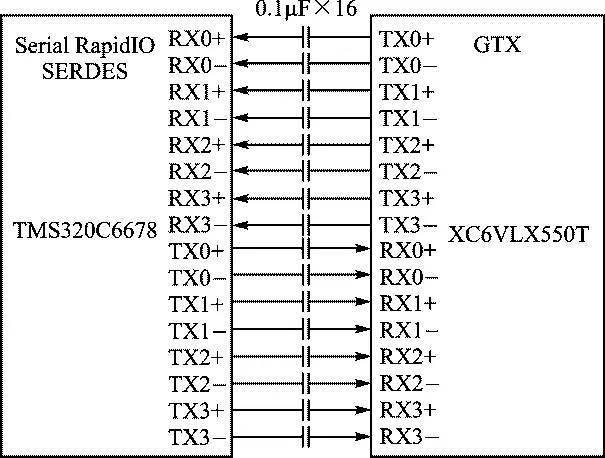

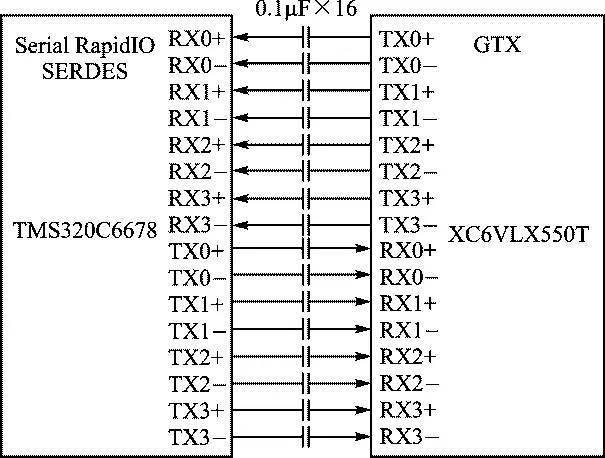

2 難度大,實現復雜算法也比較困難。因此,結合多核DSP和FPGA的優勢,構建基于異構處理器的信號處理系統成為當前一種發展趨勢。異構處理器間的高速通信成為高速信號處理系統[1]的關鍵問題之一,本文基于SRIO協議設計和實現了DSP與FPGA之間的高速數據通信。

2017-11-17 03:11:01 28802

28802

針對信號處理數據量大、實時性要求高的特點,從實際應用出發,設計了以雙DSP+FPGA為核心的并行信號處理模塊。為了滿足不同的信號處理任務需求,FPGA可以靈活地選擇與不同的DSP組成不同的信號處理

2017-11-17 06:11:40 2373

2373

本文首先分析了FPGA是否會取代DSP,其次介紹了FPAG結構特點與優勢及DSP的基本結構和特征,最后闡述了FPGA與DSP兩者之間的區別。

2018-05-31 09:51:25 35711

35711

型到大型的幾乎所有數字電路系統,dsp主要完成復雜的數字信號處理,如fft,通常一個復雜系統可以由單片機、arm、fpga、dsp中的一種或幾種構成,各有優勢和不足。dsp通常用于運算密集型,fpga

2018-09-11 11:49:53 303

303 隨著模擬IC市場中眾多垂直細分行業的飛速發展,傳統DSP器件遭遇了各種替代性信號處理平臺的競爭,FPGA即為典型代表。憑借高密度、低功耗和低成本的優勢,FPGA不僅在通信、消費類、嵌入式等廣泛領域中行使DSP的職能,并且已經快速滲透到諸多新興應用領域之中。

2018-11-05 17:53:15 1775

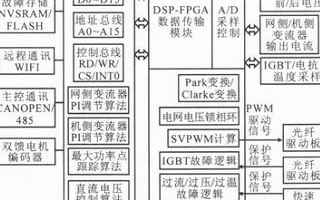

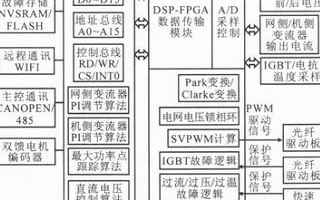

1775 目前風電技術可分為恒速恒頻控制方式和VSCF控制方式。VSCF風力發電機可提供更高的風能利用效率,故越來越多地用于大功率機組。在此設計了基于TMS320C28346型DSP與FPGA的雙饋式風力發電

2019-05-20 16:32:37 1744

1744

FPGA的并發可以在不同邏輯功能之間進行,而不局限于同時執行相同的功能。流水是通過將任務分段,段與段之間同時執行。

2019-06-19 17:50:49 11883

11883 FPGA的優勢有三個方面:1)通信高速接口設計。FPGA可以用來做高速信號處理,一般如果AD采樣率高,數據速率高,這時就需要FPGA對數據進行處理。

2020-01-10 15:46:21 1073

1073 型到大型的幾乎所有數字電路系統,dsp主要完成復雜的數字信號處理,如fft,通常一個復雜系統可以由單片機、arm、fpga、dsp中的一種或幾種構成,各有優勢和不足。 dsp通常用于運算密集型,fpga用于控制密集型,許多人都用dsp高算法,用fpga作外圍控制

2020-10-25 09:50:06 3085

3085 隨著高性能信號處理系統對運算速度、通信速率等要求的不斷提高,單獨的處理器(如FPGA或DSP)無法滿足高速實時信號處理的需求。

2023-02-27 16:27:55 4762

4762

摘要: 現代 信號 處理系統通常需要在不同處理器之間實現高速數據 通信 ,SRIO協議由于高效率、低延時的特性被廣泛使用。本文研究了在 FPGA 和 DSP 兩種處理器之間實現SRIO協議的方法

2023-03-20 15:00:01 1324

1324 廣州星嵌DSP/ARM/FPGA 選型手冊2023

2023-05-05 10:24:22 15

15 MCU(Microcontroller Unit)、DSP(Digital Signal Processor)和FPGA(Field-Programmable Gate Array)是嵌入式系統中常見的三種處理器類型,它們之間有以下主要區別:。

2023-10-26 10:12:46 1670

1670

電子發燒友App

電子發燒友App

評論