隨著微電子技術和超大規模集成電路技術的高速發展,進行電子系統設計時的系統復雜度不斷加大,系統軟件硬件的異構度提高,軟件在系統中所占的比例也越來越大。傳統的設計方法在進行電子系統設計時,一般先由系統工程師設計整個系統的架構,畫出系統框圖(包括各個模塊),再用高級編程語言(一般是C/C++/JAVA)實現各個模塊的算法,然后進行整個系統的仿真,確定系統的最佳結構、最佳實現算法及其它相關參數。待系統模型確定以后,進行系統軟硬件分割設計,但由于缺乏統一的軟硬件協同設計驗證平臺,大多只能根據經驗來定義軟件和硬件部分各自應完成的功能。對于整個系統的功能和行為,在設計最初階段,描述時尚無硬件的概念,經過軟硬件劃分之后,將系統規范描述分成軟件實現和硬件實

現兩部分。雖然VHDL等語言也支持算法級描述,但是大部分硬件描述語言HDL(HardwareDescriptionLanguage)如VHDL、Verilog等基本上還是面向硬件的描述,面向較低的硬件抽象等級。同時由于高級編程語言(C/C++/JAVA)不能描述硬件設計中的時間、延遲、信號等物理信息,與后續的硬件設計不兼容,硬件部分需重新用VHDL、Verilog等硬件描述語言來設計,造成大量的設計重復,也增加了系統設計的復雜度。

另外,許多要用硬件實現的功能,例如快速傅立葉變換FFT、掃描線算法、消隱算法等成熟而又常用的算法都有現成、完善的C語言描述,如果可以復用這些資源將節省大量的系統設計時間。

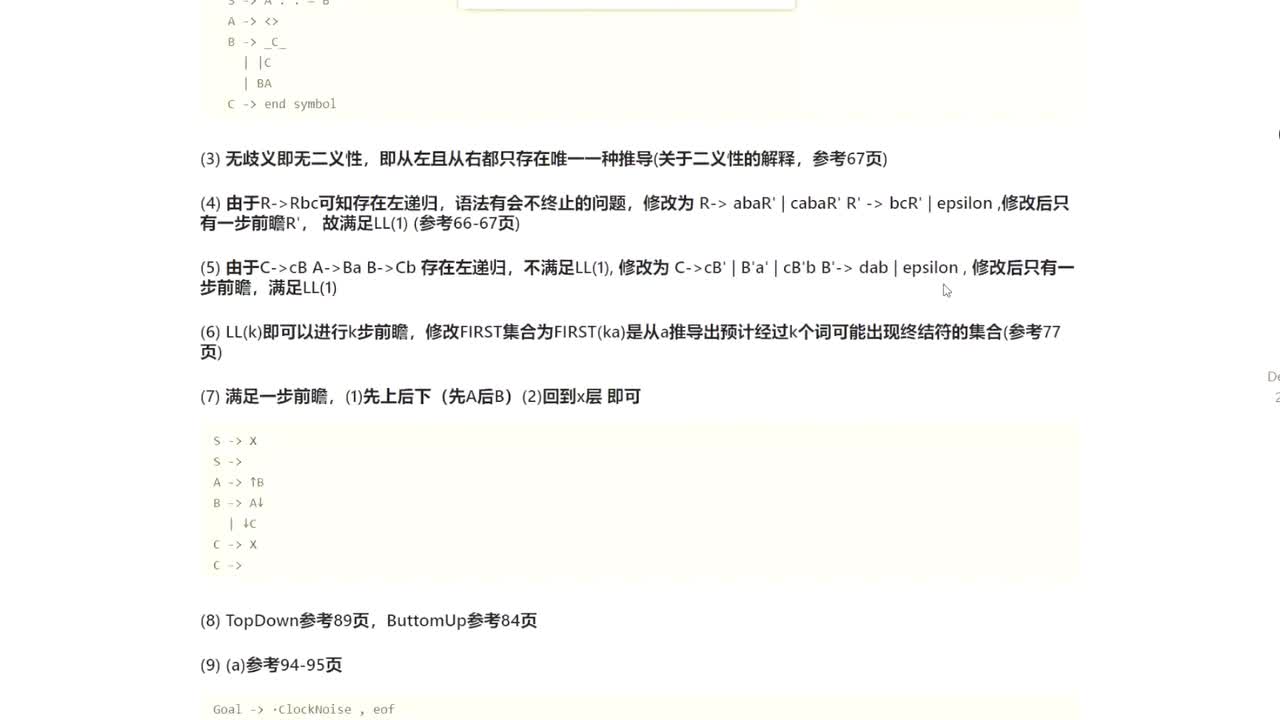

很多EDA工具只能理解HDL語言的描述,它是設計者和系統之間的界面,設計者通過HDL語言將自己的設計方案告訴EDA工具,在EDA工具的幫助下進行模擬、綜合和驗證。所以系統設計中用C語言的描述要轉換為HDL語言才能被EDA工具接受。在眾多HDL語言中,VHDL語言是被廣泛使用的,因此設計和實現一個從C語言轉換到VHDL語言的編譯器具有重要意義和很大的實用價值。

C與VHDL的語言特征

C語言是目前國際上廣泛流行的一種計算機高級語言,適合于作為系統描述語言,既可用來編寫系統軟件,也可用來編寫應用軟件。C語言是在B語言的基礎上發展起來的,既保持了B語言的優點(精練,接近硬件),又克服了其缺點(過于簡單,數據無類型等)。后來,C語言多次作了改進。1978年后,C語言已先后移植到大、中、小、微型機上,并獨立于UNIX和PDP。

1983年,美國國家標準化協會(ANSI)對C語言的各種版本進行綜合和擴充,制定了新的標準,稱為ANSIC。總的說來,C語言適合描述過程和算法,它的運行環境是圖靈機模型。它具有很多靈活的描述方式,具有較高的抽象能力,不區分函數和過程。數組的定義以及對指針的靈活應用大大方便了程序的書寫,同時因其是為開發軟件而設計的語言,因而更善于描述串行程序。但是由于其不能體現硬件設計中的時間、延遲、信號等物理特性,硬件模塊部分需重新用硬件描述語言來設計,與后續設計缺乏連貫性,也增加了系統設計的復雜度。

VHDL(Very-High-SpeedIntegratedCircuitHardwareDe2scriptionLanguage)語言是目前應用較廣泛的一種硬件描述語言,被IEEE(TheInstituteofElectricalandElectricEngineers)和美國國防部確定為標準硬件描述語言,并得到了眾多EDA公司的支持,在電子工程領域已成為事實上的通用硬件描述語言。VHDL既可以結構化的分層次的描述電路結構特性,也可以表示電路輸入輸出信號的關系特性,還可以描述和芯片布圖有關的幾何特性。它是一種較規整的語言,適合于描述并發程序。但是由于其最初目的并非是為電路設計的,而是用來描述電路的,因此它不適合進行系統級的軟件設計和算法設計,特別是現在系統中越來越多的功能由軟件來完成時。

設計方案

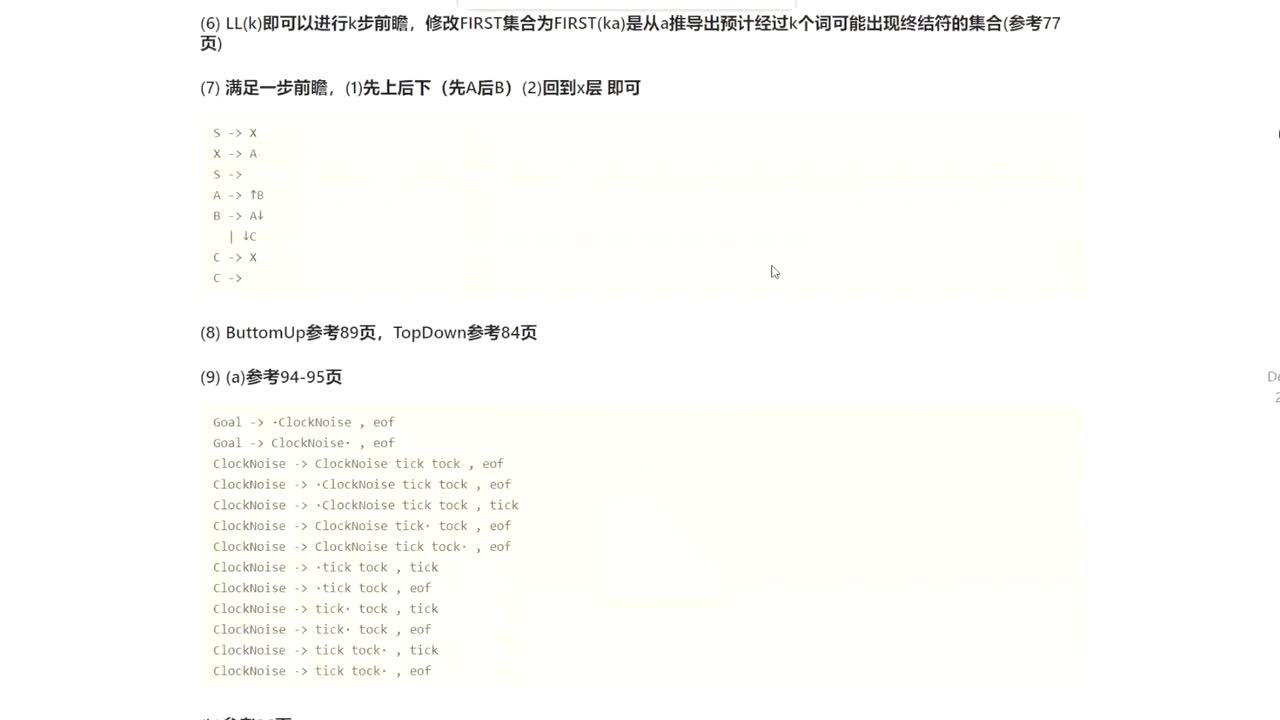

C語言和VHDL語言是兩種面向不同領域,各有所長的語言,設計與實現一個C到VHDL的編譯器即是把要用硬件來實現的C語言算法描述翻譯成VHDL語言的行為描述。為了完成從C語言向VHDL的編譯轉換,首先用Lex和Yacc完成詞法分析和語法分析。在語法分析的時候生成一棵C的語法樹,,并在自下而上生成語法樹的過程中收集綜合屬性。同時在此過程中進行語義分析———只分析和翻譯與編譯轉換有關的信息,那些與C語言本身有關的語義則不做分析,比如是否有變量被重復定義等。在語法樹的展開過程中向下傳遞繼承屬性并進行轉化,將C的規約規則翻譯為相應的VHDL規約規則。

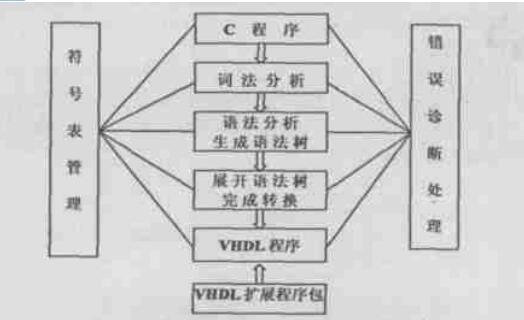

圖1C到VHDL的編譯器實現過程

編譯器的具體設計與實現過程見圖1。在語法分析的過程中生成一棵語法樹———多叉樹,其葉子節點記錄C程序中的單詞,并記錄單詞的位置、屬性、值等,非葉子節點記錄C語言的規約規則以及要傳遞的屬性———包括綜合屬性和繼承屬性。

由于C語言較靈活而VHDL語言較規整,因此這里只選擇一定范圍內的較常用的C語言語法子集進行轉換;因為VHDL只有可綜合子集可以實現,所以在轉換時必須考慮可綜合子集的限制;并且VHDL語言的數據類型有限,我們必須編寫擴充數據類型的VHDL程序包,在展開語法樹完成轉換過程中用來描述復雜的邏輯。

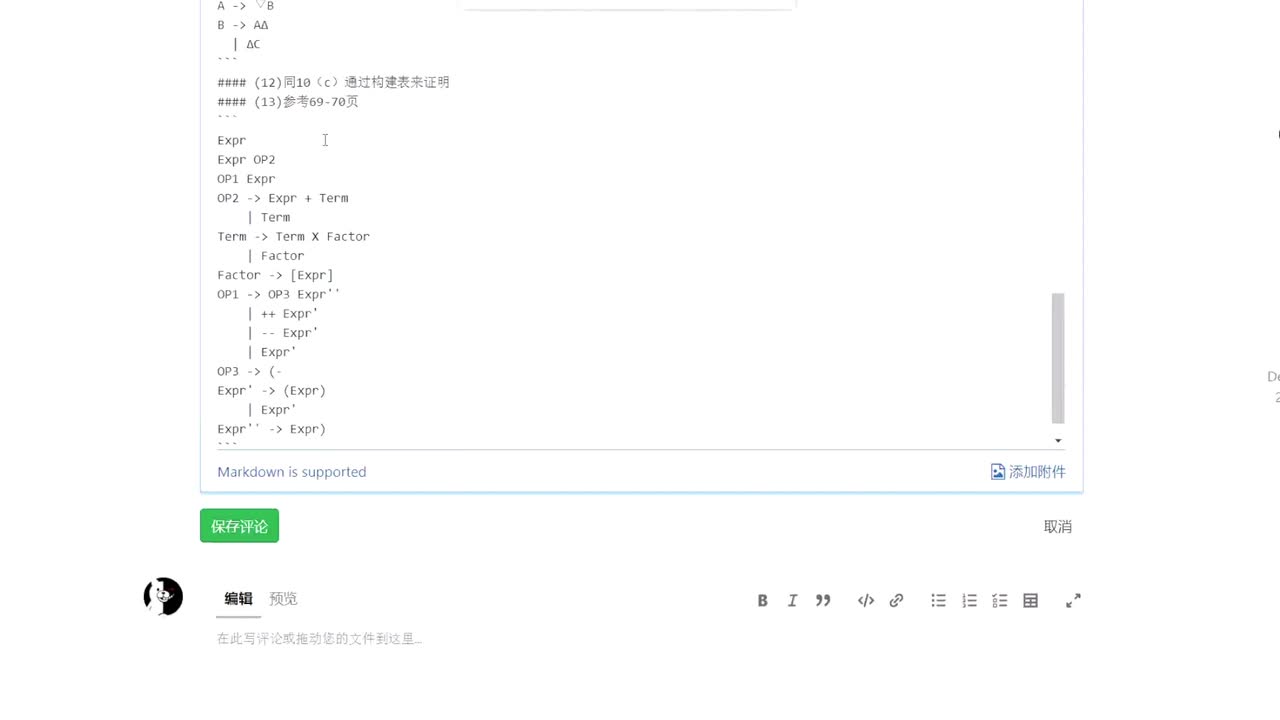

轉換過程

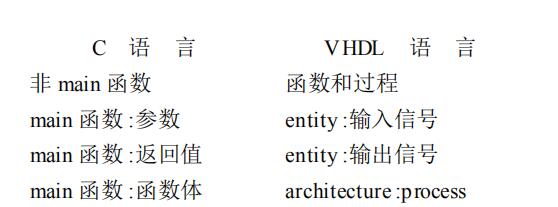

由于C語言善于描述串行程序而VHDL適合描述并發程序,因此對于C程序中的非main函數轉化為VHDL中的函數(有返回值的)和過程(無返回值的);對于main函數,將main函數的參數作為entity的輸入信號,將main的返回值作為entity

的輸出信號,將main的函數體作為architecture的一個process。雖然VHDL通常描述并發程序,但其子程序和process仍是順序執行的,與C語言的原始描述一致。具體函數對應情況見表1。

轉換過程中,通過分析兩種語言的差別,對于C語言的一些獨特、靈活的描述方式———指針、類型轉化、連等、i++和++i的處理、數組、逗號表達式等方面的正確翻譯比較關鍵和重要。

對于C語言中的指針,要將它在C語言中的作用完全翻譯到VHDL比較困難,因為C語言的指針實質上是與地址、與內存的分配有關。而VHDL作為一種描述硬件的語言,不存在地址的概念。因此在具體轉換中將指針類型翻譯為整數類型,并記錄所指向數組的名字,整數值表示指向數組中的第幾個元素。由于C的高維指針經過內存分配所得到,在VHDL中很難實現,因此初步實現一維指針,而帶高維指針的C程序可以轉換為一維指針來實現。

對于i++和++i,翻譯i++時先記錄哪些變量要經過這類操作,在完成對表達式的翻譯后再處理。而翻譯++i時因為變量值立刻變化,因此在翻譯時必須將一個完整的表達式分開,并引入臨時變量來處理。

相對于C語言中靈活的類型轉化,VHDL則嚴格的多,不允許不同類型之間運算。由于C語言沒有boolean類型,而VHDL語言有boolean類型,所以在條件表達式中要將整數或其它類型的數轉換為boolean類型。同時,在處理C中整數的邏輯運算時,必須先將整數轉換為VHDL的Bit-Vector來運算,計算后再轉換回來。

另外,由于C語言不區分函數和過程,但是VHDL嚴格區分,而且函數只能出現在表達式中,因此對于沒有出現在表達式中的函數調用,翻譯時要將其放在一個臨時表達式中,賦值給一個臨時變量。

測試及分析

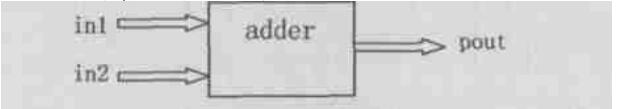

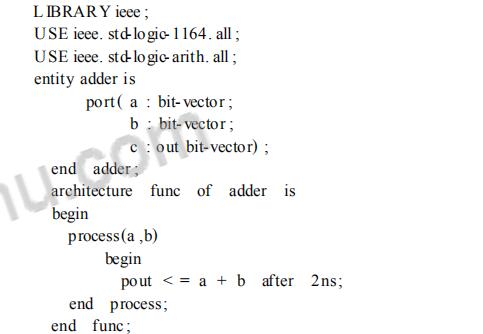

為了測試本文提出的設計方案的正確性和有效性,在設計過程中選取了一些常用的數字電路系統來比較C源程序和VHDL目標程序的功能一致性。例如對于一個無控制端口的加法器電路,其電路示意圖見圖2

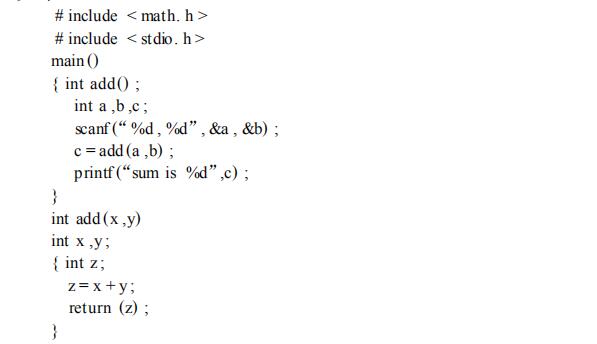

該加法器不帶任何控制端口,有兩個輸入端口in1和in2,一個輸出端口pout,它們的類型皆為位向量。當輸入信號中有任何一個或者兩個都發生變化時,進程就要再重新執行一遍。從電路功能的角度來理解:只要在輸入端有新的數據輸入,那么加法器必然要重新開始工作,將新的數值相加并送到輸出端口,這樣不斷地進行加法操作。對于加法器電路的C語言描述如下

利用本文提出的設計方案對實現加法器功能的C 語言程序進行編譯轉換, 得到轉換后的目標程序———VHDL 程序如下:

通過分析編譯轉換后的目標程序的語法語義和功能證明轉換方案是正確和有效的。由于用C 語言進行算法和程序設計,可以大大提高系統描述的層次和系統設計效率,并且有大量成熟、完善的用C 描述的算法可以復用,而VHDL 語言則是大多數EDA 工具所接受的硬件描述語言,因此設計與實現一個從C 語言轉換到VHDL 語言的編譯器具有重要意義和很大的實用價值。

本文分析了C 與VHDL 的語言特征及各自的優缺點,提出了合理有效的轉換方案,指出從C 向VHDL 轉換時需重點注意的幾個方面,并對設計方案進行了測試分析,得到較滿意的結果。

電子發燒友App

電子發燒友App

評論