最近在做FFT IP核,,走了好多彎路,LISENCE激活過(guò)了0034的IP核,通過(guò)修改LISENCE.DAT的方法。后來(lái)生成FFT的時(shí)候卡住,又嘗試了關(guān)閉quartus_map進(jìn)程和重裝jre

2019-04-03 16:16:21

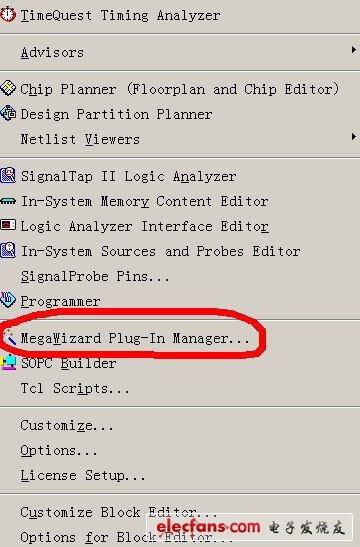

這樣的菜單欄。如下圖 然后就是按部就班的來(lái)了,設(shè)置參數(shù)啊,生成仿真文件啊完成啊。 (5)然后就可以在.v或原理圖文件中調(diào)用了。 (6)具體使用方法要看使用文檔的。 2.文件破解(我想這個(gè)

2019-06-03 09:09:51

本帖最后由 lee_st 于 2017-10-31 09:24 編輯

Quartus-II-使用方法

2017-10-30 17:03:27

Quartus-II-使用方法簡(jiǎn)介,本文是ppt文檔,

2017-11-09 13:03:37

Quartus II 中管腳上拉電阻(弱上拉)的設(shè)置方法Quartus II 中管腳上拉電阻(弱上拉)的設(shè)置方法在使用 Altera 的 FPGA 時(shí)候,根據(jù)系統(tǒng)設(shè)計(jì)需要在管腳的內(nèi)部加上上拉電阻

2012-08-12 16:10:09

Quartus II中Tsu/Tco的約束方法是什么

2021-04-29 06:36:32

的大部分功能,以及設(shè)計(jì)Altera最新CPLD和低成本FPGA系列所需的一切。Quartus II網(wǎng)絡(luò)版軟件還支持Altera高密度系列中的入門(mén)級(jí)產(chǎn)品。Quartus II訂購(gòu)版軟件提供:支持所有

2012-08-15 12:30:03

如題:我之前用Quartus ii 13創(chuàng)建的工程。現(xiàn)在改用17了。想編輯以前的IP核但是找不到MegaWizard Plug-In Manager 了

2017-09-24 21:06:09

請(qǐng)問(wèn)一下ATAN ip核中的輸出為什么經(jīng)常出現(xiàn)3F800000?而且我的輸入是很多零中插著一個(gè)有效值,但是很多情況下的輸出是連著有兩個(gè)不為零的輸出啊?其中第一個(gè)還是固定的80000000???很無(wú)助啊 。。。。好人一生平安!!!!

2017-04-14 15:40:46

關(guān)于QuartusⅡ10.1中NIOS2軟核的構(gòu)建、軟件編譯及程序固化 一、硬件開(kāi)發(fā)1、構(gòu)建CPU模塊2、構(gòu)建EPCS控制器,SYSTEM ID模塊,JTAG UART模塊3、構(gòu)建RAM模塊(1

2022-01-25 07:58:08

本帖最后由 eehome 于 2013-1-5 09:46 編輯

Quartus_II_9.0破解詳細(xì)說(shuō)明(圖文并茂)很好用!!!!

2012-12-30 21:33:44

我想問(wèn)一下,在quartus上直接調(diào)用IP核和在qsys中用IP核有什么區(qū)別?自個(gè)有點(diǎn)迷糊了

2017-08-07 10:09:03

我調(diào)用了一個(gè)ip核 在下載到芯片中 有一個(gè)time-limited的問(wèn)題 在完成ip核破解之后 還是無(wú)法解決 但是我在Google上的找到一個(gè)解決方法就是把ip核生成的v文件加到主項(xiàng)目文件中就是上面

2016-05-17 10:28:47

本帖最后由 liu1032042013 于 2017-5-3 22:16 編輯

使用quartus 12.1生成NCO IP 核失敗,進(jìn)度條一直卡著不動(dòng),經(jīng)百度得網(wǎng)友分享的方法,成功解決問(wèn)題

2017-05-02 21:39:22

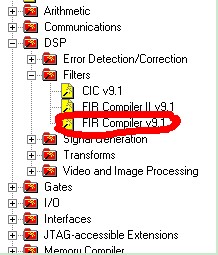

quartus II 13.1調(diào)用FIR 這個(gè)IP核生成時(shí)一直卡著,怎么解決? 系統(tǒng)版本是win7 64位 專業(yè)版,我試過(guò)網(wǎng)上說(shuō)的①在license中改相應(yīng)IP核的序列號(hào)②在任務(wù)管理器中關(guān)閉

2017-08-08 11:42:19

quartus 11.0 IP核的simulation如果勾選 就生成不出IP核出錯(cuò),但是不選的話就沒(méi)辦法RTL仿真 求大神問(wèn)題原因或者解決方法

2016-11-25 20:39:45

最近剛換了win7 64位系統(tǒng),重裝QUARTUS II 13.0并破解后,針對(duì)IP核FIR的設(shè)計(jì)編譯出現(xiàn)如下錯(cuò)誤:Error (10003): Can't open encrypted VHDL

2014-08-11 17:19:22

請(qǐng)教各位大師,quartus ii 中調(diào)用fir數(shù)字濾波器IP核,可不知道如何設(shè)置參數(shù),比如如何設(shè)置濾波器的系數(shù)

2013-11-23 20:54:41

quartus ii 調(diào)用DDR2 IP核時(shí)無(wú)法生成 ( 已經(jīng)完成破解獲得ddr2的license)

2017-02-07 17:29:25

quartus ii 的原理圖文件如何與modelsim-altera聯(lián)合仿真?

2013-04-14 21:51:13

quartus ii中的fir Ⅱ核的可重構(gòu)濾波器和雙通道的程序應(yīng)該如何寫(xiě),請(qǐng)問(wèn)大家有這方面的例程嗎

2017-09-26 16:05:55

2.5MHz 振幅0-5V 的正弦信號(hào),請(qǐng)問(wèn) data 端口應(yīng)該輸入怎樣的信號(hào)?如果有Altera IP核相關(guān)的詳解資料推薦下更好。多謝了。

2014-10-28 12:34:41

本帖最后由 ys_1*****8201 于 2016-5-19 14:16 編輯

Quartus IP核破解在完成quartus軟件安裝之后,一般都要進(jìn)行一個(gè)軟件破解。對(duì)于一般的需求來(lái)說(shuō)

2016-05-19 14:13:09

quartus 編譯顯示沒(méi)有ip核權(quán)限,生成的pof文件是time-limited,然后我在網(wǎng)上找了一個(gè)全ip權(quán)限的licsense文件,HOSTID也替換好了,可是編譯又顯示該lic文件沒(méi)有我要用

2017-01-16 20:16:27

quartus的IP核,怎么用啊,有誰(shuí)有這方面的資料嗎?求助 啊

2014-10-29 10:23:19

圖文詳解IEEE1394端子引腳

2021-06-01 06:22:33

用Quartus II 調(diào)用IP核時(shí),在哪可以查看IP核的例程

2014-07-27 20:28:04

小弟用的quartus ii軟件,調(diào)用altera公司的一個(gè)乘法器lpm_mult,無(wú)結(jié)果輸出,是不是調(diào)用的IP核都要收費(fèi)呢,有沒(méi)有辦法破解呢????

2015-06-05 11:23:31

我在用fir 核做半帶插值濾波器時(shí),自己寫(xiě)好tb后,直接用quartus ii 調(diào)用modelsim仿真時(shí),出錯(cuò),提示說(shuō)找不到auk_dspip_lib 庫(kù)怎么解決呀,謝謝大家

2017-11-24 19:28:15

`Xilinx系列FPGA芯片IP核詳解(完整高清書(shū)簽版)`

2017-06-06 13:15:16

我用quartus II調(diào)用modelsim仿真fft ip核,仿真結(jié)束后我想驗(yàn)證下數(shù)據(jù)是否正確,結(jié)果是:我用matlab生成同樣的整形數(shù)據(jù),然后用modelsim仿出的結(jié)果txt文件與用

2012-09-20 12:48:37

數(shù)學(xué)運(yùn)算(乘法器、除法器、浮點(diǎn)運(yùn)算器等)、信號(hào)處理(FFT、DFT、DDS等)。IP核類似編程中的函數(shù)庫(kù)(例如C語(yǔ)言中的printf()函數(shù)),可以直接調(diào)用,非常方便,大大加快了開(kāi)發(fā)速度。使用Verilog調(diào)用IP

2018-05-15 12:05:13

有沒(méi)有大神可以提供xilinx FPGA的FFT IP核的調(diào)用的verilog 的參考程序,最近在學(xué)習(xí)FFT的IP核的使用,但是仿真結(jié)果有問(wèn)題,所以想找些參考設(shè)計(jì),謝謝

2016-12-25 17:05:38

講,主要通過(guò)演示FPGA數(shù)字邏輯設(shè)計(jì)中除Verilog代碼方式設(shè)計(jì)外另外一種最常用的設(shè)計(jì)方式——使用IP核進(jìn)行系統(tǒng)設(shè)計(jì)。本教程講解了如何在Quartus II軟件中調(diào)用一個(gè)基本的免費(fèi)IP核——計(jì)數(shù)器IP核

2015-09-22 14:06:56

和顯示實(shí)時(shí)信號(hào),觀察在系統(tǒng)設(shè)計(jì)中的硬件和軟件之間的互相作用。Quartus II軟件可以選擇要捕獲的信號(hào)、開(kāi)始捕獲的時(shí)間,以及要捕獲多少數(shù)據(jù)樣本。還可以選擇時(shí)間數(shù)據(jù)從器件的存儲(chǔ)器塊通過(guò)JTAG端口

2016-10-11 22:24:16

通過(guò)Quartus II 軟件創(chuàng)建PLL IP核。首先,要新建一個(gè)工程,這個(gè)方法在之前的帖子中已經(jīng)發(fā)過(guò),不會(huì)的可以查看前面的相關(guān)帖子。創(chuàng)建好自己的工程:打開(kāi)如下的菜單

2016-09-23 21:44:10

`最近做仿真需要用到Quartus ii里的ROM IP核,為了驗(yàn)證功能,我新建了工程,生成IP核,數(shù)據(jù)深度512,位寬8bit,用MATLAB產(chǎn)生512個(gè)隨機(jī)整數(shù),新建hex文件,將512個(gè)隨機(jī)數(shù)

2015-12-22 23:14:53

各位大俠好,幫忙看下我的問(wèn)題: 嘗試用Quartus II生成DDR2的IP核,調(diào)用"MegaWizard Plug-in Manager",然而無(wú)法生成DDR2的IP核,不知

2016-04-27 09:37:35

用quartus ii 中自帶的ip核創(chuàng)建了一個(gè)rom,并加載了初始的hex數(shù)據(jù)。當(dāng)我從rom中讀出數(shù)據(jù)的時(shí)候,發(fā)現(xiàn)前面兩個(gè)地址(0000,0001)的輸出數(shù)據(jù)不正確,0002輸出數(shù)據(jù)是地址0000對(duì)應(yīng)的數(shù)據(jù),即地址偏移了2位,請(qǐng)教給位大蝦這是怎么回事?應(yīng)該如何解決?

2013-05-14 14:38:21

quartus ii9.0創(chuàng)建的ip核,生成的一些文件,(.qip、 add_sub_bb.v、add_sub.v)這些文件都有用嗎,想在其他工程里調(diào)用這些IP核,這幾個(gè)文件全部要添加嗎?

2013-07-02 17:20:01

在Altera Quartus II下如何調(diào)用ModelSim進(jìn)行仿真?

2021-04-30 07:15:55

在quartus II13.0版本上調(diào)用FFT IP核并進(jìn)行modelsim-altera仿真,在生成IP核時(shí),step2中勾選generate simulation model、generate

2016-10-07 22:23:33

核的分類和特點(diǎn)是什么?基于IP核的FPGA設(shè)計(jì)方法是什么?

2021-05-08 07:07:01

如何通過(guò)Quartus II軟件生成一個(gè)雙端口的RAM IP核?

2022-01-18 07:40:47

向大家請(qǐng)教個(gè)問(wèn)題,怎么破解QUARTUS中IP呢?按照網(wǎng)上有的方法,每次只能破解一個(gè)ip核,可我想在我的工程中使用多個(gè)需要破解的ip核怎么做呢?

2016-11-20 15:35:48

數(shù)學(xué)運(yùn)算(乘法器、除法器、浮點(diǎn)運(yùn)算器等)、信號(hào)處理(FFT、DFT、DDS等)。IP核類似編程中的函數(shù)庫(kù)(例如C語(yǔ)言中的printf()函數(shù)),可以直接調(diào)用,非常方便,大大加快了開(kāi)發(fā)速度。使用Verilog調(diào)用IP

2018-05-16 11:42:55

Altera® Quartus® II 設(shè)計(jì)軟件為可編程芯片系統(tǒng)(SOPC) 提供最全面的設(shè)計(jì)環(huán)境。如果您以前使用MAX+PLUS®II 軟件、其它設(shè)計(jì)軟件或 ASIC 設(shè)計(jì)軟件,現(xiàn)在準(zhǔn)備改用Quartus II 軟件

2009-04-21 23:07:15 1021

1021 Quartus II Fitter 也稱作PowerFit Fitter,執(zhí)行布局布線功能,在Quartus II軟件中是指“fitting( 適配)”。Fitter 使用由Analysis & Synthesis 建立的數(shù)據(jù)庫(kù),將工程的邏輯和時(shí)序要求與器件

2009-04-21 23:11:38 4873

4873 ALTERA QUARTUS II軟件使用:IC 設(shè)計(jì)入門(mén) (三) ALTERA QUARTUS II軟件使用第一章概述IC設(shè)計(jì)沒(méi)有捷徑,唯有花時(shí)間及努力,才會(huì)有機(jī)會(huì)入行學(xué)習(xí)軟件使用并不是啥大事.一般工程師也只

2009-10-27 14:06:56 175

175 Quartus II的仿真實(shí)驗(yàn)資料

選擇Quartus II軟件“File”菜單的“New”選項(xiàng),打開(kāi)新建其他文件對(duì)話框,選擇新建波形圖文件,

2010-02-08 16:59:10 114

114 Quartus II 中文教程

您現(xiàn)在閱讀的是 Quartus II 簡(jiǎn)介手冊(cè)。 Altera® Quartus® II 設(shè)計(jì)軟件是適合單芯片可編程系統(tǒng) (SOPC) 的最全面的設(shè)計(jì)環(huán)境。 如果您以前用過(guò)

2010-03-11 14:41:58 231

231 Quartus_II免費(fèi)下載

2012-11-02 17:20:56 178

178 quartus ii安裝下載

2012-11-09 16:30:09 51

51 quartus.ii免費(fèi)安裝

2012-11-14 14:57:47 56

56 Quartus ii 11軟件安裝

2013-12-27 09:39:53 36

36 Quartus II建立VHDL工程教程,簡(jiǎn)單易學(xué),適合初學(xué)者

2015-11-12 17:21:17 0

0 Quartus II Introduction Using Verilog Design

2015-11-24 11:42:20 6

6 Quartus II安裝入口

2015-11-24 16:57:04 13

13 quartus_II教程,又需要的下來(lái)看看

2016-05-19 15:16:15 0

0 Quartus_II使用指南(非常詳細(xì))

2016-05-19 15:16:15 0

0 quartus_II中文用戶教程,又需要的下來(lái)看看

2016-05-19 15:16:15 0

0 Quartus II中文用戶教程,有需要的下來(lái)看看

2016-07-29 18:08:19 79

79 倒車影像安裝方法圖文詳解,感興趣的小伙伴們可以看看。

2016-08-03 16:15:22 85

85 本文以 Quartus II 11.0 軟件的安裝為例,作為安裝指南。此外,關(guān)于 Quartus II 10.0 以前版本,安裝都大同小異。對(duì)于 Quartus II 11.0 ,最基本的套件包含以下三個(gè)部分:(1)Quartus II 11.0 for windows 軟件

2017-11-07 17:10:22 7

7 Quartus II軟件的使用

2017-11-14 17:48:27 12

12 Quartus II 13.0安裝說(shuō)明

2018-02-06 14:45:21 20

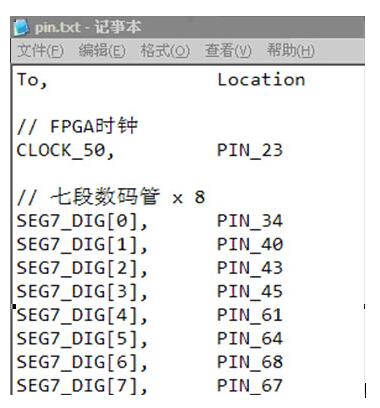

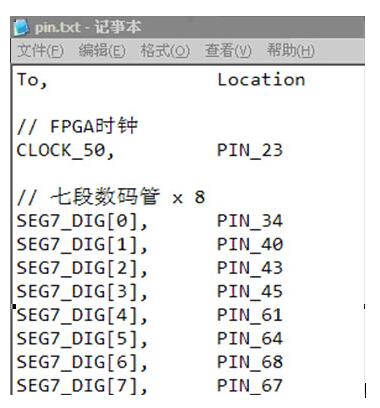

20 將Quartus II中FPGA管腳的分配及保存方法做一個(gè)匯總。本文首先介紹了FPGA 的管腳分配方法,其次介紹了Quartus II自動(dòng)添加管腳分配的方法,最后闡述了FPGA管腳分配文件保存方法,具體的跟隨小編一起來(lái)了解一下吧。

2018-05-16 11:44:41 47376

47376

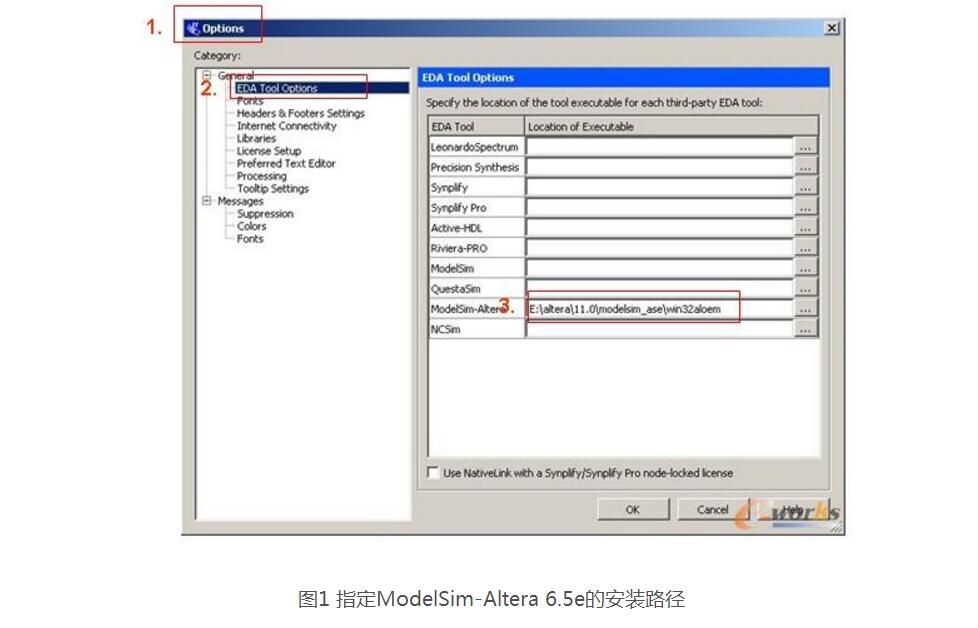

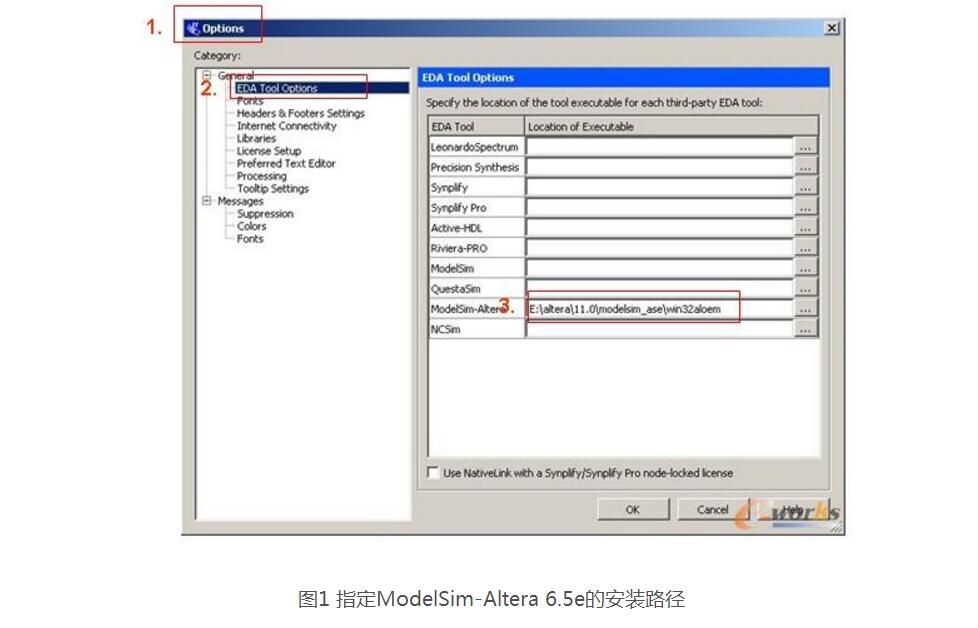

本文主要詳細(xì)介紹了在Quartus II 11.0中調(diào)用ModelSim-Altera 6.5e,另外還介紹了Quartus II調(diào)用modelsim無(wú)縫仿真教程。

2018-05-18 10:39:16 34625

34625

本文檔的主要內(nèi)容詳細(xì)介紹的是FPGA視頻教程之Quartus.II調(diào)用ModelSim仿真實(shí)例詳細(xì)資料說(shuō)明。

2019-03-05 10:46:46 13

13 如果是第一次使用modelsim,需要建立Quartus ii12.0和modelsim的鏈接。Quartus II12.0-》Tools-》option-》EDA Tool options再選擇自己的軟件和對(duì)應(yīng)的安裝文件夾。

2019-03-07 15:45:18 24331

24331 本文檔的主要內(nèi)容詳細(xì)介紹的是如何制作一個(gè)方便在Quartus II和Nios II中使用的簡(jiǎn)單IP。

2019-07-09 17:40:00 2

2 Quartus II可以在Windows、Linux以及Unix上使用,除了可以使用Tcl腳本完成設(shè)計(jì)流程外,提供了完善的用戶圖形界面設(shè)計(jì)方式。具有運(yùn)行速度快,界面統(tǒng)一,功能集中,易學(xué)易用等特點(diǎn)。

2019-11-15 07:04:00 3172

3172

quartus II 學(xué)習(xí)基礎(chǔ)材料

2020-08-11 17:36:00 18

18 Quartus II軟件為使用Altera?FPGA和CPLD設(shè)備進(jìn)行設(shè)計(jì)的系統(tǒng)設(shè)計(jì)師提供了一個(gè)完整的軟件解決方案。Quartus II程序員是Quartus II軟件包的一部分,它允許您編程

2020-09-17 14:41:00 32

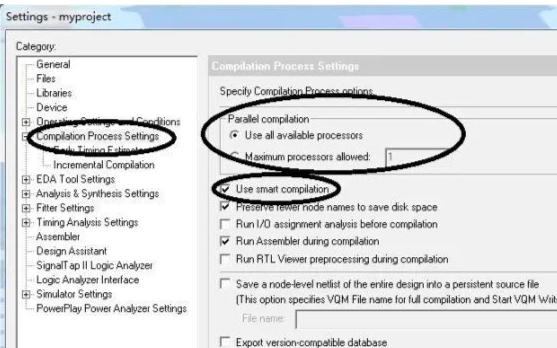

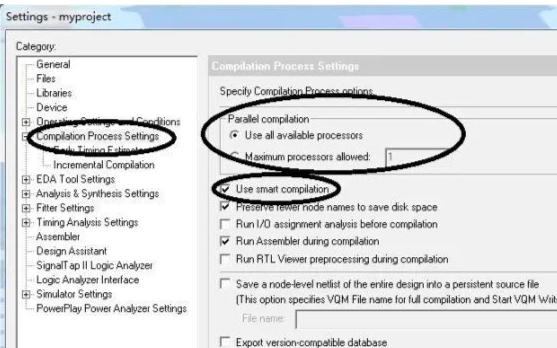

32 對(duì)于減少Quartus II的編譯時(shí)間的方法,可從三個(gè)角度進(jìn)行考慮。

2021-05-18 10:27:25 4046

4046

圖文詳解:無(wú)刷電機(jī)的繞制和接線方法

2021-05-25 11:48:29 117

117 任務(wù)及要求任務(wù)一:熟悉 Quartus II 開(kāi)發(fā)環(huán)境,掌握原理圖輸入方式,在 Quartus II 中用原理圖方式實(shí)現(xiàn)半加器,并用 Quartus II5.1 中的波形仿真。仿真成功后,生成半加器圖形符號(hào)以供后續(xù)程序調(diào)用。任務(wù)二:在 Quartus II 中用原理圖方式實(shí)現(xiàn)全加器,并用 Qua

2022-01-17 11:27:36 6

6 的,特別是在短的中等碼長(zhǎng)下,性能接近香農(nóng)限。本文是基于課題的要求,在Quartus II軟件中通過(guò)調(diào)用IP核的方式實(shí)現(xiàn)RS編譯碼過(guò)程,并通過(guò)Modelsim進(jìn)行仿真驗(yàn)證。

2022-09-28 10:02:21 2

2 首先安裝Quartus II 13.0軟件再用Quartus_II_13.0_x64破解器.exe破解

2022-12-21 17:27:08 18

18

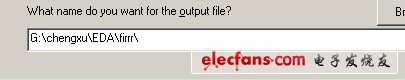

寫(xiě)上自己想要的文件名字,

寫(xiě)上自己想要的文件名字, 然后next。后出現(xiàn)這樣的菜單欄。如下圖

然后next。后出現(xiàn)這樣的菜單欄。如下圖

設(shè)置參數(shù)啊,

設(shè)置參數(shù)啊, 生成仿真文件啊

生成仿真文件啊 完成啊。

完成啊。 電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論