可編程邏輯器件的兩種類(lèi)型是現(xiàn)場(chǎng)可編程門(mén)陣列(FPGA)和復(fù)雜可編程邏輯器件(CPLD)。在這兩類(lèi)可編程邏輯器件中,F(xiàn)PGA是在PAL、GAL、EPLD等可編程器件的基礎(chǔ)上進(jìn)一步發(fā)展的產(chǎn)物。

2016-01-04 17:55:08 1404

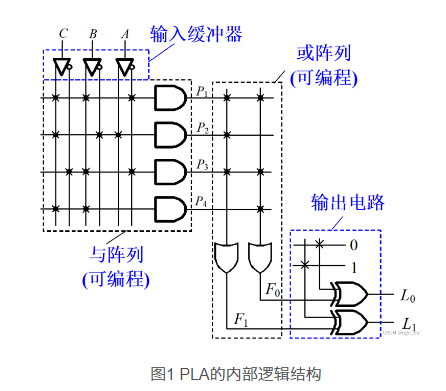

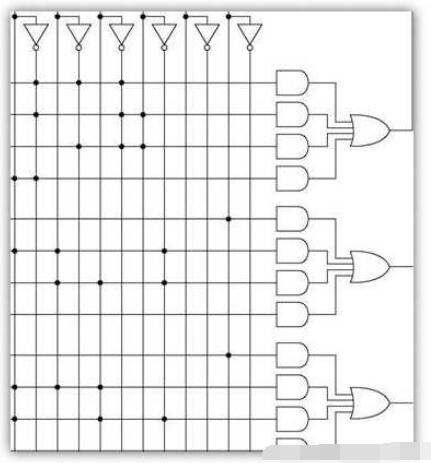

1404 可編程邏輯陣列(Programmable Logic Array,PLA)和可編程陣列邏輯(Programmable Array Logic,PAL)都是數(shù)字邏輯電路中常見(jiàn)的可編程邏輯設(shè)備,但它們有一些根本上的區(qū)別。

2024-02-02 11:41:30 353

353

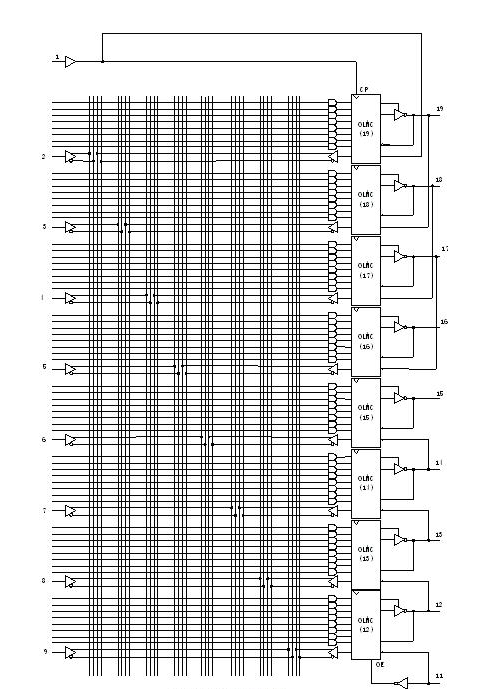

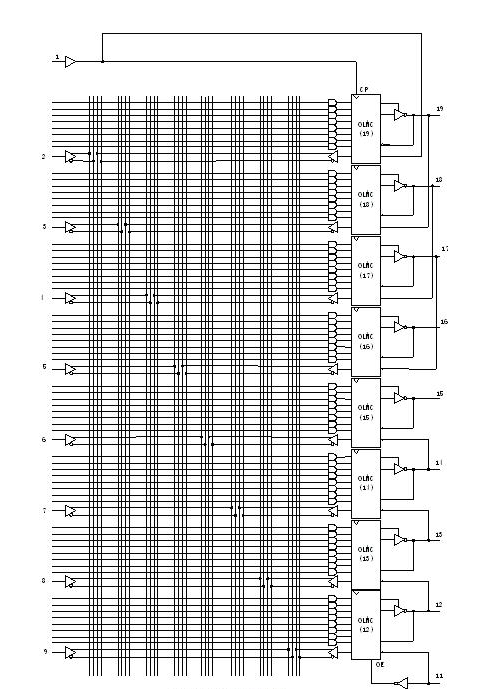

通用陣列邏輯(GAL)是一種可編程邏輯器件,由Lattice公司在PAL(可編程陣列邏輯)的基礎(chǔ)上設(shè)計(jì)出來(lái)。GAL采用可編程的輸出邏輯宏單元OLMC(Output Logic Macro Cell)結(jié)構(gòu),使得電路的邏輯設(shè)計(jì)更加靈活。

2024-02-02 12:21:12 274

274

GAL16V8D-15LD是什么芯片,是不是可編程芯片,誰(shuí)有GAL16V8D-15LD的中文資料,

2011-10-23 17:24:34

這個(gè)章節(jié)包含了定義邏輯單元 (LE) 和邏輯陣列模塊 (LAB) 的特性。具體信息體現(xiàn)在 LE如何運(yùn)作,LAB 如何容納 LE 組,以及 LAB 接口如何與 Cyclone? IV 器件中的其他模塊連接。

2017-11-13 11:25:48

FPGA/SOPC開(kāi)發(fā)教程FPGA(現(xiàn)場(chǎng)可編程門(mén)陣列)與 CPLD(復(fù)雜可編程邏輯器件)都是可編程邏輯器件,它們是在 PAL,GAL 等邏輯器件的基礎(chǔ)之上發(fā)展起來(lái)的。同以往的 PAL,GAL 等

2009-03-28 14:57:08

(06)FPGA資源評(píng)估1.1 目錄1)目錄2)FPGA簡(jiǎn)介3)Verilog HDL簡(jiǎn)介4)FPGA資源評(píng)估5)結(jié)語(yǔ)1.2 FPGA簡(jiǎn)介FPGA(Field Programmable Gate

2022-02-23 06:31:32

/sinat_41653350/article/details/105736117---這個(gè)里面有FPGA硬件資源介紹。FPGA簡(jiǎn)介 FPGA(Field-Programmable Gate Array), 即現(xiàn)場(chǎng)可編程門(mén)陣列,它是在PAL、GAL、CPLD等可編程器件的基礎(chǔ)上進(jìn)一步發(fā)展的產(chǎn)物。它是作為專(zhuān)用集成..

2021-07-26 07:09:37

函數(shù)功能) CPLD(Complex Programmable Logic Device 復(fù)雜可編程邏輯器件,內(nèi)部結(jié)構(gòu)為“與或陣列”。該結(jié)構(gòu)來(lái)自于典型的PAL、GAL器件的結(jié)構(gòu)。任意一個(gè)組合邏輯都可以

2020-07-16 10:46:21

Device復(fù)雜可編程邏輯器件 FPGA: Field-Programmable Gate Array現(xiàn)場(chǎng)可編程門(mén)陣列 GAL:Generic Array Logic通用陣列邏輯 PLA

2017-11-28 08:44:43

(10)FPGA跨時(shí)鐘域處理1.1 目錄1)目錄2)FPGA簡(jiǎn)介3)Verilog HDL簡(jiǎn)介4)FPGA跨時(shí)鐘域處理5)結(jié)語(yǔ)1.2 FPGA簡(jiǎn)介FPGA(Field Programmable

2022-02-23 07:47:50

部分。現(xiàn)場(chǎng)可編程門(mén)陣列(FPGA)是可編程器件,與傳統(tǒng)邏輯電路和門(mén)陣列(如PAL,GAL及CPLD器件)相比,F(xiàn)PGA具有不同的結(jié)構(gòu)。FPGA利用小型查找表(16×1RAM)來(lái)實(shí)現(xiàn)組合邏輯,每個(gè)查找表

2023-02-23 15:24:55

以上氣缸或者其他流程,難上加]難,不如PLC,這里我們糾正一下。PLC不是labview不能統(tǒng)一一類(lèi),一個(gè)是軟件一個(gè)是硬件。下面我們labview開(kāi)發(fā)一款可以替代PLC邏輯控制 配置即用 的通用邏輯

2020-06-17 09:39:35

PLD可編程邏輯器件 英文全稱(chēng)為:programmable logic device 即 PLD。PLD是做為一種通用集成電路產(chǎn)生的,他的邏輯功能按照用戶(hù)對(duì)器件編程來(lái)確定。一般的PLD的集成度很高

2021-07-22 09:05:48

產(chǎn)生新一代器件,其結(jié)構(gòu)與PAL一樣,也是由一個(gè)可編程的“與”門(mén)陣列去驅(qū)動(dòng)一個(gè)固定的“或”門(mén)陣列,但它的輸出單元的結(jié)構(gòu)完全不同。GAL器件的每個(gè)輸出引腳都接有一個(gè)輸出邏輯宏單元(OLMC),這些宏單元可由

2019-03-06 10:19:07

本篇將分為如下幾個(gè)部分:1.1 STM32 通用定時(shí)器簡(jiǎn)介1.2 硬件設(shè)計(jì)1.3 軟件設(shè)計(jì)1.4 下載驗(yàn)證1.1 STM32 通用定時(shí)器簡(jiǎn)介STM32 的通用定時(shí)器是一個(gè)通過(guò)可編程預(yù)分頻器(PSC

2021-08-12 07:13:39

1. 通用定時(shí)器簡(jiǎn)介STM32F4的通用定時(shí)器包括TIME2-TIME5,TIME9-TIME14共10個(gè)。 通用定時(shí)器可以被用于:定時(shí)中斷、測(cè)量數(shù)量信號(hào)的脈沖長(zhǎng)度(輸入捕獲)、輸出波形(PWM)等

2021-08-16 06:36:38

以下描述適用于整個(gè)STM32FM10xxx系列。本文依據(jù)《STM32中文參考手冊(cè)_V10》STM32通用定時(shí)器簡(jiǎn)介STM32 的通用定時(shí)器是一個(gè)通過(guò)可編程預(yù)分頻器(PSC)驅(qū)動(dòng)的 16 位自動(dòng)裝載

2021-08-11 07:02:10

通用TIMx簡(jiǎn)介通用定時(shí)器(TIM2、TIM3、TIM4和TIM5)是一個(gè)通過(guò)可編程預(yù)分頻器驅(qū)動(dòng)的16位自動(dòng)裝載計(jì)數(shù)器構(gòu)成。通用TIMx主要功能通用TIMx定時(shí)器功能包括:● 16位向上、向下、向上

2021-08-18 08:16:38

組成,而任意一個(gè)組合邏輯都可以用“與一或”表達(dá)式來(lái)描述,所以, PLD能以乘積和的形式完成大量的組合邏輯功能。這一階段的產(chǎn)品主要有PAL(可編程陣列邏輯)和GAL(通用陣列邏輯)。PAL由一個(gè)可編程

2012-02-27 11:52:00

(Interconnect)三個(gè)部分。 現(xiàn)場(chǎng)可編程門(mén)陣列(FPGA)是可編程器件,與傳統(tǒng)邏輯電路和 門(mén)陣列(如PAL,GAL及CPLD器件)相比,F(xiàn)PGA具有不同的結(jié)構(gòu)。FPGA利用小型查找表(16×1RAM

2019-08-11 04:30:00

什么是FPGA?FPGA是Field Programmable Gate Array的縮寫(xiě),即現(xiàn)場(chǎng)可編程門(mén)陣列,它是在PAL、GAL、EPLD等可編程器件的基礎(chǔ)上進(jìn)一步發(fā)展的產(chǎn)物。它是作為

2021-11-03 08:10:47

描述Commodore 8296 - 使用 ONE GAL 22v10 替換 UE5大多數(shù)有缺陷的 Commodore 8296 計(jì)算機(jī)都存在 PLA 芯片(UE5 和/或 UE6)的問(wèn)題。更換

2022-06-30 07:02:41

原文鏈接1原文鏈接2fpga簡(jiǎn)介FPGA(Field-Programmable Gate Array), 即現(xiàn)場(chǎng)可編程門(mén)陣列,它是在PAL(可編程陣列邏輯)、GAL(通用陣列邏輯器件)、CPL(復(fù)雜

2022-01-25 08:13:59

`<p><font face="Verdana">可編程通用陣列邏輯GAL器件介紹<

2009-09-29 10:25:21

什么是可編程邏輯? 在數(shù)字電子系統(tǒng)領(lǐng)域,存在三種基本的器件類(lèi)型:存儲(chǔ)器、微處理器和邏輯器件。存儲(chǔ)器用來(lái)存儲(chǔ)隨機(jī)信息,如數(shù)據(jù)表或數(shù)據(jù)庫(kù)的內(nèi)容。微處理器執(zhí)行軟件指令來(lái)完成范圍廣泛的任務(wù),如運(yùn)行字處理

2019-07-10 08:16:49

可編程邏輯陣列fpga和cpld

2023-09-20 07:58:59

介紹了利用現(xiàn)場(chǎng)可編程邏輯門(mén)陣列FPGA實(shí)現(xiàn)直接數(shù)字頻率合成(DDS)的原理、電路結(jié)構(gòu)和優(yōu)化方法。重點(diǎn)介紹了DDS技術(shù)在FPGA中的實(shí)現(xiàn)方法,給出了采用ALTERA公司的ACEX系列FPGA芯片EP1K30TC進(jìn)行直接數(shù)字頻率合成的VHDL源程序。

2021-04-30 06:29:00

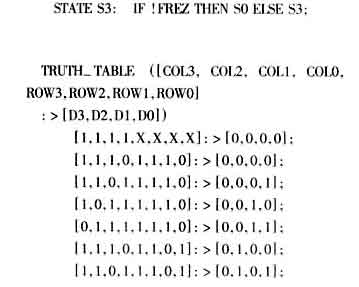

本文采用基于GAL 芯片實(shí)現(xiàn)VME 總線接口電路的思路,對(duì)VME 總線接口設(shè)計(jì)問(wèn)題進(jìn)行了深入研究。文中通過(guò)軟件技術(shù)實(shí)現(xiàn)了VME 總線地址的譯碼以及數(shù) 據(jù)讀寫(xiě)與中斷邏輯控制,有效簡(jiǎn)化了硬件電路的設(shè)計(jì)。

2021-05-28 06:39:41

早起的GAL20V8這種器件,用什么軟件開(kāi)發(fā)好?用XILINX ISE可以嗎?

2015-08-27 15:57:34

小弟對(duì)邏輯控制器件不熟,供應(yīng)商說(shuō)GAL16V8D要停產(chǎn)了,請(qǐng)熟悉邏輯器件的兄弟幫忙提供一款類(lèi)似的芯片。謝謝!

2017-06-13 08:41:07

陣列比較器都沒(méi)什么問(wèn)題 現(xiàn)在主要是sar邏輯很模糊,希望誰(shuí)可以推薦sar 邏輯的教程啊?

2021-06-24 07:47:52

【產(chǎn)品簡(jiǎn)介】高端邏輯分析儀產(chǎn)品簡(jiǎn)介(簡(jiǎn)版英文)

2022-10-17 07:08:32

基于GAL器件的步進(jìn)電機(jī)控制器的研究與設(shè)計(jì)

采用GAL控制脈沖分配的邏輯設(shè)計(jì)若采用集成電路芯片來(lái)實(shí)現(xiàn)三相六拍步進(jìn)電機(jī)的控制,所用器件較多! 電路一般比較復(fù)雜# 為

2008-10-21 01:53:23 42

42 9.1? 通用可編程邏輯器件GAL9.2? ABEL-HDL硬件描述語(yǔ)言9.3? 開(kāi)發(fā)軟件ISP Synario操作簡(jiǎn)介9.4 可編程邏輯器件CPLD/FPGA9.5? MAX+PLUSII開(kāi)發(fā)軟件邏輯器件,即可用來(lái)實(shí)

2009-01-21 14:47:56 123

123 本文利用陳列邏輯器件GAL16V8對(duì)步進(jìn)電機(jī)實(shí)現(xiàn)控制,給出了89C55單片機(jī)控制的硬件、軟件設(shè)計(jì)實(shí)例。

2009-04-02 16:30:16 200

200 通用陣列邏輯GAL實(shí)現(xiàn)基本門(mén)電路的設(shè)計(jì)一、實(shí)驗(yàn)?zāi)康?.了解GAL22V10的結(jié)構(gòu)及其應(yīng)用;2.掌握GAL器件的設(shè)計(jì)原則和一般格式;3.學(xué)會(huì)使用VHDL語(yǔ)言進(jìn)行可編程邏輯器件的邏輯設(shè)

2009-06-28 00:12:19 135

135 GAL編譯工具(Atmel提供):4.8a版本,可用于Win98/NT/2K

2009-10-12 09:58:44 101

101 采用EEPROM 工藝設(shè)計(jì)通用陣列邏輯器件——遇到的問(wèn)題與解決方案深圳市國(guó)微電子股份有限公司 裴國(guó)旭電可擦除只讀存儲(chǔ)器(EEPROM)工藝可廣泛運(yùn)用于各種消費(fèi)產(chǎn)品中,像微

2009-12-14 11:41:35 51

51 GAL編譯工具

Atmel提供的GAL編譯工具 4.8a版本

2010-04-14 15:42:06 83

83 以GAL16V8為例介紹了一種對(duì)可編程邏輯器件邏輯功能的測(cè)試方法,其中硬件接口電路采用了增強(qiáng)型并行口,使傳統(tǒng)的并行口具有高速雙向數(shù)據(jù)傳輸?shù)哪芰ΑS捎?b class="flag-6" style="color: red">GAL16V8中設(shè)計(jì)了加密位,

2010-08-06 16:05:18 0

0 GAL(generic array logic)是美國(guó)晶格半導(dǎo)體公司(gem 0udu or)最新推出的可電擦寫(xiě)、可重復(fù)編程、可加密的一種可編程邏輯器件(PLD)。這是第二代PAL, 亦是目前最理想的可多次編程的

2010-08-16 15:59:20 61

61 本文提出j以通用陣列邏輯器件GAL和只讀存貯器EPROM 為核心器件.設(shè)計(jì)測(cè)量顯示控制裝置的方法。配以數(shù)字式傳感器及用最小二乘法編制的曲線自動(dòng)分段椒合程序生成的EPR

2010-10-11 11:12:30 25

25 基于光伏模塊直流物理模型在matlab 仿真環(huán)境下開(kāi)發(fā)了光伏陣列通用仿真模型利用該模型可以模擬任意太陽(yáng)輻射強(qiáng)度環(huán)境溫度光伏模塊參數(shù)光伏陣列串并聯(lián)方式組合下的光伏陣

2010-10-21 16:00:05 0

0 摘要:介紹了利用可編程邏輯陣列把1路RS232擴(kuò)展至4路RS422的串行口電路設(shè)計(jì)方法。該擴(kuò)展電路不占用PC系統(tǒng)資源,同時(shí)具有結(jié)構(gòu)簡(jiǎn)單,使用方便,通用性和可補(bǔ)性

2006-03-24 12:58:58 1206

1206

FPGA是英文Field Programmable Gate Array的縮寫(xiě),即現(xiàn)場(chǎng)可編程門(mén)陣列,它是在PAL、GAL、EPLD等可編程器件的

2006-04-17 20:48:08 2594

2594 什么是邏輯驅(qū)動(dòng)器

邏輯驅(qū)動(dòng)器(Logical Drive)是陣列中的虛擬驅(qū)動(dòng)器,它可以占用一個(gè)以上的物理磁盤(pán)。

邏輯驅(qū)動(dòng)器把陣列或跨越陣列中的磁盤(pán)分

2009-01-19 23:25:11 9190

9190 【摘 要】 介紹了可編程邏輯器件的結(jié)構(gòu)、優(yōu)點(diǎn),及其在一種高準(zhǔn)確度A/D轉(zhuǎn)換器中的應(yīng)用。設(shè)計(jì)中采用了通用陣列邏輯芯片GAL16V8。

2009-05-15 22:30:08 781

781

摘要: 介紹了利用陣列邏輯器件GAL16V8對(duì)三相六拍步進(jìn)電機(jī)實(shí)現(xiàn)控制的方法及其電路設(shè)計(jì)。通過(guò)計(jì)算機(jī)編程器對(duì)GAL進(jìn)行編程,可以滿(mǎn)足各種控制要求。該電路簡(jiǎn)單,

2009-06-20 14:55:07 1093

1093

硬盤(pán)邏輯結(jié)構(gòu)簡(jiǎn)介

一. 硬盤(pán)邏輯結(jié)構(gòu)簡(jiǎn)介

1. 硬盤(pán)參數(shù)釋疑到目前為止, 人們常說(shuō)的硬盤(pán)參數(shù)還是古

2009-10-11 12:15:40 1559

1559

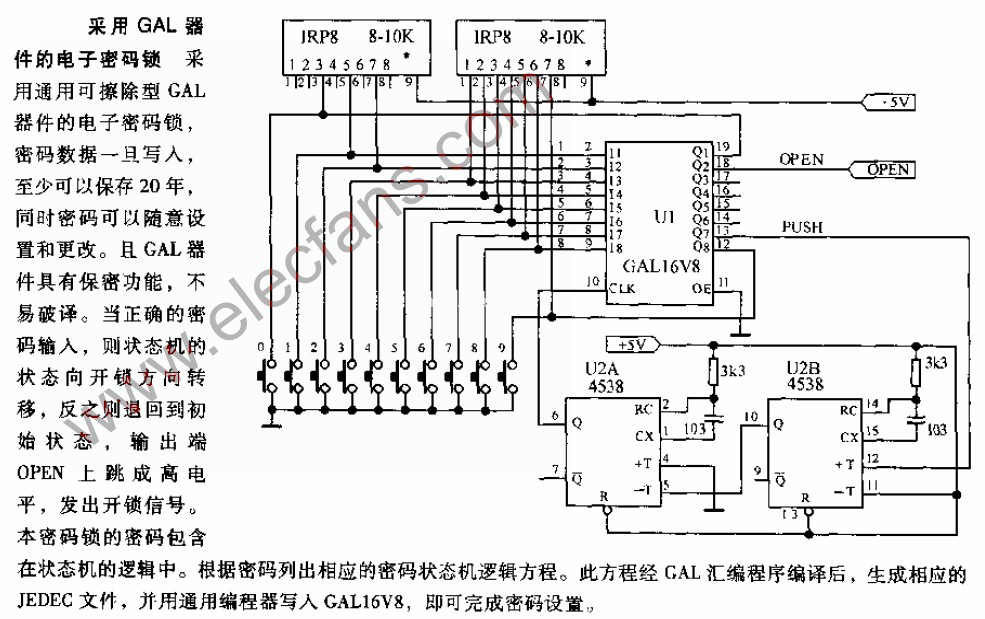

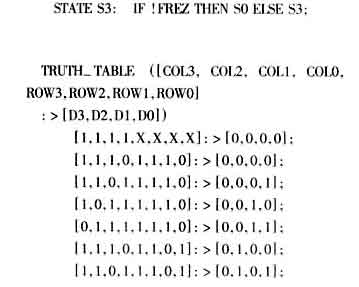

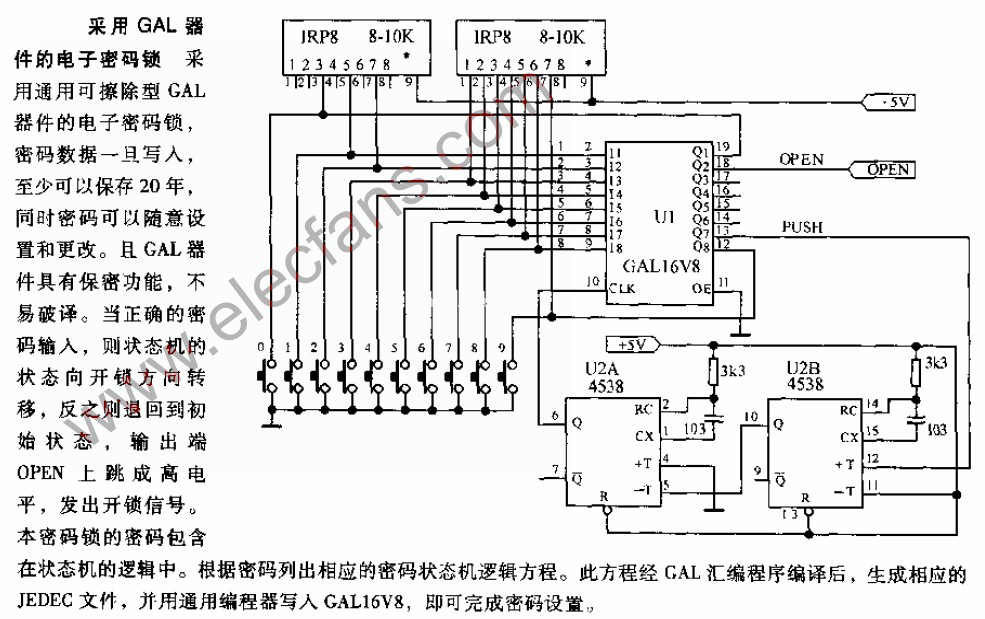

采用GAL器件的電子密碼鎖電路圖

采用通用可擦除型GAL器件的電子密碼鎖,密碼數(shù)據(jù)一旦寫(xiě)入,至少可以保存20年,同時(shí)密碼可以隨意

2009-11-17 22:41:13 988

988

二極管陣列檢測(cè)器簡(jiǎn)介

二極管陣列檢測(cè)器(diode-array detector, DAD): 以光電二極管陣列(或CCD陣列,硅靶攝像管等)作為

2009-11-24 08:53:45 2507

2507 各種邏輯電路簡(jiǎn)介

邏輯電路:

以二進(jìn)制為原理、實(shí)現(xiàn)數(shù)字信號(hào)邏輯運(yùn)算和操作的電路。分組合邏輯電路和

2009-11-24 13:27:04 2959

2959 常用邏輯門(mén)及其符號(hào)簡(jiǎn)介

2009-12-03 10:59:42 62570

62570 LogicLock邏輯鎖定簡(jiǎn)介

本節(jié)介紹Quartus的一個(gè)工具LogicLock,會(huì)在后面的實(shí)例里面介紹LogicLock的具體使用。

邏輯鎖定方法學(xué)邏輯鎖定方法學(xué)(LogicLock Methodology

2010-02-08 14:39:46 1971

1971 邏輯加密卡,邏輯加密卡是什么意思

邏輯加密存儲(chǔ)卡(Smart Card With Security Logic)主要是由EEPROM存儲(chǔ)單元陣列和密碼控制邏輯單元所構(gòu)成。

2010-04-02 13:35:45 4685

4685 什么是陣列邏輯電路

陣列邏輯電路的特點(diǎn): 邏輯元件在硅片上以陣列形式排列,芯片面積小、用戶(hù)自編程、設(shè)計(jì)方便。 典型的陣列

2010-04-15 13:43:17 3714

3714 1 GAL6002芯片簡(jiǎn)介

GAL6002是Lattice公司研制的電可擦除、可重復(fù)編程的高性能PLD器件,圖1所示是其引腳排列。GAL6002具有78×64×36 FPLA結(jié)構(gòu),可提供78×64的可編程與陣列和6

2010-08-30 18:10:00 3287

3287

可編程陣列邏輯(Programmable Array Logic)

可編程陣列邏輯(PAL)是一種與項(xiàng)可編程、或項(xiàng)固定結(jié)構(gòu)的可編程結(jié)構(gòu),為能方便實(shí)現(xiàn)各種邏輯功能,其輸出結(jié)構(gòu)通常

2010-09-18 09:13:11 1788

1788 1986年以來(lái),通用可重編程邏輯陣列(GAL)器件幾乎風(fēng)靡整個(gè)可編程邏輯器件(PLD)市

2011-02-18 13:27:50 328

328 本文給出了用可編程邏輯器件GAL配合ISA總線模擬I2C總線時(shí)序來(lái)對(duì)FI1256 MK2進(jìn)行控制的方法。該方法與PCI總線進(jìn)行模擬的方法相類(lèi)似。

2012-03-27 11:33:15 2687

2687

電子發(fā)燒友網(wǎng)核心提示: PAL有很多種不同的意思,但是在電子行業(yè)中指的是可編程陣列邏輯(Programmable Array Logic),是簡(jiǎn)單PLD其中的一種。電子發(fā)燒友網(wǎng)小編帶大家一起來(lái)深入了解什么

2012-10-12 14:02:11 4760

4760 電子發(fā)燒友網(wǎng)核心提示 :可編程陣列邏輯(PAL)是一種簡(jiǎn)單的PLD。本文由電子發(fā)燒友網(wǎng)小編給大家介紹PAL的輸出結(jié)構(gòu)以及PAL器件的命名規(guī)則。 1.PAL的輸出結(jié)構(gòu) 可編程陣列邏輯(PAL)是

2012-10-12 15:06:15 6374

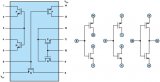

6374 電子發(fā)燒友網(wǎng)核心提示 :PLA,ProgrammableLogicArray的簡(jiǎn)稱(chēng),意為可編程邏輯陣列。本文將著重介紹可編程邏輯陣列PLA的一些基本概念、類(lèi)型以及基礎(chǔ)應(yīng)用。 一 . PLA的基本概念 可編程邏輯陣

2012-10-12 16:01:15 17896

17896 電子發(fā)燒友網(wǎng)核心提示 :本文主要介紹通用陣列邏輯GAL的優(yōu)缺點(diǎn)。 1. GAL器件的 優(yōu)點(diǎn) GAL是繼PAL之后具有較高性能的PLD,和 PAL相比,具有以下優(yōu)點(diǎn): (1) 有較高的通用性和靈活性:它

2012-10-12 16:36:13 4181

4181 可編程邏輯器件簡(jiǎn)介,相關(guān)詳細(xì)學(xué)習(xí)。

2016-04-26 16:55:36 0

0 GAL16

2017-03-04 17:50:19 4

4 現(xiàn)場(chǎng)可編程邏輯門(mén)陣列器件 FPGA原理及應(yīng)用設(shè)計(jì)

2017-09-19 11:26:26 17

17 Microchip公司本次講座將講:PIC? MCU全系列通用開(kāi)發(fā)板簡(jiǎn)介。

2018-06-06 01:45:00 4214

4214 FPGA,是Field Programmable Gate Array的簡(jiǎn)稱(chēng),中文名稱(chēng)為現(xiàn)場(chǎng)可編程門(mén)陣列,是一種可編程器件,是在PAL(可編程邏輯陣列)、GAL(通用陣列邏輯)、CPLD(復(fù)雜可編程邏輯器件)等傳統(tǒng)邏輯電路和門(mén)陣列的基礎(chǔ)上發(fā)展起來(lái)的一種半定制電路。

2019-09-18 17:51:38 49498

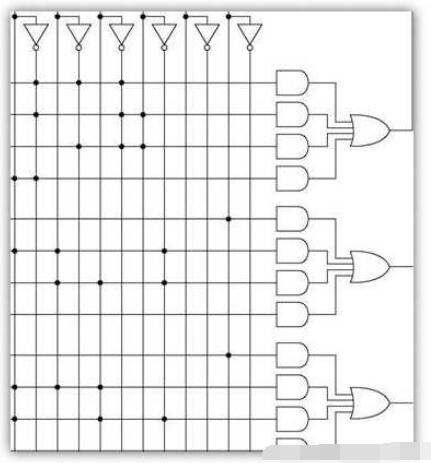

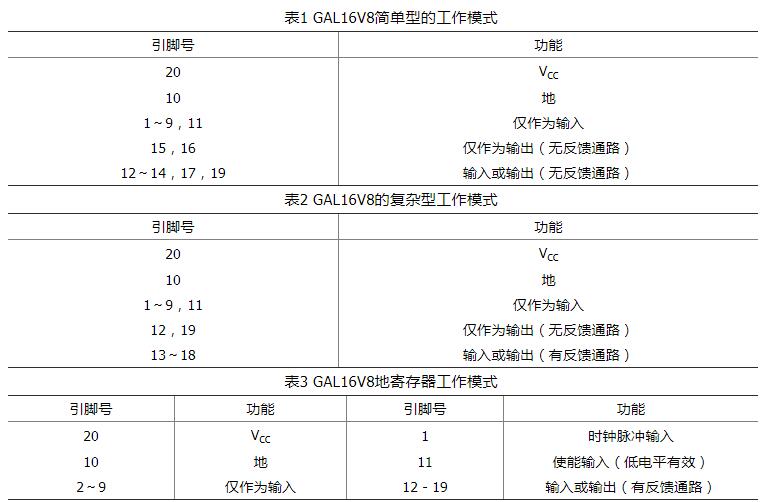

49498 根據(jù)GAL器件的門(mén)陣列結(jié)構(gòu),可以把現(xiàn)有的GAL器件分為兩大類(lèi):一類(lèi)與PAL器件基本相同,即與門(mén)陣列可編程,或門(mén)陣列固定連接,這類(lèi)器件有GAL16V8,ispGAL16Z8等;另一類(lèi)GAL器件的與門(mén)陣列和或門(mén)陣列都可編程,GAL39V18就屬于這類(lèi)器件。

2019-10-11 16:54:14 15725

15725

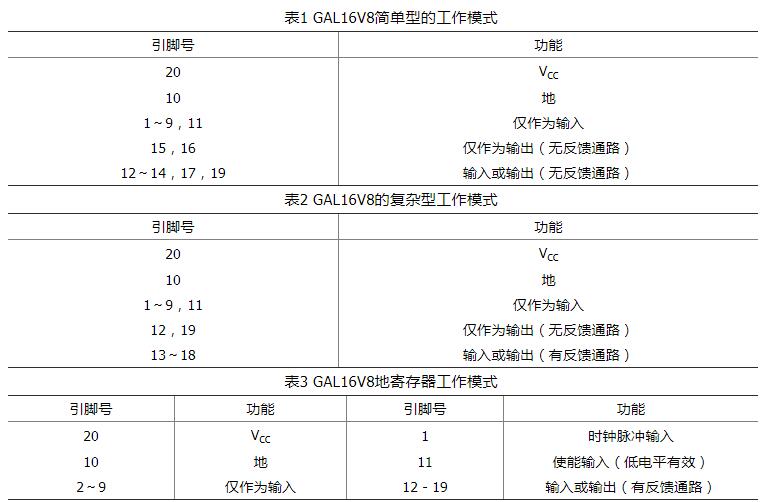

由于OLMC提供了靈活的輸出功能,因此編程后的GAL器件可以替代所有其他固定輸出極的PLD。GAL16V8有3種工作模式,即簡(jiǎn)單型、復(fù)雜型和寄存器型。適當(dāng)連接該器件的引腳線,由OLMC的輸出/輸入特性可以決定其工作模式。

2019-10-13 17:14:00 4384

4384

輸出和反響構(gòu)造由可編程的與陣列和固定的或陣列構(gòu)成,沒(méi)有輸出反響信號(hào),輸入和輸出引出端是固定的,不能由用戶(hù)自行界說(shuō)。只適用于簡(jiǎn)略的組合邏輯電路方案。

2020-06-19 09:07:40 2384

2384

輸出邏輯宏單元(OLMC)允許用戶(hù)來(lái)構(gòu)建,這種通用的結(jié)構(gòu)提供了最大的設(shè)計(jì)靈活性。作為 GAL16V8的許多可能結(jié)構(gòu)形式中最重要的一個(gè)子集,PAL結(jié)構(gòu)被列在宏單元描述部分的表里面。 GAL16V8借助于全部功能/ 熔絲圖/參數(shù)的兼容性能夠仿真任何一種PAL結(jié)構(gòu)。

2020-07-09 08:00:00 18

18 GAL(Generic Array Logic, GAL,通用數(shù)組邏輯)以PAL(可編程數(shù)組邏輯,PLD的一種)為基礎(chǔ),此是由萊迪思半導(dǎo)體公司所發(fā)明,GAL的特性與PAL相同,不過(guò)PAL的電路配置

2021-02-16 10:15:00 3996

3996 可編程邏輯陣列fpga和cpld說(shuō)明。

2021-03-30 09:30:05 25

25 通用TigerSHARC處理器產(chǎn)品簡(jiǎn)介

2021-05-26 19:50:49 8

8 原文鏈接1原文鏈接2fpga簡(jiǎn)介FPGA(Field-Programmable Gate Array), 即現(xiàn)場(chǎng)可編程門(mén)陣列,它是在PAL(可編程陣列邏輯)、GAL(通用陣列邏輯器件)、CPL(復(fù)雜

2021-12-01 10:51:05 7

7 現(xiàn)場(chǎng)可編程門(mén)陣列(Field Programmable Gate Array,F(xiàn)PGA)是在PAL、GAL、CPLD的基礎(chǔ)上產(chǎn)生的。它屬于一種半定制電路,與全定制電路相比,開(kāi)發(fā)成本較低,功能可擴(kuò)展,同時(shí)又提供了較多的邏輯單元。

2022-08-22 18:07:13 415

415 電子發(fā)燒友網(wǎng)站提供《高端邏輯分析儀產(chǎn)品簡(jiǎn)介(簡(jiǎn)版英文).pdf》資料免費(fèi)下載

2022-10-14 10:22:19 0

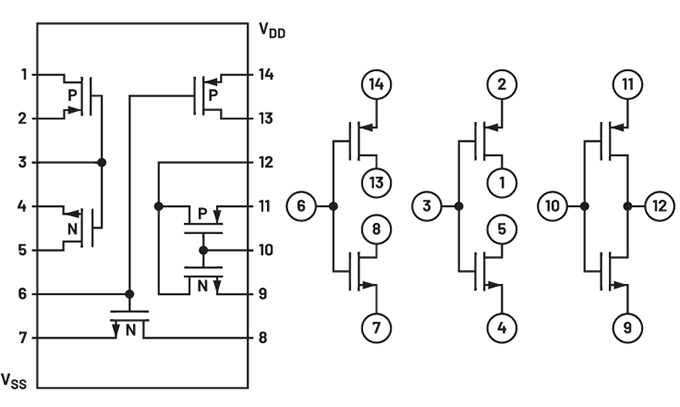

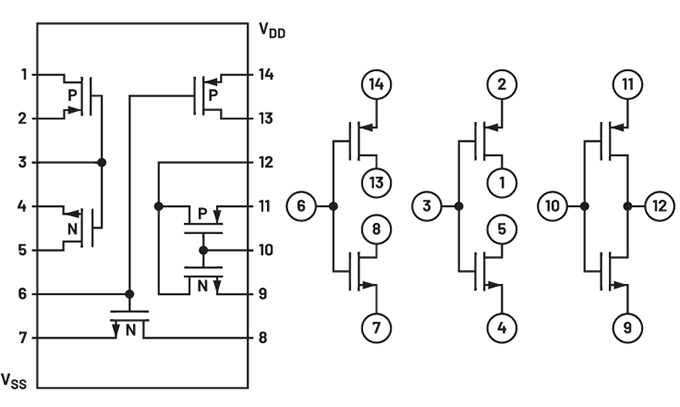

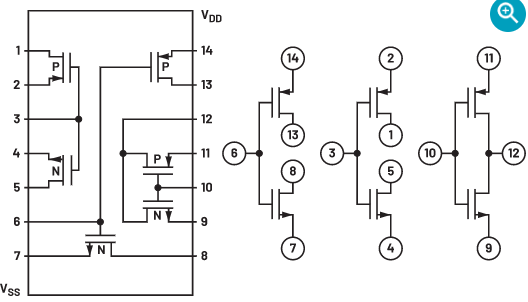

0 本實(shí)驗(yàn)活動(dòng)的目標(biāo)是使用CD4007晶體管陣列構(gòu)建各種CMOS邏輯功能。CD4007包含三對(duì)互補(bǔ)的NMOS和PMOS晶體管。

2022-11-02 17:25:20 2970

2970

FPGA是在PAL(可編程邏輯陣列)、GAL(通用陣列邏輯)、CPLD(復(fù)雜可編程邏輯器件)等傳統(tǒng)邏輯電路和門(mén)陣列的基礎(chǔ)上進(jìn)一步發(fā)展的產(chǎn)物。

2023-04-19 15:17:10 1246

1246 FPGA是在PAL(可編程邏輯陣列)、GAL(通用陣列邏輯)、CPLD(復(fù)雜可編程邏輯器件)等傳統(tǒng)邏輯電路和門(mén)陣列的基礎(chǔ)上進(jìn)一步發(fā)展的產(chǎn)物。它利用計(jì)算機(jī)輔助設(shè)計(jì),繪制出實(shí)現(xiàn)用戶(hù)要求的原理圖、編輯布爾方程或用硬件描述語(yǔ)言等方式作為設(shè)計(jì)輸入;

2023-04-20 09:20:35 2696

2696 本實(shí)驗(yàn)活動(dòng)的目標(biāo)是使用CD4007晶體管陣列構(gòu)建各種CMOS邏輯功能。CD4007包含三對(duì)互補(bǔ)的NMOS和PMOS晶體管。

2023-05-29 14:18:49 1082

1082

提出了一種僅在一個(gè)晶體管上制作的正負(fù)邏輯通用無(wú)源邏輯元件。邏輯元件至少有兩個(gè)輸入,以及三個(gè)輸出:一個(gè) OR、一個(gè) XOR 和一個(gè) AND,同時(shí)工作。給出了使用這種設(shè)備作為“只有兩個(gè)”邏輯元素的一部分以及 RS 觸發(fā)器的一部分的示例。

2023-06-10 17:11:00 811

811

(Prograrmable Logie Array, PIA)器件、可編程陣列邏輯(Prograrmable Array Logie, PAL)器件、通用陣列邏輯 ( Generic ArrayLogic, CAL)器件

2023-06-06 15:35:59 659

659

可編程邏輯器件 (Programmable Loeie Device,PLD)是一種用戶(hù)編程實(shí)現(xiàn)某種邏輯功能的邏輯器件,主要由可編程的與陣列、或陣列、門(mén)陣列等組成,可通過(guò)編程來(lái)實(shí)現(xiàn)一定的邏輯功能。

2023-06-06 15:37:45 405

405

XILINX FPGA簡(jiǎn)介-型號(hào)系列分類(lèi)參考

FPGA(Field Programmable Gate Array)是在PAL (可編程陣列邏輯)、GAL(通用陣列邏輯)等可編程器件的基礎(chǔ)上

2023-03-10 16:27:57 5185

5185

本實(shí)驗(yàn)活動(dòng)的目標(biāo)是進(jìn)一步強(qiáng)化上一個(gè)實(shí)驗(yàn)活動(dòng)“使用CD4007陣列構(gòu)建CMOS邏輯功能”中探討的CMOS邏輯基本原理,并獲取更多使用復(fù)雜CMOS門(mén)級(jí)電路的經(jīng)驗(yàn)。具體而言,您將了解如何使用CMOS傳輸門(mén)和CMOS反相器來(lái)構(gòu)建傳輸門(mén)異或(XOR)和異或非邏輯功能。

2023-07-10 10:12:41 1148

1148

通用邏輯門(mén)芯片?DIP-14封裝:DIP-14

2022-08-19 15:57:48 3

3 通用邏輯門(mén)芯片?SOP-14封裝:SOP-14

2022-08-19 15:57:48 1

1 在與邏輯陣列中,與邏輯門(mén)的輸入引腳通常通過(guò)開(kāi)關(guān)或編程連線與輸入信號(hào)相連接。而與邏輯陣列的點(diǎn)則是指它們與邏輯門(mén)輸入引腳的連接點(diǎn)。

2024-02-02 12:31:13 1083

1083 fpga芯片是什么芯片 FPGA芯片(Field Programmable Gate Array)即現(xiàn)場(chǎng)可編程邏輯門(mén)陣列,是一種特殊的邏輯芯片。它是在PAL(可編程邏輯陣列)、GAL(通用陣列邏輯

2024-03-14 17:25:24 169

169

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論