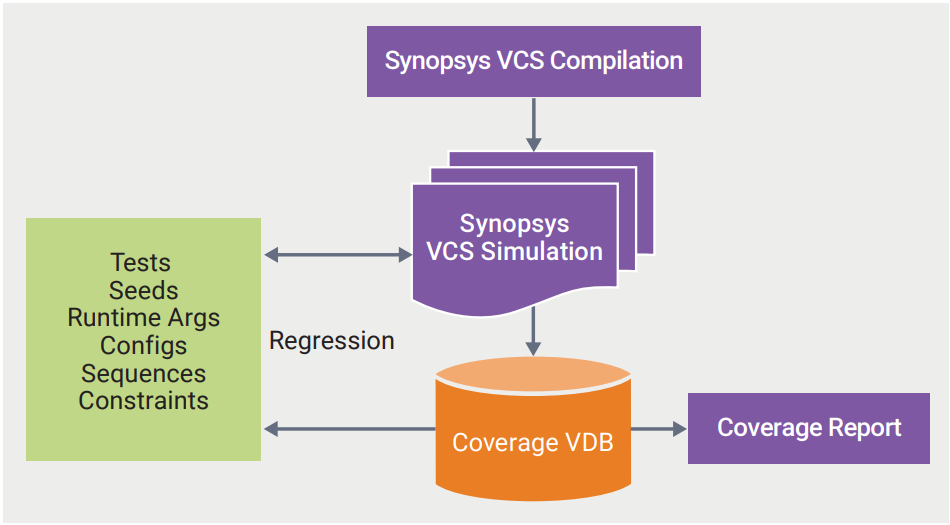

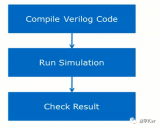

VCS是編譯型verilog仿真器,VCS先將verilog/systemverilog文件轉化為C文件,在linux下編譯生成的可執行文./simv即可得到仿真結果。

2023-10-25 17:22:28 491

491

6月初,AI賦能的 “電子哨兵”上崗深圳市南山區行政大廳,實現辦事人員健康數據核驗、體溫檢測、自動預約取號、授權調用電子證照等操作整合,避免多次掃碼、多次核驗的繁瑣。早在今年3月,深圳市已經在公交

2022-06-28 16:42:59

的使用數據里,ROOBO能夠根據使用頻次、使用時長、用戶粘性來判斷內容、功能的受歡迎程度,進而幫助企業優化出更受孩子喜愛的產品。

AI賦能教育 語言教學技能全面開花

除了技術實現外,童秘以內

2018-08-05 09:27:15

VCS是Synopsys公司的數字邏輯仿真工具,DVE是一個圖形界面,便于調試RTL代碼,查看波形。本視頻簡要介紹VCS的常用概念。 歡迎大家加入啟芯SoC QQ群: 275855756。共同交流和學習SoC芯片設計技術。

2013-10-04 13:07:00

be openedSource file "../../VCS/Extras.inc" cannot be opened for reading due to 'No such file

2014-03-26 11:24:08

VCS+Verdi如何安裝?怎么破解?

2021-06-21 06:11:03

VCS6-S5-S5 - DC/DC converter - CUI INC,

2022-11-04 17:22:44

VCS-verilog compiled simulator是synopsys公司的產品.其仿真速度相當快,而且支持多種調用方式;使用的步驟和modelsim類似,都要先做編譯,再調用仿真.Vcs

2011-12-15 10:27:10

ramb.v -->ISE map--> ISE netgen--->產生ramb_sim.vramb.v的INIT不全為零,vcs可以驗證ramb_sim.v的INIT正確嗎?我

2015-03-05 11:22:05

VCS破解過程中遇到的問題是什么?有什么解決的方法?

2021-06-21 08:10:58

VSO008N10MS

2023-03-29 17:19:43

vcs-mx是什么?vcs又是什么?vcs-mx和一般的vcs有什么區別?

2021-06-21 08:05:19

ASIC/SoC芯片設計驗證中常常使用Makefile來管理驗證環境,運行驗證案例。本視頻借用網絡上的一篇Makefile(Synopsys VCS)文件,簡要介紹了Makefile的基本語法和使用方法,并描述了數字系統驗證的流程。 啟芯SoC QQ群: 275855756

2013-10-03 19:01:52

REXROTH柱塞泵E-A10VSO100DR/31-PPA12N00 廠家訂貨德國力士樂REXROTH柱塞泵軸向柱塞泵(英文名:Piston pump)是活塞或柱塞的往復運動方向與缸體中心軸平行

2018-07-30 18:06:23

為什么verilog可以描述硬件?在SOC設計中使用verilog,和FPGA為對象使用verilog,有什么區別?SOC流程和FPGA流程的不同之處在哪里?

2021-06-21 07:02:59

STM32Wx 賦能工業物聯網解決方案, 陳列了STM32 MCU 及 MPU 產品組合、STM32Wx 無線產品、2.4GHz 產品系列、Sub-GHz 產品系列等。

2023-09-05 06:06:57

ZWS-CAN智慧云如何賦能工程機械?ZWS-CAN智慧云系統演示

2021-03-01 07:49:34

nanosim和vcs為什么可以聯合起來進行數字模擬混合仿真?nanosim和vcs混合仿真的過程是怎樣的?

2021-06-18 08:28:30

、工業優化、航空調度等全局能力為一體的ET大腦,將人工智能賦能于生活中的各處場景。阿里云解決方案總經理劉澍泉在主題為《云轉型之路》的演講中講到,人工智能已經進入到產業化的階段,我們可以看到,人工智能

2018-01-09 15:12:20

能夠表現出與人類相類似的智慧行為,包括學習、記憶及預測(推論)的思考能力,以及模擬人類感官識別和動作行為等。6.【AI學習】第3篇--人工神經網絡簡介:本篇主要介紹:人工神經網絡的起源、簡單神經網絡

2020-11-05 17:55:48

包含有DIN且使用Skey進行TEA加密的注冊確認包傳送到服務器,服務器解密驗證通過后返回響應包,并且把注冊設備的PN碼、注冊狀態等更新到數據庫。CC3200與服務器間的通信協議為TLV結構的協議,即報文類型+長度+值(內容)。具體參見AI設備通信協議文檔。文件下載請點擊:

2022-08-31 16:35:59

項目名稱:AI功能攝像機驗證試用計劃:申請理由:1,公司智能攝像頭技術驗證。2,測試華為系統的分布式總線功能,為通用物聯網技術做技術積累。計劃:第1周學習華為操作系統。第2周驗證攝像頭人形識別。預計結果:實現一套偏遠地區無線低功耗iA監視區域人入侵報警攝像頭。未來計劃:加入車形,車速,車牌檢測

2020-11-20 18:35:02

Camera HarmonyOS 鴻蒙OS開發板首先介紹一下,我叫abner,本科湖北工業大學,碩士在合肥工業大學,參與導師國家級重大科研項目。現在供職于上海**智能科技有限公司,現在項目主要做AI賦能toB

2020-11-18 18:15:42

芯片內嵌SOC子系統的規格制定;嚴格遵循開發流程、模板、標準和規范,完成芯片內嵌子系統的設計,驗證,測試,優化等工作,確保電路設計滿足規格要求,以芯片最后交付為目標。2、及時編寫各種SOC文檔和標準化

2020-02-29 11:06:28

8月25日晚上19點,知識賦能第七期第三節直播 《OpenHarmony知識賦能-WiFi掃描儀實現》 ,在OpenHarmony開發者成長計劃社群內成功舉行。本節直播為OpenHarmony知識賦

2022-08-26 14:36:33

【直播回顧】OpenHarmony知識賦能六期第五課—WiFi子系統8月11日晚上19點,知識賦能第六期第五節直播 《OpenHarmony知識賦能-WiFi子系統》 ,在OpenHarmony

2022-08-12 17:59:53

分享介紹ArkUI整體框架、ArkUI和其他子系統的關聯、布局渲染流程以及后續的課程規劃,希望能給廣大開發者一些啟發,更好的開啟學習之路。二、知識賦能第八期第2課:ArkUI自定義組件鏈接:https

2022-10-10 15:58:16

一個unsigned int數據能直接賦給SBUF嗎(如unsigned int a;SBUF=a;),如果不能,有什么方法可以實現,希望各位高手給指點下

2012-07-18 08:14:29

中國智能產業高峰論壇(CIIS 2020)在嘉興南湖舉辦。在11月15日舉辦的智能駕駛產業專題論壇上,中汽創智科技有限公司首席人工智能官丁華杰先生為我們帶來了題為《AI賦能自動駕駛的幾點思考》的精彩

2021-07-27 06:14:59

作為物理世界和數字世界之間的接口,傳感器和換能器已經從技術上的波瀾不驚轉變成為汽車安全、安防、醫療保健、物聯網(IoT)和人工智能(AI)等應用賦能的前沿技術。因此,它們在尺寸、功耗和靈敏度等基本物

2020-05-19 08:12:53

職位描述:1.負責我司數據通信產品的FPGA和ASIC應用的仿真驗證工作; 2.著重負責仿真驗證平臺系統的搭建和仿真驗證方法的引進; 3.編寫各種設計文檔和標準化資料,實現資源、經驗共享。 任職要求

2015-07-16 11:04:49

在4.25OpenHarmony 技術日生態論壇上,華秋電子副總經理曾海銀從華秋OpenHarmony 生態貢獻、華秋OpenHarmony 生態賦能案例、華秋供應鏈商業賦能計劃解決方案三大方

2022-05-13 12:17:00

模型、設計實例(instantiation)以及驗證流程。 組件模型 當制作以硅為目標的組件模型時,對于細節組件行為對照驗證系統正確作業所需的時間的取舍需謹慎為之。這在PLD架構的模擬組件中尤其重要

2011-10-16 22:55:10

代碼使用為例,進行VCS使用說明。簡要說明下該串口功能。該串口工作在波特率為115200,無奇偶檢驗位。一位停止位。當使能信號有效,就將8位數據發送出去,輸出結束后,在將該數據讀回來。即自發自收。測試

2022-07-18 16:18:48

在即將開展的“中國移動全球合作伙伴大會”上,華為將發布一款面向運營商電信領域的一站式AI開發平臺——SoftCOM AI平臺,幫助電信領域開發者解決AI開發在數據準備、模型訓練、模型發布以及部署驗證

2021-02-25 06:53:41

2021年12月,OpenAtom OpenHarmony(以下簡稱”OpenHarmony“)開源開發者成長計劃開啟了第一節OpenHarmony知識賦能直播課程,給廣大開發者搭建了一個專業的學習

2023-04-17 11:18:05

決方案的過程中,創建所需文化和組織運作轉變的計劃;創建創新生態系統的計劃,該生態系統應是新業務的一個組成部分,以預見并向新業務和聯合客戶提供新的智能服務。由AI技術賦能的人機界面(HMI)。對數據的誤解

2019-05-06 16:46:05

Mentor公司的Modelsim,Synopsys的VCS,還有Cadence的NC-Verilog均可以對RTL級的代碼進行設計驗證?(使用Cadence或Modelsim或Synopsys的VCS等軟件

2020-02-12 16:09:48

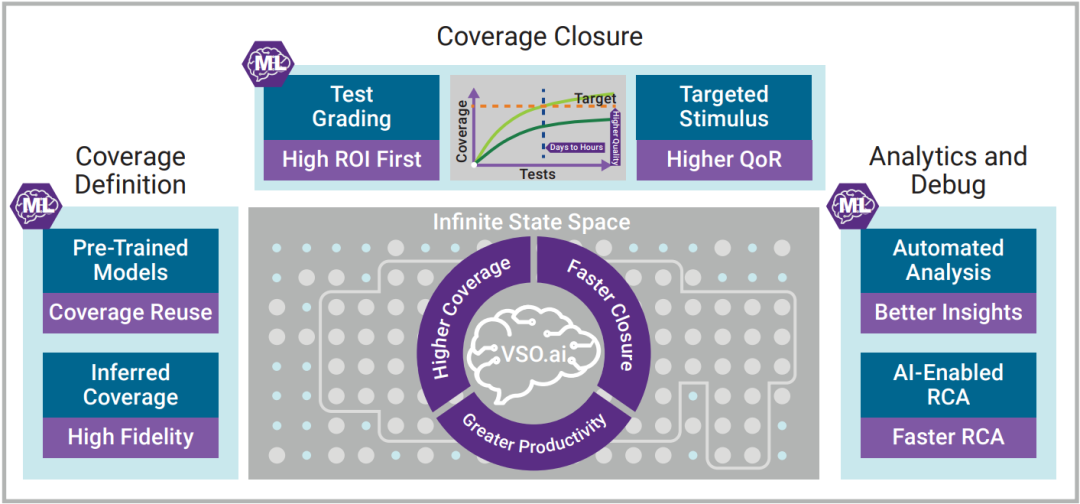

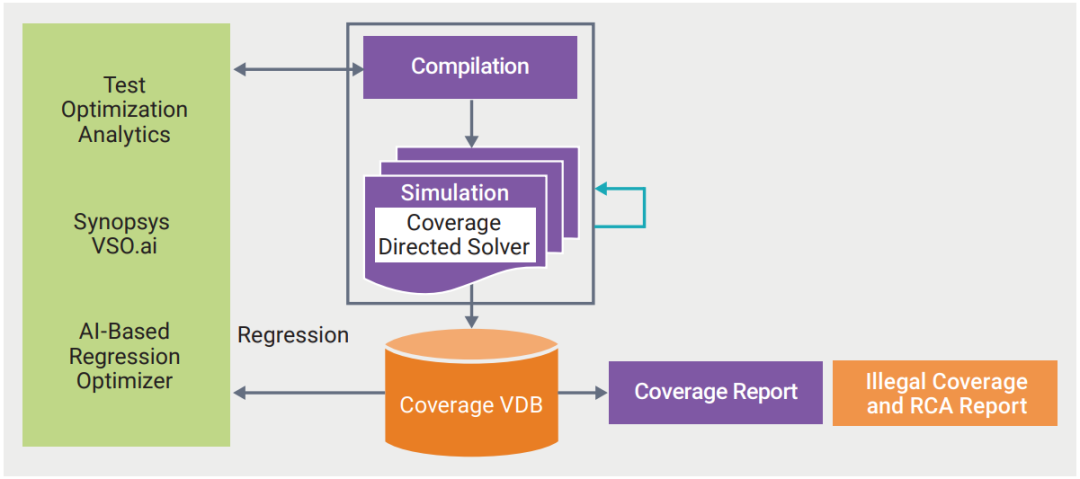

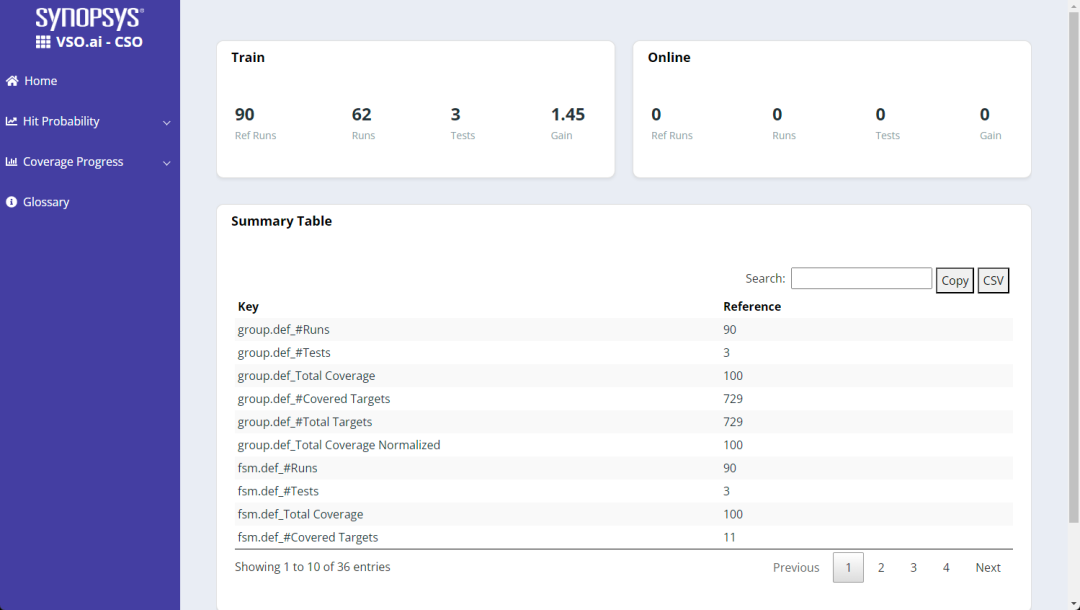

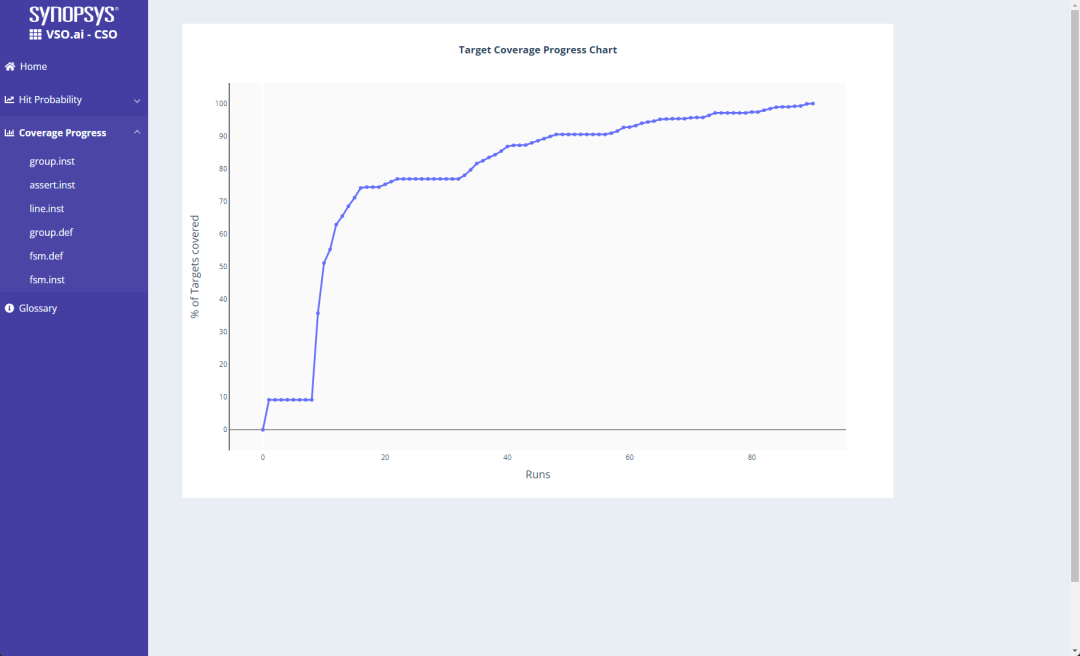

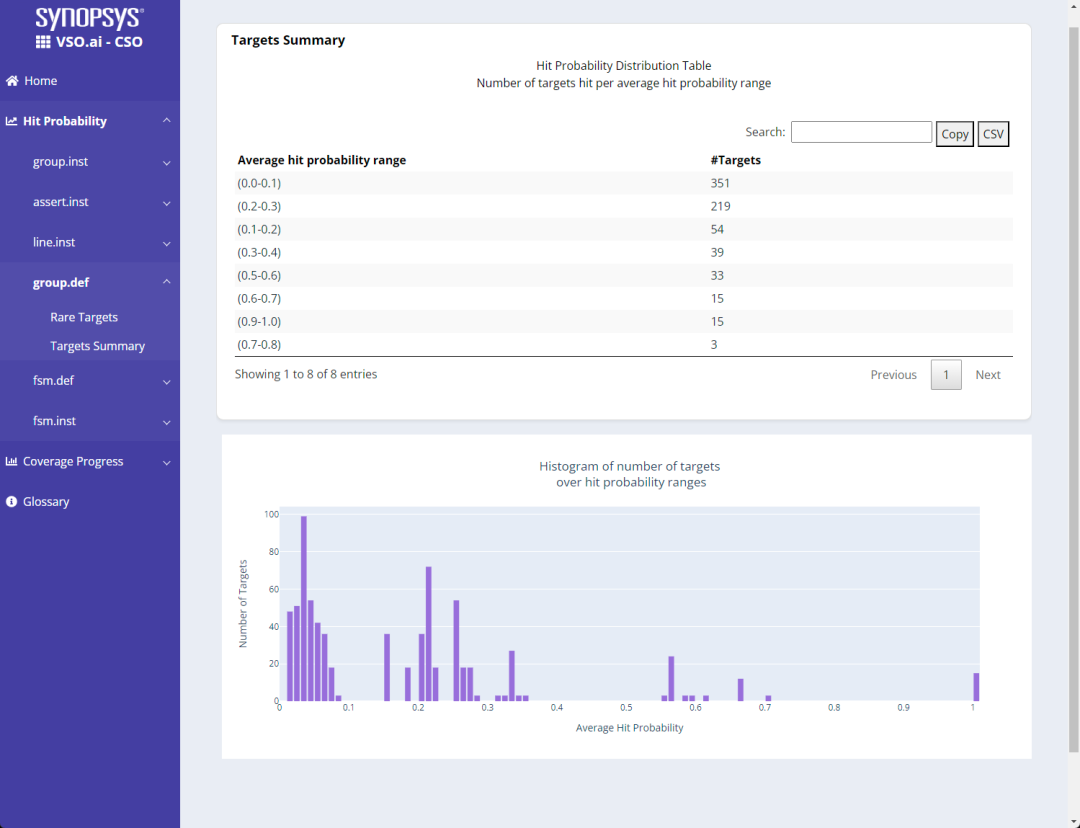

技術很快將難以滿足質量和上市時間的要求。通過新思科技VCS(Synopsys.ai解決方案的組成部分)的AI驅動型驗證,我們在減少功能覆蓋盲區方面實現了高達10倍的優化,并將IP驗證效率提高了30

2023-04-03 16:03:26

場景中落地,為各行業賦能。官網專欄產品頁訊飛開放平臺上線AI能力詳情頁,產品介紹,接入流程,能力提供方等信息一應俱全!全渠道推廣宣傳線上渠道,線下市場活動,會針對AI能力伙伴的產品進行全網宣傳和推廣

2018-07-06 08:58:38

能除了自研能力,科大訊飛還與業內優秀的技術廠商進行戰略互補形式的合作。帶來能力星云計劃。訊飛開放平臺自2010年成立以來,經過8年的積累,現已開放近百項AI能力,賦能88萬開發者團隊。在能力星云

2018-08-03 12:48:59

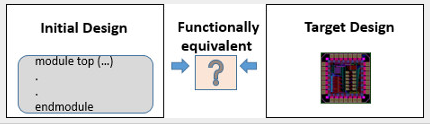

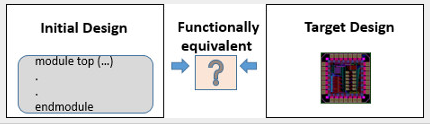

關于時序邏輯等效性的RTL設計和驗證流程介紹。

2021-04-28 06:13:14

本周四晚19:00知識賦能第七期第3課丨OpenHarmonyWiFi掃描儀實現8月25日19:00~20:00,第七期知識賦能第三節直播就要開始啦!如果你是缺乏實戰經驗的學生,如果你是初出茅廬

2022-08-24 11:59:51

本周四晚19:00知識賦能第八期第2課丨ArkUI自定義組件9月21日19:00~20:00,第八期知識賦能第2節直播就要開始啦!本次直播將為同學們帶來涂鴉小游戲的趣味體驗,讓大家全面了解ArkUI

2022-09-21 17:13:26

雷鋒網 AI 科技評論按:谷歌 DeepMind 博客昨日更新一篇關于機器學習如何賦能風力發電的文章,詳細介紹了谷歌全球可再生能源項目中針對風電場的機器學習實驗結果,雷鋒網(公眾號:雷鋒網) AI

2021-07-12 06:09:47

谷歌 DeepMind 博客昨日更新一篇關于機器學習如何賦能風力發電的文章,詳細介紹了谷歌全球可再生能源項目中針對風電場的機器學習實驗結果,雷鋒網(公眾號:雷鋒網) AI 科技評論將之編譯如下

2021-07-12 07:41:08

混合信號FPGA的智能型驗證流程是怎樣的?

2021-04-30 06:26:35

只是賦能第二期(入門)兩小時玩轉git和gitee

2021-12-03 11:09:29

這么重要,如何進行驗證呢?對于驗證來說,不同等級的驗證,它的方法是不一樣的。什么是驗證的等級,從設計流程(下圖)可以看到,驗證可以大致分為單獨子模塊驗證、功能模塊驗證、系統頂級驗證。絕對經典VCS中文教程[hide][/hide]

2011-12-15 10:37:49

產品,包括覆蓋多層次算力的智能工作站(邊緣計算盒子)、AI加速卡等;同時向大家展示自研的AI技術服務——“深元”0代碼移植工具鏈和創新性的行業解決方案,賦能更多AIoT產業生態企業快速具備AI能力

2023-09-25 10:03:19

VCS有哪幾種調試模式?萌新求助關于VCS仿真指南

2021-04-29 06:52:26

最近要用到VCS仿真后生成FSDB文件,然后在Verdi中進行自動偵錯,請問我怎么安裝Verdi這個軟件以及如何啟動license,并且怎么寫testbench文件才可以產生FSDB文件。請懂得人給我支支招,我也是剛開始學習這個軟件的使用。

2015-01-22 14:53:03

群主好,我想請教數字電路的系統級設計驗證工具及流程?即系統工程師常用的硬件描述語言,系統驗證工具以及設計驗證的基本流程,多謝!

2012-09-05 15:11:23

的工作與生活更加協調。我已經退休了,未來仍繼續以寫書、教書傳達我的感性科技觀。 社區小助手:采訪到這里就快要結束了,有什么話想要對大家說的嗎?高煥堂老師:VR/AR可以欺騙大腦,AI可以賦能大腦。兩者

2019-11-26 13:52:25

數模混合信號仿真已經成為SoC芯片驗證的重要環節。文章以一款固網短信電話專用SoC芯片為例,介紹一種使用Synopsys公司的NanoSim-VCS協同仿真環境進行仿真的驗證方法,并給出驗證結

2009-05-15 15:41:26 19

19 數模混合信號仿真已經成為SoC芯片驗證的重要環節。文章以一款固網短信電話專用SoC芯片為例,介紹一種使用Synopsys公司的NanoSim-VCS協同仿真環境進行仿真的驗證方法,并給出驗證結

2009-05-15 15:41:26 5

5 Synopsys VCS Training 培訓資料

2010-07-28 16:26:53 136

136 VCS是編譯型Verilog模擬器,它完全支持OVI標準的Verilog HDL語言、PLI和SDF。VCS具有目前行業中最高的模擬性能,其出色的內存管理能力足以支持千萬門級的ASIC設計,而其模擬精度也完全

2010-07-28 16:28:35 13018

13018 VCS-verilog compiled simulator是synopsys公司的產品.其仿真速度相當快,而且支持多種調用方式;使用的步驟和modelsim類似,都要先做

2010-10-09 16:59:08 5110

5110 Yuncam VCS PC套件使用說明

2017-01-14 16:11:19 0

0 在linux系統上實現vivado調用VCS仿真教程 作用:vivado調用VCS仿真可以加快工程的仿真和調試,提高效率。 前期準備:確認安裝vivado軟件和VCS軟件 VCS軟件最好安裝

2018-07-05 03:30:00 10733

10733

AWR公司,高頻EDA軟件的創新領導者,與電氣和電子工程軟件解決方案的領先供應商Zuken今天一起發布AWR Connected for Zuken。該射頻印刷電路板(PCB)驗證流程簡化

2017-12-07 16:40:17 447

447 采用System Verilog語言設計了一種具有層次化結構的可重用驗證平臺,該平臺能夠產生各種隨機、定向、錯誤測試向量,并提供功能覆蓋率計算。將驗證平臺在Synopsys公司的VCS仿真工具上運行

2018-01-12 11:28:24 2379

2379

Graphcore 芯片業務副總裁 Phil Horsfield 說:“為了對我們的 IPU 加速器進行全面驗證,需要每天進行涵蓋數以千計的復雜測試場景的仿真回歸分析。新思科技 VCS

2020-08-28 15:22:16 3187

3187 ? 新思科技(Synopsys)近日宣布,亞馬遜公司旗下云計算服務平臺(Amazon Web Services, Inc., AWS)已在其基于Arm的Graviton2服務器上部署了新思科技VCS

2021-01-07 11:28:06 8002

8002 5G單站驗證流程課件下載

2021-03-19 09:17:48 0

0 VCS是一個高性能、高容量的編譯代碼仿真器,它將高級抽象的驗證技術集成到一個開放的本地平臺中。它能夠分析、編譯和編譯Verilog、VHDL、SystemVerilog和OpenVera所描述

2022-05-07 14:20:57 3908

3908 VCS是編譯型verilog仿真器,VCS先將verilog/systemverilog文件轉化為C文件,在linux下編譯生成的可執行文./simv即可得到仿真結果。

2022-05-23 16:04:45 7608

7608 芯片驗證就是采用相應的驗證語言,驗證工具,驗證方法,在芯片生產之前驗證芯片設計是否符合芯片定義的需求規格,是否已經完全釋放了風險,發現并更正了所有的缺陷,站在全流程的角度,它是一種防范于未然的措施。

2022-07-25 11:48:49 5264

5264 本篇文章來源于微信群中的網友,分享下在SpinalHDL里如何絲滑的運行VCS跑Vivado相關仿真。自此仿真設計一體化不是問題。

2022-08-10 09:15:17 2040

2040 前年,發表了一篇文章《VCS獨立仿真Vivado IP核的一些方法總結》(鏈接在參考資料1),里面簡單講述了使用VCS仿真Vivado IP核時遇到的一些問題及解決方案,發表之后經過一年多操作上也有些許改進,所以寫這篇文章補充下。

2022-08-29 14:41:55 1551

1551 APM32E103VCS MINI開發板原理圖

2022-11-09 21:03:33 0

0 必須優化正式驗證流程中的初始網表,因此測試設計需要額外的邏輯。在這里,我們提供16 nm節點的形式驗證流程和調試技術。

2022-11-24 12:09:17 850

850

和靜態時序分析工具一起來完成對電路完備的驗證。本文就以Synopsys公司的formality工具為例,來介紹形式驗證的流程和基本概念,后續會詳細介紹使用formality做RTL2Gate流程中每一步驟的操作。

2022-12-27 15:18:11 1177

1177 幾乎所有的芯片設計、芯片驗證工程師,每天都在和VCS打交道,但是由于驗證環境的統一化管理,一般將不同的編譯仿真選項集成在一個文件里,只需要一兩個人維護即可。所以大部分人比較少有機會去深入地學習VCS的仿真flow。基于此,本文將介紹VCS仿真的 兩種flow ,概述這兩種flow分別做了哪些事!

2023-01-10 11:20:38 2281

2281 ? ? ? ? ? 原文標題:AI驅動芯片驗證:VSO.ai在手,覆蓋率收斂更快、更好、更高效 文章出處:【微信公眾號:新思科技】歡迎添加關注!文章轉載請注明出處。

2023-03-30 20:05:03 500

500 選擇VCS,再指定庫文件存放的路徑;如果VCS的環境變量設置好了,那么會自動跳出Simulator executable path的路徑的。

2023-03-31 10:21:43 964

964 ? ? ? ? ? 原文標題:下周五|AI驅動芯片驗證:VSO.ai在手,覆蓋率收斂更快、更好、更高效 文章出處:【微信公眾號:新思科技】歡迎添加關注!文章轉載請注明出處。

2023-03-31 17:30:02 520

520 ? ? ? ? ? 原文標題:本周五|AI驅動芯片驗證:VSO.ai在手,覆蓋率收斂更快、更好、更高效 文章出處:【微信公眾號:新思科技】歡迎添加關注!文章轉載請注明出處。

2023-04-03 22:20:04 320

320 我們以一個簡單的加法器為例,來看下如何用vcs+verdi仿真Verilog文件并查看波形。

源文件內容如下:

2023-05-11 17:03:36 1268

1268

vcs工作環境

2023-05-15 09:38:17 0

0 VCS是一款常見的Verilog編譯工具,它提供很多編譯選項來控制編譯過程及其輸出。本文主要介紹以下兩個編譯選項。

2023-05-29 14:46:39 6972

6972 VCS是編譯型verilog仿真器,VCS先將verilog/systemverilog文件轉化為C文件,在linux下編譯生成的可執行文./simv即可得到仿真結果。

2023-05-30 09:26:05 807

807

驗證其實是一個“證偽”的過程,從流程到工具,驗證工程師的終極目的都只有一個。

2023-05-31 10:34:49 1072

1072 最近,需要使用VCS仿真一個高速并串轉換的Demo,其中需要用到Vivado的SelectIO IP核以及IDELAYCTRL,IDELAY2原語。而此前我只使用VCS仿真過Quartus的IP核。

2023-06-06 11:09:56 1599

1599

使用VCS仿真Vivado里面的IP核時,如果Vivado的IP核的仿真文件只有VHDL時,仿真將變得有些困難,VCS不能直接仿真VHDL

2023-06-06 11:15:35 1328

1328

, VSO.ai)。任何新功能的真正考驗都是由真正的客戶在真正的設計中的使用,這也是本文的主題。請繼續閱讀,了解AMD如何將Synopsys AI驗證工具用于測試。

2023-09-21 14:43:07 785

785

FPGA原型驗證流程是確保FPGA(現場可編程門陣列)設計正確性和功能性的關鍵步驟。它涵蓋了從設計實現到功能驗證的整個過程,是FPGA開發流程中不可或缺的一環。

2024-03-15 15:05:33 97

97

電子發燒友App

電子發燒友App

評論