完善資料讓更多小伙伴認識你,還能領取20積分哦,立即完善>

標簽 > 功耗

文章:232個 瀏覽:32526次 帖子:293個

盡管如此,Zen 2看起來很像Zen。它屬于同一個系列,這意味著它看起來非常相似。AMD在這個平臺上所做的一切,啟用PCIe 4.0,并使服務器處理器擺...

PIC單片機在執行SLEEP指令后進入睡眠省電模式。進入SLEEP模式后,主振蕩停止,如果看門狗在燒寫時打開了,看門狗定時器將被清并保持運行。I/O口,...

靜態功耗是指一個電路維持在一個或另一個邏輯狀態時所需的功率。可以通過觀察電路中每個電阻元件的電流I和壓降V來計算每個元件的功率VI,并求和得到總功率,這...

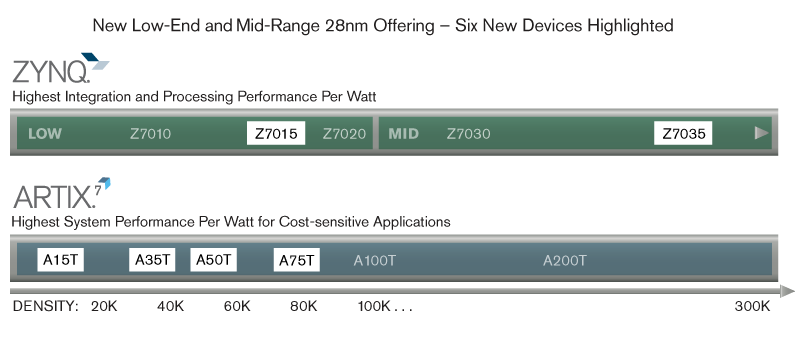

6大全新28nm 器件,功耗再降30%,擴大 28nm 領先地位

持續創新 28HPL 高性能低功耗工藝,成就跨越全新中低端器件,和 Artix-7 FPGA、Kintex-7 FPGA 及 Zynq-7000 SoC...

賽靈思宣布支持16nm UltraScale+器件工具與文檔公開支持主流市場

通過與 Vivado 設計套件的協同優化可以完全發揮 UltraScale+ 產品系列的功耗性能比優勢,以及 SmartCORE 及 LogiCORE ...

基于Virtex UltraScale FPGA的成本及功耗優化型銅線互連解決方案

連接您的服務器與架頂式交換機的方式中,與采用傳統光學連接相比,銅線兼具成本及功耗優化的優勢。您是否對采用更具成本效益的 25G 銅線連接更感興趣。

賽靈思推出豐富的智能解決方案能與安全、加密和 RegEx 功能方便集成

面向數據包處理的 Xilinx 智能方案包括 FPGA、 3D IC、和 SoC 以及一系列 SmartCORE IP,可進行定制優化以滿足獨特的市場需...

低功耗是MCU的一項非常重要的指標,比如某些可穿戴的設備,其攜帶的電量有限,如果整個電路消耗的電量特別大的話,就會經常出現電量不足的情況,影響用戶體驗。...

了解如何使用可用工具在UltraScale器件上執行功耗分析,以及如何估算從7系列FPGA遷移的設計的功耗。 還要了解如何操作Xilinx功耗估算器。

Kintex UltraScale FPGA KCU105評估套件的特點性能介紹

查看Kintex?UltraScale?FPGA KCU105評估套件,該評估套件具有完美的開發環境,可用于評估尖端的Kintex UltraScale...

了解如何為UltraScale +設計添加額外的安全級別。 該視頻演示了如何防止差分功耗分析(DPA),以在比特流配置之上增加額外的安全性。

了解如何為UltraScale +設計添加額外的安全級別。 該視頻演示了如何防止差分功耗分析(DPA),以在比特流配置之上增加額外的安全性。

了解如何為UltraScale +設計添加額外的安全級別。 該視頻演示了如何防止差分功耗分析(DPA),以在比特流配置之上增加額外的安全性。

了解如何為UltraScale +設計添加額外的安全級別。 該視頻演示了如何防止差分功耗分析(DPA),以在比特流配置之上增加額外的安全性。

換一批

換一批

編輯推薦廠商產品技術軟件/工具OS/語言教程專題

| 電機控制 | DSP | 氮化鎵 | 功率放大器 | ChatGPT | 自動駕駛 | TI | 瑞薩電子 |

| BLDC | PLC | 碳化硅 | 二極管 | OpenAI | 元宇宙 | 安森美 | ADI |

| 無刷電機 | FOC | IGBT | 逆變器 | 文心一言 | 5G | 英飛凌 | 羅姆 |

| 直流電機 | PID | MOSFET | 傳感器 | 人工智能 | 物聯網 | NXP | 賽靈思 |

| 步進電機 | SPWM | 充電樁 | IPM | 機器視覺 | 無人機 | 三菱電機 | ST |

| 伺服電機 | SVPWM | 光伏發電 | UPS | AR | 智能電網 | 國民技術 | Microchip |

| 開關電源 | 步進電機 | 無線充電 | LabVIEW | EMC | PLC | OLED | 單片機 |

| 5G | m2m | DSP | MCU | ASIC | CPU | ROM | DRAM |

| NB-IoT | LoRa | Zigbee | NFC | 藍牙 | RFID | Wi-Fi | SIGFOX |

| Type-C | USB | 以太網 | 仿真器 | RISC | RAM | 寄存器 | GPU |

| 語音識別 | 萬用表 | CPLD | 耦合 | 電路仿真 | 電容濾波 | 保護電路 | 看門狗 |

| CAN | CSI | DSI | DVI | Ethernet | HDMI | I2C | RS-485 |

| SDI | nas | DMA | HomeKit | 閾值電壓 | UART | 機器學習 | TensorFlow |

| Arduino | BeagleBone | 樹莓派 | STM32 | MSP430 | EFM32 | ARM mbed | EDA |

| 示波器 | LPC | imx8 | PSoC | Altium Designer | Allegro | Mentor | Pads |

| OrCAD | Cadence | AutoCAD | 華秋DFM | Keil | MATLAB | MPLAB | Quartus |

| C++ | Java | Python | JavaScript | node.js | RISC-V | verilog | Tensorflow |

| Android | iOS | linux | RTOS | FreeRTOS | LiteOS | RT-THread | uCOS |

| DuerOS | Brillo | Windows11 | HarmonyOS |