完善資料讓更多小伙伴認(rèn)識(shí)你,還能領(lǐng)取20積分哦,立即完善>

標(biāo)簽 > 電源完整性

電源完整性通常指三個(gè)方面:1、電源紋波及噪聲要滿(mǎn)足系統(tǒng)工作要求。2、由于模擬電源要求的噪聲極小,所以必須通過(guò)一定手段濾除外界噪聲干擾。3、電源系統(tǒng)要提供給芯片所需的額定電平,不能有太大偏離。

電源完整性通常指三個(gè)方面:1、電源紋波及噪聲要滿(mǎn)足系統(tǒng)工作要求。2、由于模擬電源要求的噪聲極小,所以必須通過(guò)一定手段濾除外界噪聲干擾。3、電源系統(tǒng)要提供給芯片所需的額定電平,不能有太大偏離。

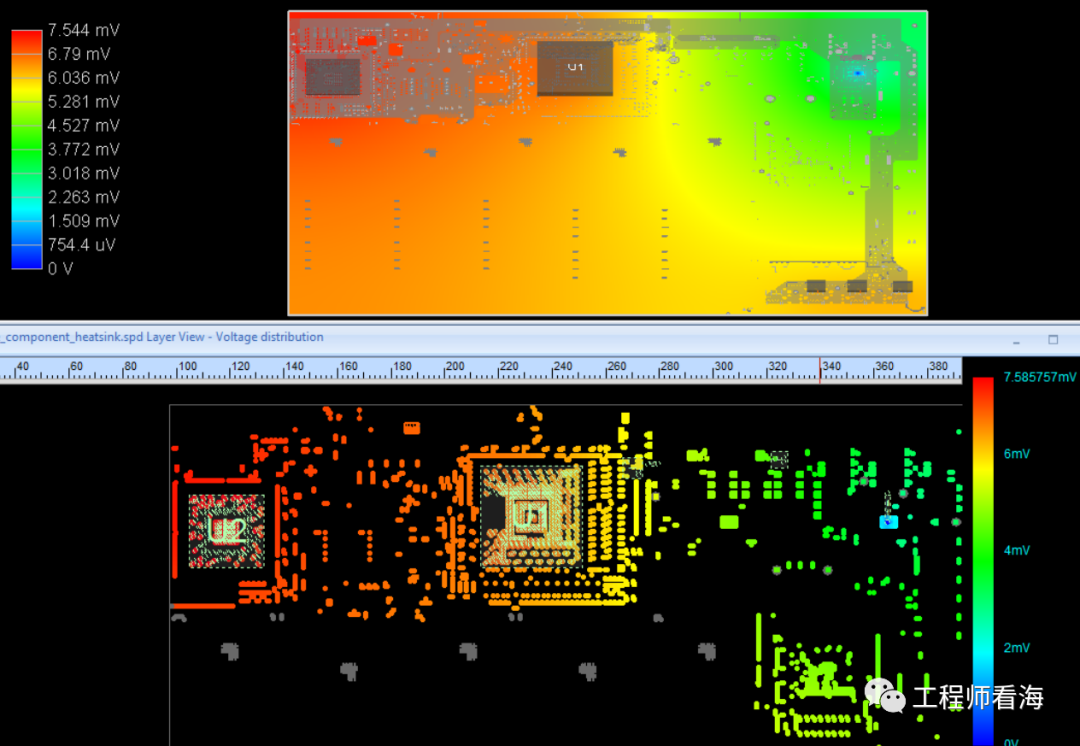

第1和第2點(diǎn)相似,都和電源噪聲有關(guān)。第3點(diǎn)要求電源在路徑上不能有太大的直流壓降。

電源質(zhì)量如果不滿(mǎn)足要求,往往導(dǎo)致PCB出現(xiàn)無(wú)規(guī)則的怪異行為,很難直接定位問(wèn)題所在,往往需要很長(zhǎng)時(shí)間才能找到故障原因。所以電源完整性問(wèn)題必須引起足夠重視。

電源完整性設(shè)計(jì)最常見(jiàn)的幾個(gè)方面包括:去耦電容的配置、磁珠濾波器或LC濾波器的配置、直流壓降控制

電源完整性通常指三個(gè)方面:1、電源紋波及噪聲要滿(mǎn)足系統(tǒng)工作要求。2、由于模擬電源要求的噪聲極小,所以必須通過(guò)一定手段濾除外界噪聲干擾。3、電源系統(tǒng)要提供給芯片所需的額定電平,不能有太大偏離。

第1和第2點(diǎn)相似,都和電源噪聲有關(guān)。第3點(diǎn)要求電源在路徑上不能有太大的直流壓降。

電源質(zhì)量如果不滿(mǎn)足要求,往往導(dǎo)致PCB出現(xiàn)無(wú)規(guī)則的怪異行為,很難直接定位問(wèn)題所在,往往需要很長(zhǎng)時(shí)間才能找到故障原因。所以電源完整性問(wèn)題必須引起足夠重視。

電源完整性設(shè)計(jì)最常見(jiàn)的幾個(gè)方面包括:去耦電容的配置、磁珠濾波器或LC濾波器的配置、直流壓降控制

最近在論壇里看到一則關(guān)于電源完整性的提問(wèn),網(wǎng)友質(zhì)疑大家普遍對(duì)信號(hào)完整性很重視,但對(duì)于電源完整性的重視好像不夠,主要是因?yàn)椋瑢?duì)于低頻應(yīng)用,開(kāi)關(guān)電源的設(shè)計(jì)更...

2017-12-26 標(biāo)簽:信號(hào)完整性電源完整性 3.5萬(wàn) 0

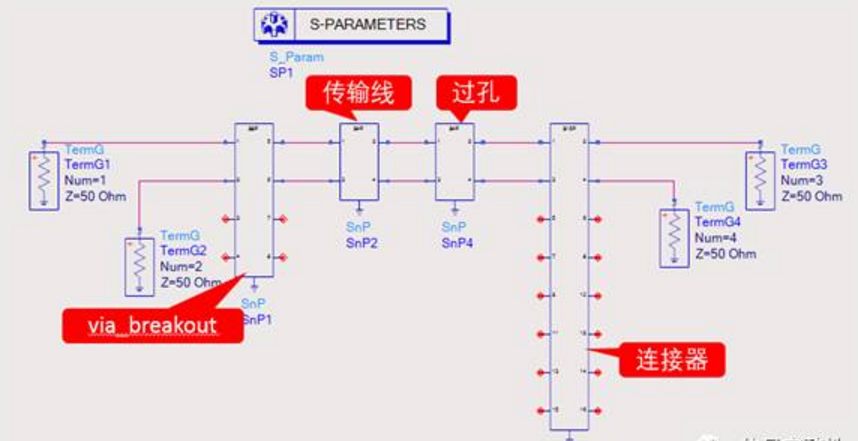

ADS的信號(hào)完整性和電源完整性仿真應(yīng)用方案

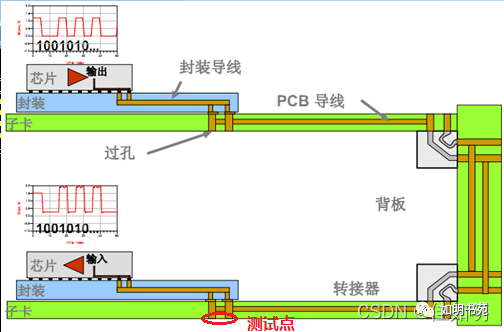

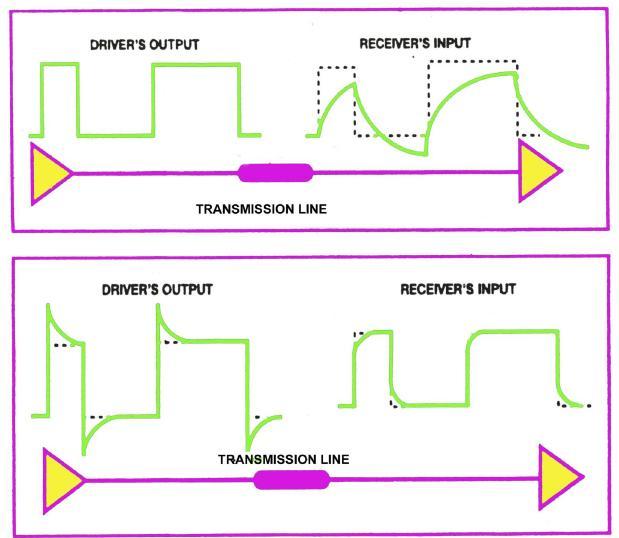

隨著數(shù)據(jù)傳輸速率的快速增加,從而使得以前微秒(us)量級(jí)的邊沿或保持時(shí)間減少到納秒(ns)甚至皮秒(ps)。如此高的帶寬需求使得傳統(tǒng)的設(shè)計(jì)解決方案已經(jīng)很...

2017-12-04 標(biāo)簽:信號(hào)完整性電源完整性ads 3.3萬(wàn) 0

電源完整性中接地規(guī)則:?jiǎn)吸c(diǎn)接地和多點(diǎn)接地區(qū)別

多點(diǎn)接地電路簡(jiǎn)單,高頻駐波會(huì)減少,缺點(diǎn)是電路中會(huì)增加很多接地環(huán)路,一定程度上會(huì)降低會(huì)外界磁場(chǎng)的抵御能力。

2021-03-22 標(biāo)簽:DC-DC信號(hào)完整性電磁干擾 2.5萬(wàn) 0

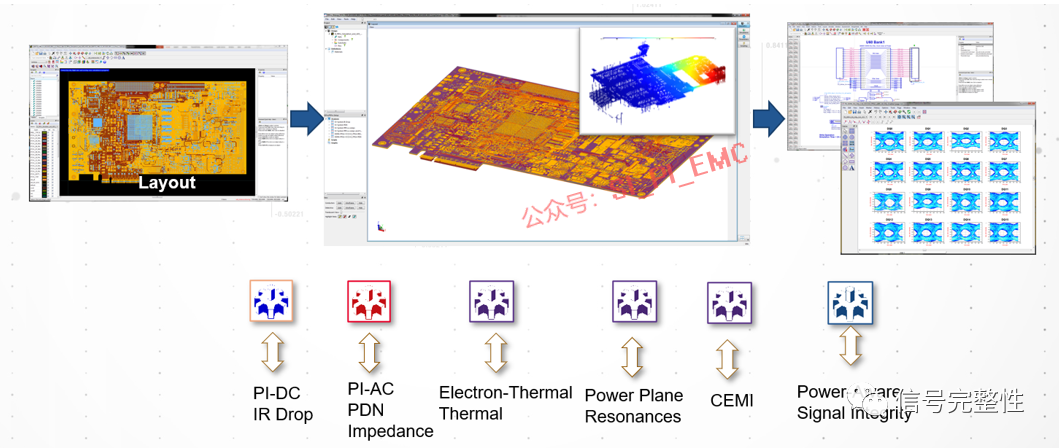

SIPro/PIPro是內(nèi)嵌于ADS 版圖設(shè)計(jì)環(huán)境中的功能模塊,它包含獨(dú)立的仿真界面及仿真器,可以對(duì)版圖設(shè)計(jì)進(jìn)行分析。

電源完整性(PI,PowerIntegrity)就是為板級(jí)系統(tǒng)提供一個(gè)穩(wěn)定可靠的電源分配系統(tǒng)(PDS)。實(shí)質(zhì)上是要使系統(tǒng)在工作時(shí),電源、地噪聲得到有效的...

介紹一下ADS中時(shí)域仿真組件中的Vprbs電壓源的用法

在當(dāng)今電子行業(yè)中信號(hào)仿真作為信號(hào)完整性、電源完整性的重要手段之一,正在被越來(lái)越多的企業(yè)和工程師所重視,而ADS在眾多仿真軟件中的作用無(wú)疑是舉足輕重的;

2023-10-11 標(biāo)簽:電壓源信號(hào)完整性ADS仿真 1.3萬(wàn) 0

數(shù)電》《模電》《電磁場(chǎng)》,這三門(mén)課只要是電子相關(guān)專(zhuān)業(yè),在大學(xué)的時(shí)候都會(huì)接觸。數(shù)電主要講0和1之間的邏輯關(guān)系,模電關(guān)心模擬信號(hào)的波形,電磁場(chǎng)從更高的維度來(lái)...

2020-09-14 標(biāo)簽:信號(hào)完整性數(shù)字信號(hào)電源完整性 1.1萬(wàn) 0

PCB走線(xiàn)基礎(chǔ)(一):電源完整性與PDN設(shè)計(jì)

SI(信號(hào)完整性)研究的是信號(hào)的波形質(zhì)量,而PI(電源完整性)研究的是電源波形質(zhì)量, PI研究的對(duì)象是PDN(Power Distribution Ne...

信號(hào)完整性(Signal Integrity,SI),也就是我們通常所說(shuō)的信號(hào)質(zhì)量。隨著信號(hào)速率的提高,數(shù)字信號(hào)的傳輸已經(jīng)不能只考慮邏輯上的實(shí)現(xiàn),而要考...

2023-06-12 標(biāo)簽:接收器信號(hào)完整性電源完整性 9873 0

1

0

標(biāo)簽:電源完整性 62960 1

63

5

【送書(shū)福利】不懂PDN談何電源完整性?請(qǐng)收下這本PDN設(shè)計(jì)指導(dǎo)硬核書(shū)

標(biāo)簽:電源設(shè)計(jì)電源完整性PDN 12866 63

類(lèi)別:電子教材 2011-11-30 標(biāo)簽:信號(hào)完整性電源完整性仿真分析

類(lèi)別:IC中文資料 2024-08-12 標(biāo)簽:信號(hào)完整性電源完整性

類(lèi)別:PCB設(shè)計(jì)規(guī)則 2015-08-31 標(biāo)簽:仿真電源完整性Hyperlynx

高速電路信號(hào)完整性分析與設(shè)計(jì)(九).rar立即下載

類(lèi)別:電子書(shū)籍 2012-05-29 標(biāo)簽:電源完整性高速電路信號(hào)高速PCB板

信號(hào)完整性與電源完整性的仿真分析與設(shè)計(jì)立即下載

類(lèi)別:PCB設(shè)計(jì)規(guī)則 2016-12-14 標(biāo)簽:信號(hào)完整性電源完整性

類(lèi)別:PCB設(shè)計(jì)規(guī)則 2021-04-21 標(biāo)簽:pcb電源完整性電源分配網(wǎng)絡(luò)

類(lèi)別:電源技術(shù) 2021-09-29 標(biāo)簽:信號(hào)完整性電源完整性

華為公司是如何開(kāi)展信號(hào)完整性和電源完整性分析研究工作的立即下載

類(lèi)別:電源技術(shù) 2015-01-13 標(biāo)簽:信號(hào)完整性電源完整性

1 電源完整性概述 電源完整性(Power Integrity)簡(jiǎn)稱(chēng)PI,是確認(rèn)電源來(lái)源、目的端電壓以及電流是否符合需求。PI所研究的就是如何為整個(gè)系統(tǒng)...

電源路徑與信號(hào)路徑是有區(qū)別的,電源分配網(wǎng)絡(luò)中一個(gè)電源路徑可以在一個(gè)節(jié)點(diǎn)分成多個(gè)路徑,或者說(shuō)轉(zhuǎn)換成多個(gè)電源,終端掛多個(gè)元器件,可以理解為一對(duì)多,而信號(hào)路徑...

電源完整性 (Power Integrity) :是指系統(tǒng)供電電源在經(jīng)過(guò)一定的傳輸網(wǎng)絡(luò)后在指定器件端口相對(duì)該器件對(duì)工作電源要求的符合程度。雖然電源完整性...

2017-11-27 標(biāo)簽:電源完整性 7449 0

基于Cadence的信號(hào)和電源完整性設(shè)計(jì)與分析

在Cadence信號(hào)和電源完整性三天活動(dòng)的第二天,只有100多名與會(huì)者聽(tīng)取了會(huì)議,Robert Hanson解釋了與DDR3和PCI Express 3...

2019-09-01 標(biāo)簽:信號(hào)完整性電源完整性 6236 0

電源完整性設(shè)計(jì)之ESR對(duì)反諧振的影響

ESR對(duì)反諧振(Anti-Resonance)的影響,現(xiàn)代工藝生產(chǎn)的貼片電容,等效串聯(lián)阻抗很低,因此就有辦法控制電容并聯(lián)去耦時(shí)反諧振點(diǎn)處的阻抗。等效串聯(lián)...

eda怎么自動(dòng)布線(xiàn) eda布線(xiàn)完了之后干嘛

EDA(電子設(shè)計(jì)自動(dòng)化)軟件通常提供了自動(dòng)布線(xiàn)工具,以幫助設(shè)計(jì)師在電路板設(shè)計(jì)中進(jìn)行自動(dòng)布線(xiàn)。以下是一般的自動(dòng)布線(xiàn)流程。

2023-09-26 標(biāo)簽:電路板EDA信號(hào)線(xiàn) 3391 0

開(kāi)關(guān)電源為什么要測(cè)控制環(huán)路響應(yīng)

當(dāng)你發(fā)現(xiàn)信號(hào)完整性不好時(shí), 會(huì)不會(huì)是電源完整性帶來(lái)的問(wèn)題?當(dāng)你發(fā)現(xiàn)時(shí)鐘抖動(dòng)很大時(shí),會(huì)不會(huì)是電源質(zhì)量不好?當(dāng)你發(fā)現(xiàn)系統(tǒng)有誤碼時(shí),會(huì)不會(huì)是電源的控制環(huán)路...

2022-09-05 標(biāo)簽:開(kāi)關(guān)電源電源完整性控制環(huán)路 3295 0

發(fā)現(xiàn)電源完整性分析如何減少對(duì)你的設(shè)計(jì)旋轉(zhuǎn)和削減成本。

2019-11-05 標(biāo)簽:設(shè)計(jì)電源完整性 3221 0

芯和半導(dǎo)體片上無(wú)源電磁場(chǎng)仿真套件成功通過(guò)三星8LPP工藝認(rèn)證

三星電子設(shè)計(jì)Design Enablement團(tuán)隊(duì)副總裁Jongwook Kye說(shuō):“芯和半導(dǎo)體的三維全波EM套件的成功認(rèn)證,將為我們共同的客戶(hù)在創(chuàng)建模...

換一批

換一批

編輯推薦廠商產(chǎn)品技術(shù)軟件/工具OS/語(yǔ)言教程專(zhuān)題

| 電機(jī)控制 | DSP | 氮化鎵 | 功率放大器 | ChatGPT | 自動(dòng)駕駛 | TI | 瑞薩電子 |

| BLDC | PLC | 碳化硅 | 二極管 | OpenAI | 元宇宙 | 安森美 | ADI |

| 無(wú)刷電機(jī) | FOC | IGBT | 逆變器 | 文心一言 | 5G | 英飛凌 | 羅姆 |

| 直流電機(jī) | PID | MOSFET | 傳感器 | 人工智能 | 物聯(lián)網(wǎng) | NXP | 賽靈思 |

| 步進(jìn)電機(jī) | SPWM | 充電樁 | IPM | 機(jī)器視覺(jué) | 無(wú)人機(jī) | 三菱電機(jī) | ST |

| 伺服電機(jī) | SVPWM | 光伏發(fā)電 | UPS | AR | 智能電網(wǎng) | 國(guó)民技術(shù) | Microchip |

| Arduino | BeagleBone | 樹(shù)莓派 | STM32 | MSP430 | EFM32 | ARM mbed | EDA |

| 示波器 | LPC | imx8 | PSoC | Altium Designer | Allegro | Mentor | Pads |

| OrCAD | Cadence | AutoCAD | 華秋DFM | Keil | MATLAB | MPLAB | Quartus |

| C++ | Java | Python | JavaScript | node.js | RISC-V | verilog | Tensorflow |

| Android | iOS | linux | RTOS | FreeRTOS | LiteOS | RT-THread | uCOS |

| DuerOS | Brillo | Windows11 | HarmonyOS |