完善資料讓更多小伙伴認識你,還能領(lǐng)取20積分哦,立即完善>

標簽 > ACAP

ACAP是賽靈思在2018年推出的新一代計算平臺,是一種革命性異構(gòu)計算架構(gòu)。ACAP整合了硬件可編程邏輯單元、軟件可編程處理器、以及軟件可編程加速引擎的計算平臺產(chǎn)品。

ACAP是賽靈思在2018年推出的新一代計算平臺,是一種革命性異構(gòu)計算架構(gòu)。

ACAP結(jié)合了矢量、標量、自適應(yīng)硬件單元,提供了三大引人注目的優(yōu)勢:軟件可編程特性、 異構(gòu)加速、靈活應(yīng)變能力。

ACAP整合了硬件可編程邏輯單元、軟件可編程處理器、以及軟件可編程加速引擎的計算平臺產(chǎn)品。

petalinux是什么?petallinux是如何設(shè)計的

這里使用一下petalinux工具。vivado,vitis HLS 都安裝在windows 下,而petalinux 必須安裝在linux 下,嘗試安...

2022-09-29 標簽:ZynqUbuntu系統(tǒng)ACAP 1.4萬 0

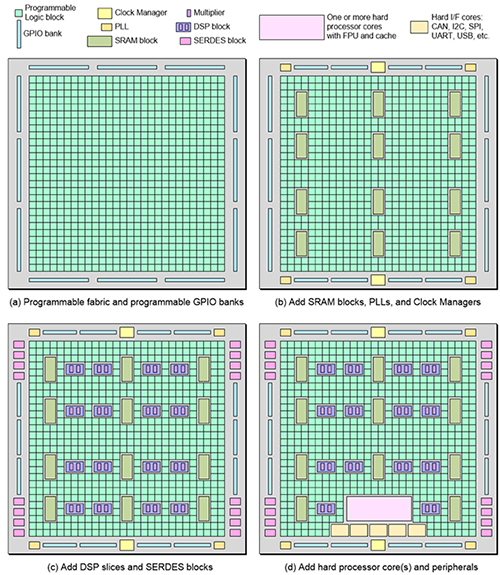

一文了解Xilinx FPGA架構(gòu)及相關(guān)工具

作者:Clive Max Maxfield,Digi-Key北美編輯 現(xiàn)場可編程門陣列 (FPGA) 具有諸多特性,無論是單獨使用,抑或采用多樣化架構(gòu),...

引言 隨著人工智能和5G的興起,數(shù)據(jù)處理對芯片的算力和帶寬要求更高。為了布局未來,助力人工智能和5G,賽靈思也推出了自己的FPGA加速芯片-ACAP。A...

ME結(jié)構(gòu)在FPGA加速芯片ACAP有何作用

隨著人工智能和5G的興起,數(shù)據(jù)處理對芯片的算力和帶寬要求更高。為了布局未來,助力人工智能和5G,賽靈思也推出了自己的FPGA加速芯片-ACAP。ACAP...

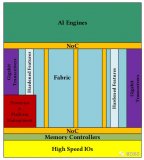

AMD自適應(yīng)計算加速平臺(ACAP)是一個完全軟件可編程資源集合,這些資源結(jié)合在一起構(gòu)成片上系統(tǒng) (SoC),包括以下主要的資源塊

2023-11-27 標簽:收發(fā)器控制器片上系統(tǒng) 1772 0

非整數(shù)數(shù)據(jù)恢復單元應(yīng)用說明立即下載

類別:電子資料 2023-09-13 標簽:數(shù)據(jù)恢復VersalACAP

計算架構(gòu)迎來黃金時代,水大魚大、風高浪急的新十年已開啟

這一個新十年,時代的“大”和“快”從數(shù)字的比較上是以前難以想象的。大數(shù)據(jù)雪崩爆發(fā)時,每一片雪花都是意義的;有些事件看似離我們很遠,但被浪花打到時依然有力...

都在擁抱新基建,橫跨七大領(lǐng)域的計算平臺如何差異化?

新基建的核心就是數(shù)據(jù),七大領(lǐng)域所覆蓋的汽車、城際高速、特高壓、工業(yè)物聯(lián)網(wǎng)等傳統(tǒng)行業(yè),面臨產(chǎn)業(yè)數(shù)字化的轉(zhuǎn)型機會;5G、人工智能、數(shù)據(jù)中心等,則面臨數(shù)字產(chǎn)業(yè)...

Versal 自適應(yīng)計算加速平臺 (ACAP) 將標量引擎 (Scalar Engine)、自適應(yīng)引擎 (Adaptable Engine) 和智能引擎...

賽靈思 Versal 自適應(yīng)計算加速平臺 (ACAP) 設(shè)計方法論是旨在幫助精簡 Versal 器件設(shè)計進程的一整套最佳實踐。鑒于這些設(shè)計的規(guī)模與復雜性...

2020 人工智能卓越創(chuàng)新獎,請為Xilinx打call

賽靈思: FPGA、可編程 SoC,以及 ACAP 自適應(yīng)計算加速的發(fā)明者,“致力于打造靈活應(yīng)變,萬物只能的世界”。從消費電子到自動駕駛、從云到端到邊緣...

? 在日前召開的FPGA領(lǐng)域的學術(shù)頂會--2019年“FPGA國際研討會”上,賽靈思發(fā)表了兩篇長論文,詳細介紹了賽靈思“自適應(yīng)計算加速平臺”ACAP的系...

在瞬息萬變的智能化時代, 單一計算架構(gòu)已難以應(yīng)對處理海量數(shù)據(jù)的重任, 業(yè)界亟需“異構(gòu)計算”來解決當今所面臨的挑戰(zhàn), 賽靈思 Versal ACAP, 作...

賽靈思推第三代ACAP平臺Versal Premium,計算密度為FPGA兩倍

賽靈思發(fā)布ACAP的第三代產(chǎn)品——Versal Premium系列,該處理器采用臺積電7nm制程工藝,集成軟件可編程功能、動態(tài)可配置硬件加速、預制連接和...

賽靈思Versal評估套件助力開發(fā)者邁入解鎖ACAP功能的高速路

裝備業(yè)界首個自適應(yīng)計算加速平臺(ACAP)的賽靈思 Versal AI Core 系列 VCK190評估套件 和 Versal Prime 系列 VMK...

如何根據(jù)Versal ACAP架構(gòu)的描述來使用XPE

對于任何一項設(shè)計,要想盡可能實現(xiàn)最低的功率包絡(luò),都需要在設(shè)計周期早期準確估算功耗。早期估算有助于選擇合適的器件、充分發(fā)揮架構(gòu)優(yōu)勢、更改設(shè)計拓撲,以及使用...

換一批

換一批

編輯推薦廠商產(chǎn)品技術(shù)軟件/工具OS/語言教程專題

| 電機控制 | DSP | 氮化鎵 | 功率放大器 | ChatGPT | 自動駕駛 | TI | 瑞薩電子 |

| BLDC | PLC | 碳化硅 | 二極管 | OpenAI | 元宇宙 | 安森美 | ADI |

| 無刷電機 | FOC | IGBT | 逆變器 | 文心一言 | 5G | 英飛凌 | 羅姆 |

| 直流電機 | PID | MOSFET | 傳感器 | 人工智能 | 物聯(lián)網(wǎng) | NXP | 賽靈思 |

| 步進電機 | SPWM | 充電樁 | IPM | 機器視覺 | 無人機 | 三菱電機 | ST |

| 伺服電機 | SVPWM | 光伏發(fā)電 | UPS | AR | 智能電網(wǎng) | 國民技術(shù) | Microchip |

| Arduino | BeagleBone | 樹莓派 | STM32 | MSP430 | EFM32 | ARM mbed | EDA |

| 示波器 | LPC | imx8 | PSoC | Altium Designer | Allegro | Mentor | Pads |

| OrCAD | Cadence | AutoCAD | 華秋DFM | Keil | MATLAB | MPLAB | Quartus |

| C++ | Java | Python | JavaScript | node.js | RISC-V | verilog | Tensorflow |

| Android | iOS | linux | RTOS | FreeRTOS | LiteOS | RT-THread | uCOS |

| DuerOS | Brillo | Windows11 | HarmonyOS |