完善資料讓更多小伙伴認(rèn)識(shí)你,還能領(lǐng)取20積分哦,立即完善>

標(biāo)簽 > hls

HLS(HTTP Live Streaming)是Apple的動(dòng)態(tài)碼率自適應(yīng)技術(shù)。主要用于PC和Apple終端的音視頻服務(wù)。包括一個(gè)m3u(8)的索引文件,TS媒體分片文件和key加密串文件。

文章:98個(gè) 瀏覽:24675次 帖子:45個(gè)

多種數(shù)據(jù)類型給用戶提供了更多的選擇,用戶可根據(jù)實(shí)際需求選擇可最佳匹配于硬件的數(shù)據(jù)類型。一個(gè)小的技巧是,把數(shù)據(jù)類型通過typedef定義在用戶的頭文件中。...

2018-12-12 標(biāo)簽:C++數(shù)據(jù)類型HLS 1.7萬 0

索貝爾算子(Sobel operator)主要用作邊緣檢測,在技術(shù)上,它是一離散性差分算子,用來運(yùn)算圖像亮度函數(shù)的灰度之近似值。在圖像的任何一點(diǎn)使用此算...

第二步,不設(shè)置任何directive,直接執(zhí)行C綜合,此時(shí)會(huì)顯示如下錯(cuò)誤信息。該信息表明,在非dataflow區(qū)域使用默認(rèn)的FIFO規(guī)模(這個(gè)FIFO是...

FPGA設(shè)計(jì)中的HLS 工具應(yīng)用

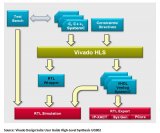

在集成電路行業(yè)飛速發(fā)展的今天,縮短產(chǎn)品開發(fā)的周期而又不犧牲驗(yàn)證過程,這不可避免地成為了商業(yè)市場的一個(gè)關(guān)鍵因素。Xilinx Vivado High Le...

高層次綜合(High Level Synthesis, HLS)是Xilinx公司推出的最新一代的FPGA設(shè)計(jì)工具,它能讓用戶通過編寫C/C++等高級語...

XIlinx利用HLS進(jìn)行加速設(shè)計(jì)進(jìn)度

接著開始正文。據(jù)觀察,HLS的發(fā)展呈現(xiàn)愈演愈烈的趨勢,隨著Xilinx Vivado HLS的推出,intel也快馬加鞭的推出了其HLS工具。HLS可以...

此外,通過()或range()還可選取指定范圍的某幾位。代碼片段如圖5所示,相應(yīng)的輸出結(jié)果圖6所示。相比較,直接使用()操作會(huì)更快捷。同時(shí),該操作還可實(shí)...

Vivado設(shè)計(jì)之HLS開發(fā)詳細(xì)步驟

對于Vivado Hls來說,輸入包括Tesbench,C/C++源代碼和Directives,相應(yīng)的輸出為IP Catalog,DSP和SysGen,...

這種方法還可以更好地與團(tuán)隊(duì)方法一起使用,并且可以創(chuàng)建可跨多個(gè)項(xiàng)目使用的加速內(nèi)核庫(IP)。另一個(gè)優(yōu)點(diǎn)是應(yīng)用于可編程邏輯實(shí)現(xiàn)的優(yōu)化駐留在 .xo 文件中,...

Vivado環(huán)境下如何在IP Integrator中正確使用HLS IP

介紹如何設(shè)計(jì)HLS IP,并且在IP Integrator中使用它來作一個(gè)設(shè)計(jì)——這里生成兩個(gè)HLS blocks的IP,并且在一個(gè)FFT(Xilinx...

通過HLS封裝的縮放IP來實(shí)現(xiàn)視頻圖像縮放技術(shù)

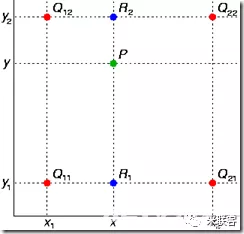

放大測試:將640x480分辨率圖像放大到1024x600 縮小測試:將720P分辨率圖像縮小到640x480。 實(shí)現(xiàn)的縮放IP主要用于功能驗(yàn)證,可以在...

2020-11-14 標(biāo)簽:視頻圖像圖象處理圖像傳輸系統(tǒng) 4382 0

使用教程分享:在Zynq AP SoC設(shè)計(jì)中高效使用HLS IP(一)

高層次綜合設(shè)計(jì)最常見的的使用就是為CPU創(chuàng)建一個(gè)加速器,將在CPU中執(zhí)行的代碼移動(dòng)到FPGA可編程邏輯去提高性能。本文展示了如何在Zynq AP SoC...

使用教程分享連載:在Zynq AP SoC設(shè)計(jì)中高效使用HLS IP(二)

對于硬件加速模塊來說,這些硬件加速模塊會(huì)消耗源于CPU存儲(chǔ)器的數(shù)據(jù),并且以streaming方式產(chǎn)生數(shù)據(jù)。本文使用Vivado HLS和xfft IP模...

FPGA專家教您如何在FPGA設(shè)計(jì)中使用HLS

Luke Miller并非一開始就是HLS(高層次綜合)的倡導(dǎo)者。在使用早期的工具版本的時(shí)候,他似乎有過一些糟糕的經(jīng)歷。

2017-02-10 標(biāo)簽:FPGAFPGA設(shè)計(jì)HLS 3779 0

HLS高階綜合(high level synthesis)在被廣泛使用之前,作為商業(yè)技術(shù)其實(shí)已經(jīng)存在了20多年。設(shè)計(jì)團(tuán)隊(duì)對于這項(xiàng)技術(shù)可以說呈現(xiàn)出兩極化的...

調(diào)用HLS的FFT庫實(shí)現(xiàn)N點(diǎn)FFT(hls:fft)

在HLS中用C語言實(shí)現(xiàn)8192點(diǎn)FFT,經(jīng)過測試,實(shí)驗(yàn)結(jié)果正確,但是時(shí)序約束不到100M的時(shí)鐘,應(yīng)該是設(shè)計(jì)上的延時(shí)之類的比較大,暫時(shí)放棄這個(gè)方案

換一批

換一批

編輯推薦廠商產(chǎn)品技術(shù)軟件/工具OS/語言教程專題

| 電機(jī)控制 | DSP | 氮化鎵 | 功率放大器 | ChatGPT | 自動(dòng)駕駛 | TI | 瑞薩電子 |

| BLDC | PLC | 碳化硅 | 二極管 | OpenAI | 元宇宙 | 安森美 | ADI |

| 無刷電機(jī) | FOC | IGBT | 逆變器 | 文心一言 | 5G | 英飛凌 | 羅姆 |

| 直流電機(jī) | PID | MOSFET | 傳感器 | 人工智能 | 物聯(lián)網(wǎng) | NXP | 賽靈思 |

| 步進(jìn)電機(jī) | SPWM | 充電樁 | IPM | 機(jī)器視覺 | 無人機(jī) | 三菱電機(jī) | ST |

| 伺服電機(jī) | SVPWM | 光伏發(fā)電 | UPS | AR | 智能電網(wǎng) | 國民技術(shù) | Microchip |

| Arduino | BeagleBone | 樹莓派 | STM32 | MSP430 | EFM32 | ARM mbed | EDA |

| 示波器 | LPC | imx8 | PSoC | Altium Designer | Allegro | Mentor | Pads |

| OrCAD | Cadence | AutoCAD | 華秋DFM | Keil | MATLAB | MPLAB | Quartus |

| C++ | Java | Python | JavaScript | node.js | RISC-V | verilog | Tensorflow |

| Android | iOS | linux | RTOS | FreeRTOS | LiteOS | RT-THread | uCOS |

| DuerOS | Brillo | Windows11 | HarmonyOS |