完善資料讓更多小伙伴認(rèn)識你,還能領(lǐng)取20積分哦,立即完善>

標(biāo)簽 > xilinx

Xilinx是全球領(lǐng)先的可編程邏輯完整解決方案的供應(yīng)商。Xilinx研發(fā)、制造并銷售范圍廣泛的高級集成電路、軟件設(shè)計工具以及作為預(yù)定義系統(tǒng)級功能的IP(Intellectual Property)核。

文章:1670個 瀏覽:124378次 帖子:5354個

Xilinx監(jiān)控系統(tǒng)開發(fā)人員面臨的挑戰(zhàn)

在本次網(wǎng)絡(luò)研討會中,Xilinx展示了高級監(jiān)控系統(tǒng)開發(fā)人員面臨的關(guān)鍵挑戰(zhàn),重點是何時在邊緣或云端本地化實時圖像處理。

2018-11-29 標(biāo)簽:圖像處理xilinx監(jiān)控系統(tǒng) 2836 0

Xilinx FPGA的復(fù)位:全局復(fù)位并不是好的處理方式

通常情況下,復(fù)位信號的異步釋放,沒有辦法保證所有的觸發(fā)器都能在同一時間內(nèi)釋放。觸發(fā)器在A時刻接收到復(fù)位信號釋放是最穩(wěn)定的,在下一個時鐘沿來臨被激活,但是...

FPGA開發(fā)要懂得使用硬件分析儀調(diào)試——ILA

其實這兒便很簡單了,可以直接在畫布上添加一個ILA核,再把想要的信號線連進(jìn)來就行了呀,都不需要在代碼里定義這個ILA核。不過這樣做就說明你還沒能靈活的使...

采用Xilinx技術(shù)/Pinnacle和安森美合作推出新的HDR監(jiān)控方案

在真實情況的測試下,新的方案捕獲和色調(diào)映射高對比度場景達(dá)120 dB或20 EV,全是全高清1080 p 30 fps實時輸出 Pinnacle Ima...

本文通過一個簡單的例子,介紹Vivado 下的仿真過程。主要參考了miz702的教程,同時也參考了Xilinx的ug937, xapp199.。

隨著智能安全、機器人或無人駕駛汽車等應(yīng)用越來越依靠嵌入式人工智能技術(shù)來提高性能,交付全新的用戶體驗,推斷引擎必須滿足嚴(yán)格定義的推斷精度,還受限于總線寬度...

浪潮聯(lián)合Xilinx發(fā)布全球首款集成HBM2的FPGA AI加速卡F37X

浪潮聯(lián)合賽靈思宣布推出全球首款集成HBM2高速緩存的FPGA AI加速卡F37X,可在不到75W典型應(yīng)用功耗提供28.1TOPS的INT8計算性能和46...

Xilinx Zynq UltraScale MPSoC可擴展電源設(shè)計

TIDA-01480 參考設(shè)計是一種可擴展的電源設(shè)計,旨在為 Xilinx Zynq UltraScale+ (ZU+) 系列 MPSoC 器件供電。此...

Xilinx Alveo U200數(shù)據(jù)中心加速器卡的主要性能和優(yōu)勢

啟用 Alveo 加速器卡是 Xilinx 及合作伙伴應(yīng)用的一個生態(tài)系統(tǒng),主要面向數(shù)據(jù)中心的工作負(fù)載。對于定制解決方案,Xilinx 應(yīng)用開發(fā)工具套件 ...

2018-10-14 標(biāo)簽:xilinx機器學(xué)習(xí) 6413 0

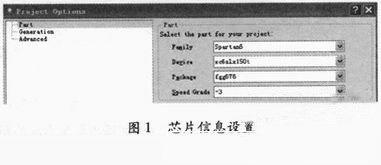

基于Xilinx FPGA用于ASIC前端驗證的問題總結(jié)

FPGA本身是有專門的時鐘cell的,以xilinx FPGA為例,就是primitive庫中的BUFG。

MIPI分為CSI(Camara sensor interface)與DSI(Display interface)

FPGA(Field Programmable Gate Array)于1985年由xilinx創(chuàng)始人之一Ross Freeman發(fā)明,雖然有其他公司宣...

初學(xué)Xilinx SDK的開發(fā),API函數(shù)筆記

初學(xué)Xilinx SDK的開發(fā),下面記錄使用到的API函數(shù)及自己的理解。若有誤,還請指教。 1、XScuTimer_Config *XScuTimer_...

基于Xilinx開發(fā)平臺和FPGA器件實現(xiàn)一維成像雷達(dá)目標(biāo)識別

目標(biāo)識別作為現(xiàn)代雷達(dá)的重要發(fā)展方向之一,成為未來武器系統(tǒng)中的一個重要組成部分和當(dāng)前國內(nèi)外關(guān)注的熱點,具有廣泛的民用和軍事應(yīng)用價值。根據(jù)雷達(dá)的探測手段及應(yīng)...

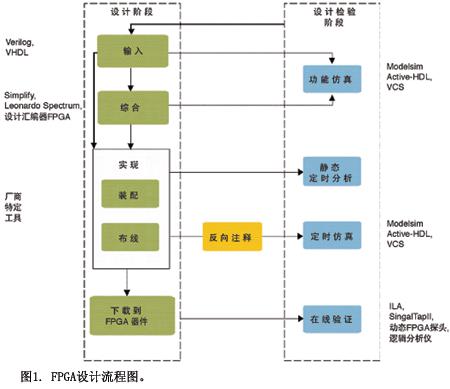

有助于提高FPGA調(diào)試效率的技術(shù)與問題分析

本文重點介紹在調(diào)試FPGA系統(tǒng)時遇到的問題及有助于提高調(diào)試效率的技術(shù),針對Altera和Xilinx的FPGA調(diào)試提供了最新的方法和工具。

集成式比特誤碼率測試儀的原理、功能及在FPGA芯片調(diào)試中的應(yīng)用

隨著高速數(shù)字系統(tǒng)的發(fā)展,高速串行數(shù)據(jù)被廣泛使用,內(nèi)嵌高速串行接口的FPGA也得到大量應(yīng)用,相應(yīng)的高速串行信號質(zhì)量的測試也越來越頻繁和重要。通常用示波器觀...

以Virtex5開發(fā)板和SPI FLASH為基礎(chǔ)的FPGA多重配置分析

Xilinx 公司Virtex5 系列的FPGA 具有多重配置的特性,允許用戶在不掉電重啟的情況下,根據(jù)不同時刻的需求,可以從FLASH 中貯存的多個比...

如何利用FPGA完成信號模擬和時序控制 實現(xiàn)雷達(dá)目標(biāo)模擬器設(shè)計

ADI公司是業(yè)界廣泛認(rèn)可的數(shù)據(jù)轉(zhuǎn)換和信號調(diào)理技術(shù)全球領(lǐng)先的供應(yīng)商,擁有遍布世界各地的60,000客戶,他們事實上代表了全部類型的電子設(shè)備制造商。ADI公...

2018-09-07 標(biāo)簽:fpga嵌入式系統(tǒng)Xilinx 9387 0

估計是之前裝過ISE14.7之后卸載,再裝Vivado 2015.3導(dǎo)致的問題;也可能是win8.1的問題,是我在win8.1中使的用戶名是中文的原因(...

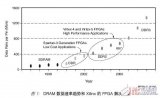

各種存儲器接口控制器設(shè)計所面臨的挑戰(zhàn)和Xilinx的解決方案詳解

FPGA 設(shè)計人員在滿足關(guān)鍵時序余量的同時力爭實現(xiàn)更高性能,在這種情況下,存儲器接口的設(shè)計是一個一向構(gòu)成艱難而耗時的挑戰(zhàn)。Xilinx FPGA 提供...

換一批

換一批

編輯推薦廠商產(chǎn)品技術(shù)軟件/工具OS/語言教程專題

| 電機控制 | DSP | 氮化鎵 | 功率放大器 | ChatGPT | 自動駕駛 | TI | 瑞薩電子 |

| BLDC | PLC | 碳化硅 | 二極管 | OpenAI | 元宇宙 | 安森美 | ADI |

| 無刷電機 | FOC | IGBT | 逆變器 | 文心一言 | 5G | 英飛凌 | 羅姆 |

| 直流電機 | PID | MOSFET | 傳感器 | 人工智能 | 物聯(lián)網(wǎng) | NXP | 賽靈思 |

| 步進(jìn)電機 | SPWM | 充電樁 | IPM | 機器視覺 | 無人機 | 三菱電機 | ST |

| 伺服電機 | SVPWM | 光伏發(fā)電 | UPS | AR | 智能電網(wǎng) | 國民技術(shù) | Microchip |

| Arduino | BeagleBone | 樹莓派 | STM32 | MSP430 | EFM32 | ARM mbed | EDA |

| 示波器 | LPC | imx8 | PSoC | Altium Designer | Allegro | Mentor | Pads |

| OrCAD | Cadence | AutoCAD | 華秋DFM | Keil | MATLAB | MPLAB | Quartus |

| C++ | Java | Python | JavaScript | node.js | RISC-V | verilog | Tensorflow |

| Android | iOS | linux | RTOS | FreeRTOS | LiteOS | RT-THread | uCOS |

| DuerOS | Brillo | Windows11 | HarmonyOS |