完善資料讓更多小伙伴認識你,還能領取20積分哦,立即完善>

電子發燒友網技術文庫為您提供最新技術文章,最實用的電子技術文章,是您了解電子技術動態的最佳平臺。

首先按照GitHub 說明在虛擬機上安裝依賴項,然后創建一個新的存儲庫目錄并克隆了 pico-SDK 和 XVC-Pico 項目。...

在一些攝像頭中,pwdn管腳和rst管腳有時會直接省略掉。pwdn管腳為電源掉電模式管腳,低電平表示為正常模式,高電平表示掉電模式。使用時,將pwdn管腳置為低電平即可。...

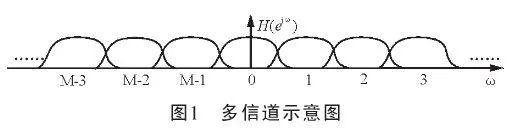

在數字接收機的各種參數中,頻率是重要的參數之一,它能反映接收機的功能和用途、以及頻譜寬度等重要指標。...

本文主要用來隨意記錄一下最近在為手頭的FPGA項目做約束文件時候遇到的一點關于FPGA專用時鐘管腳相關的內容,意在梳理思路、保存學習結果、以供自己日后以及他人參考。...

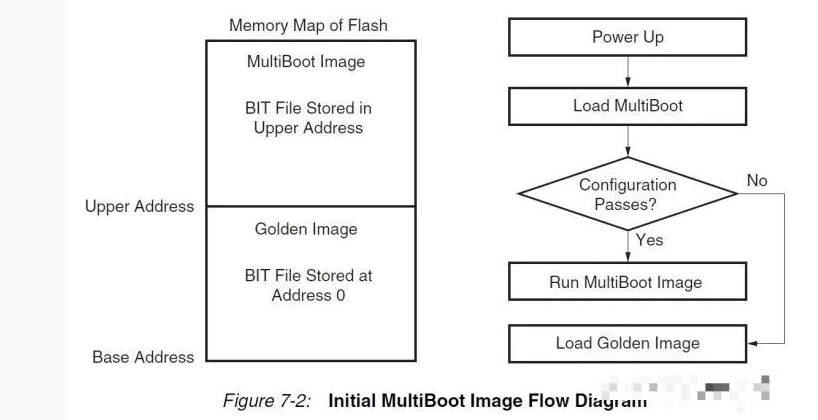

在遠程更新的時候,有時候需要雙鏡像來保護設計的穩定性。在進行更新設計的時候,只更新一個鏡像,另一個鏡像在部署之前就測試過沒問題并不再更新。當更新出錯時,通過不被更新的鏡像進行一些操作,可以將更新失敗的數據重新寫入Flash。這樣即使更新出錯,也能保證設計至少可以被遠程恢復。...

由Binary Pointer生成Gary Pointer,其實這里根據經典AFIFO論文[1]里應該是用新的wptr_bin_next生成wptr_gray_next,這樣wptr_bin和wptr_gray可以同步更新。...

雙沿時鐘使得原本一個周期輸出/輸入一個數據的架構,改變為一個周期輸出/輸入兩個數據,這樣在不升高時鐘頻率的前提下,提升了信號的吞吐率,從而帶來「性能的提升」。...

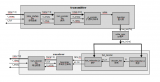

FPGA可重構技術就是通過上位機控制在FPGA運行過程中加載不同的Bitstream文件,FPGA芯片根據文件內的不同邏輯將內部的資源全部或部分進行重新配置以達到多種功能任務動態切換的目標,從而提高了使用FPGA進行開發的靈活度。...

在FPGA處理完數字信號之后,我們有些情況下是需要將數字信號轉變為模擬信號再輸出的。比如音頻信號在濾波后,需要轉換為聲音信號進行輸出。...

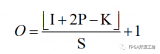

HLS需要bit-reverse命令數據塊后端,所說的自然順序和一個O (N)轉換適用于FFT輸出提取的頻譜數據N-point真實數據集。注意,第一個輸出兩包第0個和512(純粹的)分別輸出頻譜數據的實部和虛部。...

亞穩態這種現象是不可避免的,哪怕是在同步電路中也有概率出現,所以作為設計人員,我們能做的是減少亞穩態發生的概率。...

首先是對 SQL 的支持,比如是否支持 IC SQL,還是會違背 IC SQL 的語法,有很多自己的 SQL 語法。引申就是有沒有一些 MySQL 協議或者是 PG 協議,直接可以去對接更好的 BI 工具,能夠較少地去改動。...

一般來說,我們認為CMOS數字電路的輸出的穩定狀態只有2種,就是邏輯0和邏輯1,從模擬信號量來說,就是0V和VDD。...

FPGA 設計工程師需要對如何創建系統以及使用行業軟件和工具有深入的了解。在軟件方面,設計工程師必須知道如何建模自己的設計,并通過一系列測試保證正確的運行。業界有許多這種高級建模程序,包括Matlab,Simulink,Octave,Verdi等等。...

真實數據是保存在較長的一行。分析后可以看到較長行的長度都是一樣的。具體內容是,前端若干位是控制符(包含地址),然后是具體數據,之后是校驗碼。找到規律后,就可以直接提取其中內容了。...

擴頻系統最早可以追溯到20世紀20年代左右,擴頻通信就有了初步的應用。但是一直到20世紀年代中期,擴頻系統才真正應用和發展起來。...