近年來,消費(fèi)電子和個人計算市場的發(fā)展增加了對于更強(qiáng)大且高度集成的芯片產(chǎn)品的需求。低成本、低功耗、復(fù)雜功能和縮短上市時間的需要,讓越來越多的IC設(shè)計采用了SoC技術(shù)。

在這些SoC電路中,由于包含了數(shù)據(jù)轉(zhuǎn)換器、功率管理及其它模擬電路,混合信號設(shè)計不可避免并且越來越多。在混合信號SoC設(shè)計中,為了避免芯片重制,確保一次性流片成功,全芯片混合信號驗(yàn)證成為關(guān)鍵一環(huán)。傳統(tǒng)上,在復(fù)雜的混合信號SoC設(shè)計中,不同團(tuán)隊(duì)分別獨(dú)立驗(yàn)證數(shù)字和模擬組件,并不進(jìn)行全芯片綜合驗(yàn)證,其主要原因是沒有足夠強(qiáng)大的EDA工具能夠完成這個重要任務(wù)。如果所有的集成和接口問題僅僅是在測試平臺中進(jìn)行解決,那么就很難保證混合信號的正確連接和時序匹配。隨著高速SPICE模擬工具的出現(xiàn),設(shè)計師可以在晶體管級執(zhí)行整個芯片系統(tǒng)的驗(yàn)證,這是一種較為有效的驗(yàn)證方法。該方法具有很高的精確性,并能夠進(jìn)行全面的功能分析,但是,此類驗(yàn)證只能在設(shè)計周期的最后階段進(jìn)行,那時所有的單元和定制元件都已經(jīng)設(shè)計完成。此外,這種方法的模擬速度有時非常緩慢,必須動用大量的硬件資源。對于包含微處理器、ROM、RAM、PLL等的復(fù)雜系統(tǒng),由于其元件數(shù)量實(shí)在過于龐大,高速SPICE模擬器幾乎不可能執(zhí)行全芯片晶體管級模擬。

然而,驗(yàn)證方法學(xué)應(yīng)該貫穿于整個設(shè)計階段,而不能僅局限于最終的驗(yàn)證階段。同時,為了實(shí)現(xiàn)混合信號SoC驗(yàn)證在精確性和速度之間的完美平衡,設(shè)計師可能想要保持某些重要的模擬模塊(如ADC、PLL)作為SPICE網(wǎng)表,而其它部分為Verilog行為級模塊。這時,設(shè)計師可以選擇使用晶體管級電路去替代特定的行為模塊,并及時高效地繼續(xù)設(shè)計驗(yàn)證過程。

為了實(shí)現(xiàn)精確而快速的全芯片驗(yàn)證,全新的模擬解決方案應(yīng)運(yùn)而生。

AMS Designer與AMSVF

作為新一代的模擬器,AMS Designer基于Virtuoso Spectre和Ultrasim Simulator以及Incisive Unified Simulator引擎的可靠技術(shù),是一種單一核心(Single Kernel)的混合信號模擬器。它提供了兩種模擬求解器——Spectre和Ultrasim,并支持幾乎所有的語言和SPICE網(wǎng)表規(guī)格。Ultrasim求解器性能較高,有著堪比SPICE的精確性,并且容量幾乎無限,因此較適合大型全芯片設(shè)計。

雖然AMS Designer為DFII流程提供了友好的圖形用戶界面,然而對于混合信號驗(yàn)證,多數(shù)設(shè)計師更需要該應(yīng)用在命令行模式下執(zhí)行全芯片驗(yàn)證。其原因不僅是因?yàn)槊钚心J教峁┝藦?qiáng)大而方便的批量運(yùn)行功能,還因?yàn)樵O(shè)計本身是基于沒有原理圖的文本文檔,或沒有GUI環(huán)境。對于這種應(yīng)用方式,AMSVF(AMS驗(yàn)證流程)更加適合。

AMSVF的應(yīng)用模式

繼承了NC-Verilog,AMSVF的使用支持ncverilog單步模式,它主要面向Verilog-XL用戶;而3步模式會調(diào)用ncvlog剖析輸入文件,調(diào)用ncelab構(gòu)建電路結(jié)構(gòu),然后調(diào)用ncsim模擬器模擬電路。

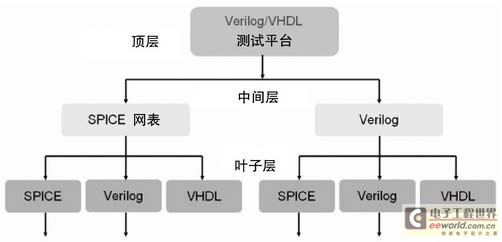

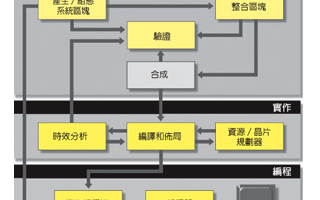

目前,AMSVF可以為數(shù)字測試平臺提供支持,其應(yīng)用模式如圖1所示。

圖1 AMSVF的應(yīng)用模式

Verilog/VHDL頂層也可以例示SPICE subckt,對于VHDL測試平臺來說,需要提供Verilog wrapper。另外,頂層可以調(diào)用其它Verilog/VHDL模塊。這種應(yīng)用模式被命名為“Verilog on top”。中層SPICE subckt也可以例示最底層的Verilog/VHDL模塊,這種應(yīng)用模式被命名為“Sandwich”或“SPICE in middle”。另外,在一些復(fù)雜設(shè)計中,AMSVF還支持多個“Sandwich”應(yīng)用模式,如“Verilog - SPICE - Verilog - SPICE - Verilog”。

這兩種應(yīng)用模式對于用戶的全芯片驗(yàn)證應(yīng)用是非常方便的。對于一個純粹的數(shù)字系統(tǒng)設(shè)計,為了獲得精確的結(jié)果,用戶可以用SPICE網(wǎng)表替代一些Verilog模塊,甚至使用寄生參數(shù)以獲得更為精確的模擬結(jié)果。由于物理元件太多,模擬速度可能會變慢,這時,用戶可以在SPICE網(wǎng)表中對基本門電路使用Verilog/VHDL行為級模塊。那么,“Sandwich”應(yīng)用模式就得以實(shí)現(xiàn)。這意味著用戶可以自由而簡單地切換應(yīng)用模式。

?????AMSVF的應(yīng)用與重要功能

AMSVF中有許多實(shí)用而重要的功能,其中某些功能可用于減少建立測試用例所需的手工時間,而另外一些功能可用于驗(yàn)證性能。

自動總線連接

在HDL語言中,總線信號的使用非常普遍且不可或缺。但SPICE中并沒有類似的概念或定義,連接到SPICE支電路的Verilog總線必須被分解到每一個單獨(dú)的端口,而且必須按順序連接。例如:

module verilog;

wire [0:5] v;

analog_top xana_top ( v[0], v[1], v[2], v[3], v[4], v[5] );

endmodule

.subckt analog_top p<0> p<1> p<2> p<3> p<4> p<5>

...

.ends

為了準(zhǔn)確地連接Verilog實(shí)例和SPICE subckt,總線信號v[0:5]必須被分離。通常,分離的過程需要極為耗時的手動編輯,尤其對于規(guī)模較大的總線更是如此。而在AMSVF中,通過自動總線連接功能,用戶可以輕松地將實(shí)例寫為:

analog_top xana_top ( v );

用戶可以在SPICE網(wǎng)表中設(shè)置總線界定符,告知AMSVF哪個符號用于總線信號。這里符號<> 和[ ]為默認(rèn)界定符,甚至也可以支持空總線界定符。

AICM與BDR

AMS Designer嚴(yán)格遵從Verilog AMS的規(guī)范確定(Discipline Resolution)過程,它讓用戶可以依靠工具確認(rèn)信號間的連通性,并能實(shí)現(xiàn)連接模塊的自動插入。

AICM(自動插入連接模塊)算法判定通過未聲明端口相連的線網(wǎng)規(guī)范,然后在模擬和數(shù)字域邊界上插入連接模塊。除了電氣到邏輯(E2L)以及邏輯到電氣(L2E)這兩個普通的連接模塊外,AICM還支持雙向的連接模塊,這對于不想明確指定線網(wǎng)端口方向的用戶來說是非常方便的。

在驗(yàn)證大規(guī)模設(shè)計時,尤其是在ncelab階段,新的BDR(鎖定規(guī)范確定)功能能夠讓設(shè)計師應(yīng)用他們的設(shè)計知識去控制并縮小規(guī)范確定的解析范圍以提升性能。此外,如果通過AMSVF驗(yàn)證的設(shè)計在數(shù)字和模擬之間有清晰的界限,或其所有線網(wǎng)都已被明確地聲明,那么,利用“-disres none”選項(xiàng)甚至可以跳過規(guī)范確定過程,顯著縮短運(yùn)行時間。因此,這種新功能可以大幅提高AMSVF在ncelab階段的性能和效率。

此外,BDR對于多電源設(shè)計來說是非常實(shí)用的。例如,對于同時使用5V、3.3V和1.8V供應(yīng)電源的電路來說,當(dāng)數(shù)字模塊用不同的供應(yīng)電源連接模擬模塊時,數(shù)字信號將會有不同的數(shù)字規(guī)范,如logic5V、logic33V 和logic18V,而對于單電源設(shè)計來說,僅用缺省的logic這一個數(shù)字規(guī)范即可。因此通過這種功能,用戶可以為設(shè)計中的數(shù)字模塊設(shè)定不同的數(shù)字規(guī)范,以便模擬器更加準(zhǔn)確地插入連接模塊。

Stub View

Stub View提供了從模擬中移除原理圖或Verilog AMS模塊的途徑。通過移除不影響模擬結(jié)果或是沒有使用到的模塊,可以幫助用戶加快模擬速度。另外,該功能可以用于確認(rèn)哪個模塊是造成模擬速度降低的主要原因。

比如,電路中包含有不同激勵源的3個通道,每個通道彼此獨(dú)立,利用Stub View功能移除其中的一或兩個通道,就可以大幅加快模擬速度。

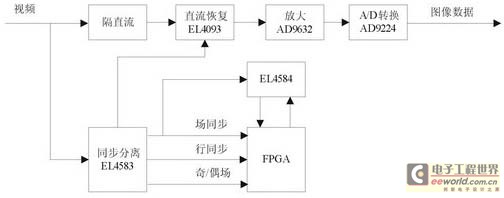

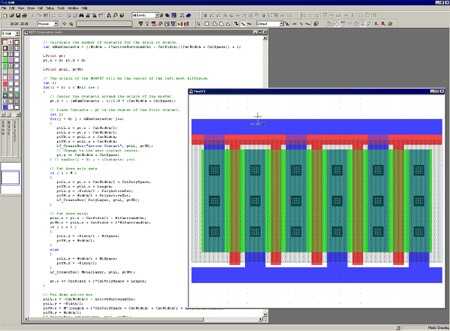

UPS求解器

一般來說,電源/地線網(wǎng)絡(luò)中存在大量的寄生RC,在版圖后仿真時,這些寄生RC將會大大降低性能,并侵占大量內(nèi)存。對于這類模擬,AMSVF中的UPS求解器可被用于加速模擬速度,同時保持精確性。模擬器首先偵測電源網(wǎng)絡(luò),然后將整個設(shè)計分離為電源網(wǎng)絡(luò)和信號網(wǎng)絡(luò)兩部分。電源網(wǎng)絡(luò)部分由UPS求解器處理,而信號網(wǎng)絡(luò)部分則由Ultrasim求解器處理。電源網(wǎng)絡(luò)模擬的示意圖如圖2所示。

圖2 電力網(wǎng)絡(luò)模擬法示意圖

使用傳統(tǒng)的瞬態(tài)模擬和UPS求解器分別進(jìn)行電壓降分析的性能對比如表1所示。

????? VR技術(shù)

由于芯片內(nèi)電源電壓不斷降低,并開始采用多電源電壓,因此,越來越多的混合信號/RF或數(shù)字電路均使用片上穩(wěn)壓器來產(chǎn)生內(nèi)部供電電壓。Ultrasim求解器通過有效的分區(qū)技術(shù)實(shí)現(xiàn)模擬加速,但這只能應(yīng)用在電路由理想電源電壓驅(qū)動的情況下。使用傳統(tǒng)的分區(qū)技術(shù),所有連接到內(nèi)部穩(wěn)壓源的模塊都必須包含在單個分區(qū)內(nèi),嚴(yán)重影響了模擬速度。

VR(穩(wěn)壓)技術(shù)能夠克服這種限制, 讓用戶能夠方便地對由內(nèi)部穩(wěn)壓器供電的電路模塊進(jìn)行模擬仿真。

快速包絡(luò)分析

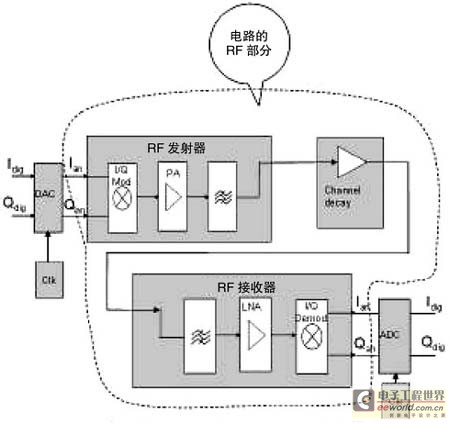

總的來說,當(dāng)被調(diào)制電路采用傳統(tǒng)的瞬態(tài)分析時,需要非常小的時間步長以適應(yīng)高頻載波信號,并且需要長時間的持續(xù)周期覆蓋低頻基帶信號,這將使得模擬變得非常緩慢和困難。快速包絡(luò)分析主要用于解決這個難題,這些電路類型通常出現(xiàn)在發(fā)射器、接收器等RF電路中。

AMSVF的快速包絡(luò)分析功能提供了對模擬/混合信號電路進(jìn)行模擬和設(shè)計的有效方法。任何包含已調(diào)制信號的電路或RF部分都可以通過快速包絡(luò)分析法進(jìn)行模擬,而電路的其它部分則由數(shù)字求解器或傳統(tǒng)的瞬態(tài)模擬法進(jìn)行仿真。包括數(shù)字和模擬電路在內(nèi)的所有仿真都在每個時間步長進(jìn)行同步,它考慮了各仿真之間的耦合,并確保解決方案的精確性。快速包絡(luò)分析可以跳過時鐘周期中的很多時點(diǎn),減少大量的時間步長數(shù),簡化計算量。

以圖3中完整的RF電路為例,它包含了發(fā)射器、接收器和ADC/DAC Verilog-AMS模塊。與瞬態(tài)分析相比,快速包絡(luò)分析可以通過極小的精確性損失讓性能提高7倍。兩種方法的波形對比如圖4所示,來自快速包絡(luò)的最后一個波形跳過了很多周期。

圖3 完整的RF電路和ADC/DAC行為模塊

結(jié)語

AMSVF已經(jīng)被證明是一種針對復(fù)雜混合信號電路進(jìn)行全芯片驗(yàn)證的有效而強(qiáng)大的工具。它不僅提供了靈活的應(yīng)用模式,還包括更加先進(jìn)而強(qiáng)大的功能,能夠幫助更多的用戶在設(shè)計的初期階段發(fā)現(xiàn)設(shè)計錯誤,縮短設(shè)計周期,實(shí)現(xiàn)一次性流片成功。

電子發(fā)燒友App

電子發(fā)燒友App

評論