【在此特別鳴謝原文作者邵亞利】【芯人類】EDA 是芯片之母是IC 設計最上游、最高端的產(chǎn)業(yè)。也是中國集成電路產(chǎn)業(yè)最薄弱的環(huán)節(jié)。為向集成電路專業(yè)師生和從業(yè)者中系統(tǒng)介紹EDA技術(shù)的前沿進展,芯人類將分多期全文引入《電子報》EDA前沿技術(shù)專欄。專欄特邀行業(yè)多位專家,全面系統(tǒng)地介紹國內(nèi)外EDA 的狀況和國產(chǎn)EDA 的發(fā)展。本文為電子報授權(quán)發(fā)表。包含混合SOC的設計,驗證和實現(xiàn)的方法流程三方面內(nèi)容,并重點介紹了驗證所需要了解的仿真器原理,和行為級建模相關(guān)的知識。共分三次發(fā)表。

片上系統(tǒng)(SOC)混合信號含量越來越高

集成電路從模擬電路開始,后來數(shù)字電路蓬勃發(fā)展,而今為了能夠滿足多種場合的不同復雜應用,例如高集成/低成本/可移動/多接口等要求,混合信號片上系統(tǒng)SOC(System On Chip)日益流行。SOC中的數(shù)模混合信號含量已經(jīng)從10%~20%增加到50%或更高。

例如,在以數(shù)字為主的SOC中,離不開連接真實世界的ADC(Analog-to-Digital-Converter),DAC(Digital-To-Analog-Converter),還有提供高速時鐘的PLL(Phase-Locked-Loop)以及射頻收發(fā)器,存儲器接口等。在以模擬為主的SOC中,也增加了Control/Trim/Calibration等數(shù)字邏輯,來補償PVT(Process, Voltage, Temperature)的變化,提高性能指標和良率。數(shù)模電路甚至在不同層次中緊密結(jié)合。

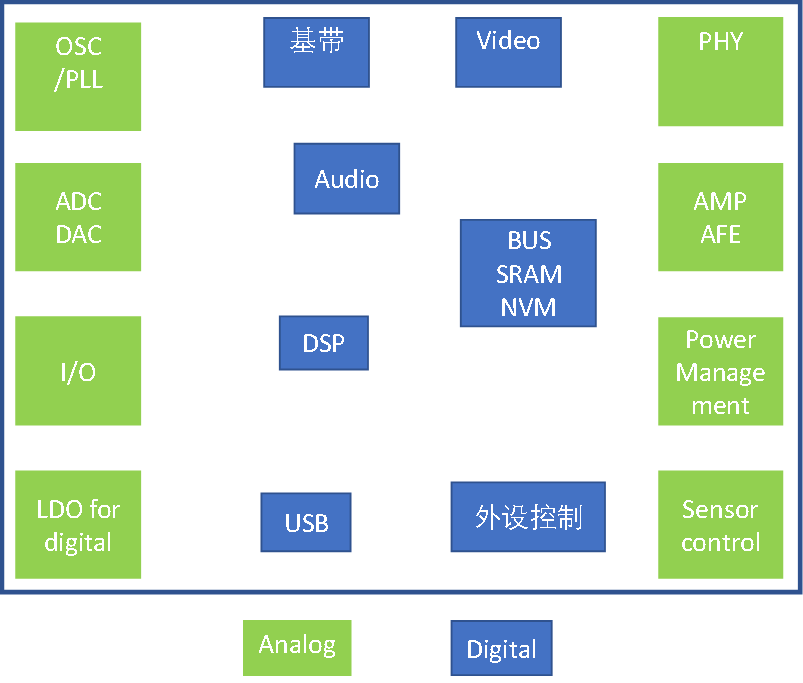

圖1 混合信號SOC典型框圖

這張圖是一顆混合SOC芯片,藍色部分是數(shù)字部分,通常有微處理器、基帶(BB)、總線、SRAM (緩存,或者叫內(nèi)存)、有NVM(非易失性存儲器),比如說像FLASH、EEPROM,或者OTP,還有Video, Audio, USB,以及外設的一些接口控制電路,像SPI、I2C、HDMI接口或者UART、GPIO、PWM控制等。

綠色部分是模擬或者模擬為主的混合模塊,通常有OSC/PLL振蕩器,有作為數(shù)字和外界的窗口ADC或者DAC,有邏輯控制的GPIO作為通用的I/O接口,為了給數(shù)字電路供電有LDO,因為數(shù)字電路需要比較穩(wěn)定的電源。

右邊第一個是PHY,是協(xié)議物理層,通常它本身也是一個數(shù)模混合的模塊,它既有數(shù)字電路也有模擬電路,把它放在這里就表示需要模擬工程師對它進行重點的關(guān)注。還有作為對微弱信號處理的放大器和模擬前端AFE(Analog Front End),AFE將模擬信號經(jīng)過放大處理,把它輸入到ADC或者數(shù)字電路當中。Power Management是經(jīng)常會用到的一個模塊,包括BUCK,BOOST或Charge Pump等模塊,另外就是傳感器的控制電路。前面這幾個模塊每個芯片都不一樣,有可能有,有可能沒有。但是左邊這一列,基本上每個SOC芯片都會有。

數(shù)模混合SOC設計常用流程與工具

既然數(shù)模混合SOC市場需求越來大,那么如何設計與實現(xiàn)一款混合SOC呢?本章節(jié)主要探討數(shù)模集成電路設計常用的流程與工具。

1.以數(shù)字為主的SOC設計流程

常用文檔編輯工具,從高級描述開始,采用Verilog, System Verilog或者C語言,去設計數(shù)字電路并制作Test Bench(TB)和層次化的模型,再用仿真工具去仿真模型,然后通過標準單元庫,自動綜合成門級電路,生成網(wǎng)表,再對網(wǎng)表進行布圖并生成三個文件(GDS、Netlist和Timing信息的SDF),設計告一段落。

在驗證階段需要模擬的Model,供數(shù)字控制模擬或者模擬返回到數(shù)字的模擬驗證。也需要固件的二進制碼供給TB對SOC進行仿真。

2.以模擬為主的SOC設計流程

區(qū)別于寫代碼,模擬IC設計通常是以電路圖來做設計,電路圖中包括電阻電容/MOS管等基本元件,和相關(guān)拓撲連接關(guān)系。模擬工程師通常先設計子模塊,電路圖的頂層則是由一個模擬頂層的線路圖和一個空的數(shù)字模塊構(gòu)成。

頂層仿真開始階段用Digital的RTL的IP模塊和Firmware組合,加之模擬電路,進行Analog On Top的仿真。仿真驗證通過后,RTL進行PR,再由Schematic Verilog-in組成最終頂層的線路圖,結(jié)合數(shù)字的SDF的Timing約束,完成PR后的仿真。

從后端看,頂層仿真后進行Analog layout將等在Digital PR完成,然后Stream-in進來一起形成TOP的Layout,即使有些IP可能不會給底層的GDS,通過Phantom View形成TOP的Layout,再對它進行LVS。

3.數(shù)模集成電路設計的常見工具

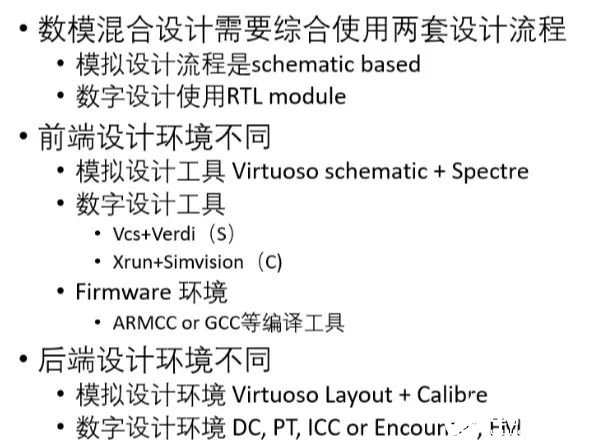

圖2 數(shù)模混合設計與實現(xiàn)的常見工具

數(shù)模混合驗證需要在頂層同時整合兩套設計流程。模擬工程師熟悉的流程是Schematic Based,數(shù)字設計師使用RTL module。

通常熟悉Cadence Virtuoso schematic + Spectre的是模擬設計者。數(shù)字設計工具Synopsys用VCS+Verdi,Cadence用的是Xrun+Simvison,此外還要搭建Firmware的設計環(huán)境。當然,寫程序和編譯還要用到ARM CC或者像GCC之類的工具。

后端設計,模擬往往用Virtuoso Layout,再加上Calibre,做LVS和DRC;數(shù)字設計要用DC綜合,時序分析PT(Prime Time),布圖用ICC(或Encounter),還有FM(形式驗證),Patten(測試矢量的自動生成)工具。

4.數(shù)模混合SOC并行協(xié)同設計流程

公開的/工業(yè)標準的數(shù)據(jù)庫的出現(xiàn),例如Open Access(OA),對數(shù)模混合SOC方法學的開發(fā)與應用做出了重要貢獻。OA是一種層次化的數(shù)據(jù)庫,能同時存儲數(shù)字和模擬,從而不需要將數(shù)據(jù)從一種格式轉(zhuǎn)換到另外一種格式。公共數(shù)據(jù)庫是同步混合信號設計的基本要求,否則在以前單獨的模擬或者數(shù)字方法學中,每個區(qū)域?qū)Ψ蕉远际呛诤凶樱头浅H菀壮鲥e,甚至是低級錯誤,因為復雜的功能,不同的Background, 模糊的“Common Sense”,都增加了芯片出bug的風險,一些簡單錯誤可能會導致很嚴重的后果,例如功能不正常,過長的流片后的debug時間,昂貴的再流片成本,更重要的是Delay的研發(fā)周期,錯失的市場窗口。

通過OA數(shù)據(jù)庫的支持,數(shù)字和模擬之間完全透明,從而誕生了數(shù)模混合并行協(xié)同設計的流程,它可以同時汲取數(shù)模流程中的優(yōu)點,回避其缺點,從而最高效率地設計混合SOC。

以下表格對比和總結(jié)了以上三種數(shù)模混合IC的設計驗證與實現(xiàn)流程。

表1 數(shù)模混合IC的設計/驗證/實現(xiàn)流程

混合SOC驗證的挑戰(zhàn)與方法介紹

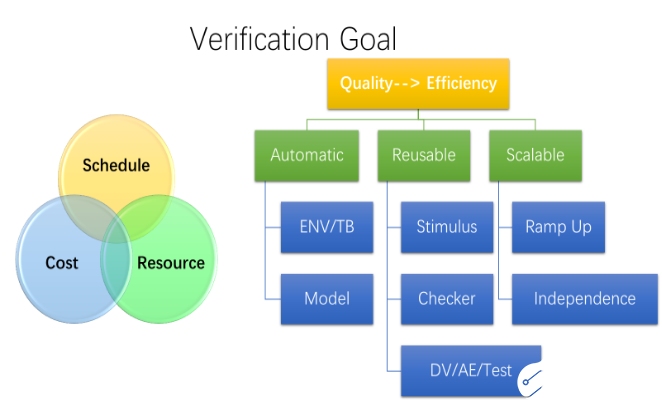

驗證是在流片前,保證芯片的設計滿足客戶應用的指標要求。數(shù)模混合SOC的驗證面臨很多挑戰(zhàn),Time To Market的壓力,芯片的研發(fā)周期Schedule在不斷被壓縮,成本也越來越低,且IC人才又相對有限。驗證更需要一些對應的技巧與流程規(guī)范來達到驗證目的。

一個好的驗證,需要達到什么目的呢?首先是最起碼保證芯片的質(zhì)量,以便First Silicon Sample。在保證質(zhì)量的基礎上,需要提高效率。主要有三個維度:首先是Automatic,如何讓驗證環(huán)境自動化產(chǎn)生,Test Bench自動產(chǎn)生,甚至Model自動產(chǎn)生等;其次是Reusable,例如Stimulus,Checker等,又或是DV/AE(Application Engineer)和TE(Test Engineer)之間的Reuse。第三是Scalable,高度集成的數(shù)模混合驗證,通常需要很多人參與。如何讓新資源快速的Ramp Up起來縮短適應時間;這么多人工作在同一個項目上,且做到彼此不相互影響,不Block Other’s work, 那就更需要驗證環(huán)境和整個流程的分配協(xié)調(diào),從而保證大家能夠“各自為戰(zhàn)”。

圖3 驗證目標

1.混合SOC驗證的挑戰(zhàn)

混合信號設計的復雜度急劇增長,促使設計隊伍需要各種技能的工程師緊密合作;隨工藝尺寸變小,需要電路抽象級別更高,以便在系統(tǒng)級進行分析和驗證;為縮小數(shù)模之間的設計差距,需要更多采納軟硬件結(jié)合的自動化方法;數(shù)模之間數(shù)據(jù)交互,需要EDA工具和設計方法學支持,以加速數(shù)模混合驗證的收斂。但是正如上文所述,數(shù)字模擬IC采用了不同的設計流程和工具,加之SOC復雜的功能性能要求,然而模擬工程師和數(shù)字工程師的背景卻很不相同,任何一個環(huán)節(jié)出錯,都可能造成嚴重的后果。

圖4數(shù)模混合設計驗證的挑戰(zhàn)

圖4列出來了目前公認的混合信號SOC所面臨的挑戰(zhàn):模擬Spice/Fast Spice在復雜的SOC系統(tǒng)中仿真速度顯然不夠快,使得如果用最精確的模擬仿真會嚴重影響研發(fā)周期。晶體管-門級協(xié)同混合仿真比全Spice仿真要快,但是依然比較慢。對模擬電路去創(chuàng)建模型,則需要人才儲備,知識積累,以及模型開發(fā)與驗證時間。這是混合IC驗證面臨的前三大挑戰(zhàn)。另外還有缺乏模擬混合設計驗證IP,功耗意圖,為覆蓋率(Coverage)產(chǎn)生測試向量,軟硬件協(xié)同驗證等挑戰(zhàn)。

另外物聯(lián)網(wǎng)在低功耗方面的要求越來越高。造成芯片測試成本超過硅片本身,可測性設計就應該在設計過程中考慮。為此在保證正常功能與性能不降低的同時,增加片內(nèi)自建的測試電路(Scan,IDDQ等),會使芯片尺寸增大10%左右,加上冗余修復等電路,都為提高產(chǎn)品品質(zhì)和Debug提供了良好的基礎,但也增大了數(shù)模混合的驗證難度,因為不僅要驗證正常功能,還需要驗證可測試性功能。

2.混合SOC驗證的方法流程

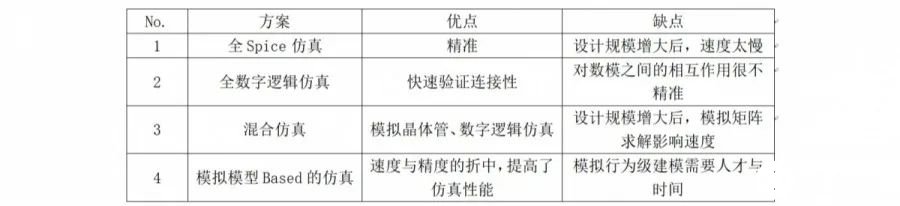

為了模擬和數(shù)字仿真同步的、平行的運行,解決混合信號驗證的問題,有以下幾項選擇方案:

表2 混合SOC仿真驗證方案

顯然這四種方案各有優(yōu)缺點,經(jīng)常需要幾種方案交互使用。這就誕生了基于Model的驗證方法,以及層次化的驗證技巧。

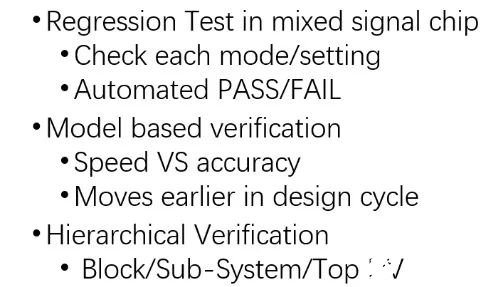

行為建模使得仿真在速度與精度之間做了非常好的折中,極大的提高了仿真效率;而且也能夠讓驗證在項目的早期就介入其中,與設計并行,縮短整體研發(fā)周期。所以接下來本文第五部分將重點介紹Model知識。

層次化的驗證方法,是將Block級設計者與驗證者的工作,納入了整體驗證考量因素之中。哪些性能指標是應該在Block級進行驗證,無須在Sub-System再驗證,是需要有經(jīng)驗的工程師進行驗證規(guī)劃的。層次化的驗證,重點強調(diào)每個級別上驗證的側(cè)重點的不同,使其形成一種整體的互補策略。同時也在層次化的Reuse驗證部分的相同環(huán)節(jié),減少Test Case 中Stimulus與Checker的創(chuàng)建。

圖5數(shù)模混合SOC驗證的方法

芯片的PVT變化,加之數(shù)字Random的概念,要求混合SOC必須做Regression測試,以便能夠遍歷所有的Mode和Setting,同時自動化的檢查PASS或者FAIL的仿真結(jié)果,以應對設計變化時候的快速驗證迭代。基于覆蓋率Coverage和斷言Assertion的指標驅(qū)動驗證(MDV),是數(shù)模混合驗證的重要內(nèi)容。這在純數(shù)字驗證中,已經(jīng)作為Sign Off標準。數(shù)字覆蓋率主要有代碼覆蓋率,有限狀態(tài)機覆蓋率,功能覆蓋率和結(jié)構(gòu)覆蓋率。混合信號的覆蓋率通過采用數(shù)據(jù)分級(bin)的概念,將連續(xù)的電壓電流等模擬值,轉(zhuǎn)換為離散的用戶自定義的范圍,從而實現(xiàn)覆蓋率的概念。斷言Assertion,就是捕捉設計的預期行為,來判斷數(shù)模混合屬性是否滿足Spec需求。標準的Assertion語言有PSL和SVA。為了滿足混合信號,IC標準委員會正在致力于模擬SVA(ASVA)和System-Verilog的AMS(SV-AMS)。

FPGA驗證對于驗證數(shù)字模塊有用,簡單的數(shù)字模塊仿真能夠覆蓋。復雜的數(shù)字模塊,比如有上位機軟件互動等,可以有效減少仿真驗證工作量。對于提前開發(fā)軟件、燒錄工具、自動測試有幫助。對于數(shù)模混合部分,F(xiàn)PGA驗證環(huán)境很難搭建。形式驗證和硬件加速目前還沒有針對模擬電路大量使用。所以以模擬為主的混合SOC主要以仿真驗證為主。

數(shù)字驗證已經(jīng)有了比較流行的UVM(Universal Verification Methodology)方法學,混合信號領域的UVM-MS方法擴展包括模擬模塊的驗證計劃,模擬信號的產(chǎn)生,模擬屬性的檢查和斷言技術(shù),以及模擬功能覆蓋的分析。

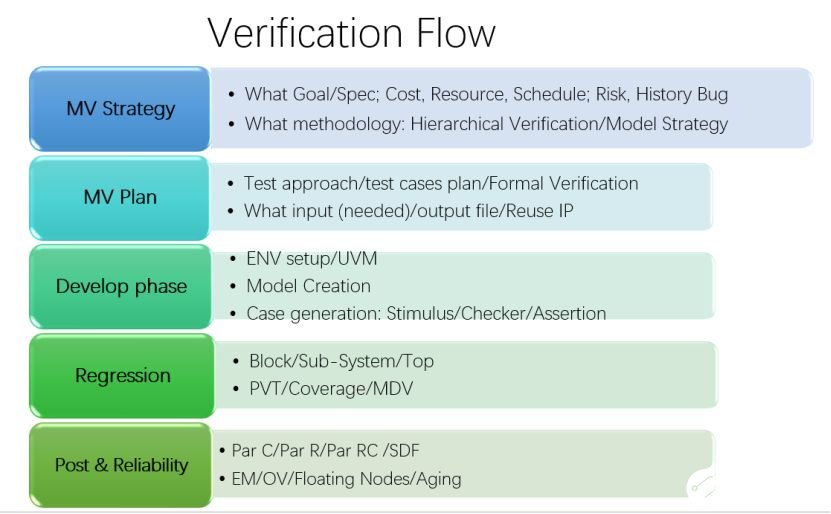

圖6 驗證流程介紹

最后,從項目研發(fā)進度的角度談一下驗證的流程。在項目剛開始階段,需要考慮混合驗證的策略(Strategy),主要包括驗證目標是什么,客戶要求Spec有哪些,項目周期,開發(fā)人員數(shù)量與技能等。項目風險在哪里,以前類似產(chǎn)品有哪些Bug。在方法學上采用自上而下與自下而上的結(jié)合么?怎么樣做層次化的驗證?建立Model的策略是什么?

清楚了策略之后,就需要開始具體制定驗證計劃。包括驗證需要哪些Input File,哪些Output result,采用什么樣的驗證工具與手段,是否需要形式驗證等。哪些通過RTL進行,哪些需要通過混合仿真,哪些需要通過晶體管仿真進行。

制定完計劃后就是具體的實施階段。主要包括驗證環(huán)境(ENV)的搭建,UVM的引入,基于Model驗證的Model本身的創(chuàng)建,以及Test Case所涉及的Stimulus,Checker與Assertion。

當Test Case建立完成以后,就需要開始跑Regression,分析Coverage,做MDV驗證。

最后還要做一些后仿真。模擬的寄生R,C,的仿真,數(shù)字基于SDF的門級仿真。也需要做一些和可靠性相關(guān)的檢查,例如電子遷移EM,過壓OV,浮點Floating Nodes,與老化Aging等檢查。

【在此特別鳴謝原文作者邵亞利】

作者簡介

邵亞利,模擬混合信號設計驗證專家。浙江大學本碩,“模擬混合信號設計驗證”公眾號(yaliDV)創(chuàng)始人。曾就職于德州儀器(TI),現(xiàn)就職于亞德諾(ADI)半導體公司。ADI(Analog Devices) 是全球領先的高性能模擬技術(shù)公司,憑借杰出的檢測、測量、電源、連接和解譯技術(shù),搭建連接現(xiàn)實模擬世界和數(shù)字世界的智能化橋梁。

責任編輯:pj

-

soc

+關(guān)注

關(guān)注

38文章

4356瀏覽量

221939 -

數(shù)模混合

+關(guān)注

關(guān)注

0文章

24瀏覽量

9404 -

LVS

+關(guān)注

關(guān)注

1文章

38瀏覽量

10152

發(fā)布評論請先 登錄

工程師不得不懂的MCU混合信號驗證策略和挑戰(zhàn)

物聯(lián)網(wǎng)IC涉及日趨復雜 混合信號驗證挑戰(zhàn)大增

基于FPGA的混合信號驗證流程

SoC設計與驗證整合

求一種數(shù)模混合SoC設計協(xié)同仿真的驗證方法

一種數(shù)模混合SoC 設計協(xié)同仿真的驗證方法

一種數(shù)模混合SoC 設計協(xié)同仿真的驗證方法

SoC驗證環(huán)境搭建方法的研究

一種基于事務的SoC功能驗證方法

基于FPGA的驗證平臺及有效的SoC驗證過程和方法

利用FPGA軟硬件協(xié)同系統(tǒng)驗證SoC系統(tǒng)的過程和方法

混合SOC驗證的挑戰(zhàn)與方法介紹

混合SOC驗證的挑戰(zhàn)與方法介紹

評論