28335未使用的一些GPIO口需要如何處理,如果現在已經是懸空狀態的話,程序中如何配置,能夠讓外部可能引入的干擾最小?是配置成輸出口,然后輸出低嗎?

2020-06-04 15:44:53

有的,他們有著很理性的知識,同時又帶著一些自我創作的情感去布線,布出來的線就頗為美觀有藝術感。 下面是一些好的布線技巧和要領: 首先,先對做個基礎介紹,PCB的層數可以分為單層,雙層和多層的,單層現在

2018-09-18 15:55:57

實際電路比學校中學習的冗余元器件多一些,多了很多保護電阻電容,請大神解答一下吧。

2015-03-27 17:00:15

本帖最后由 x3942832 于 2012-9-28 11:19 編輯

1. 如何處理實際布線中的一些理論沖突的問題 問:在實際布線中,很多理論是相互沖突的;例如: 1。處理多個模/數地的接法

2012-09-28 11:15:18

以下問題:

1)AD10200管腳1的作用是什么,在實際的電路使用中,應該如何處理?

2)模擬信號輸入端是否為CMOS電路,A路、B路其中一路輸入懸空時,懸空管腳如何正確的處理?

3)采樣時鐘

2023-12-22 06:15:58

你好,我公司正在用ADE7880做一個項目,遇到一些問題。問幾個基礎的問題。希望能得到答復。謝謝! 1. 基波有效值寄存器只有一個電壓FVRMS和 FIRMS,如何讀三相每一項的基波值,是不是用

2018-12-18 09:10:01

的ADC,差分模式有什么弱點嗎? 和單端的輸入相比,外圍的電路相對復雜一些。 41.請問在高速數據采集系統設計中,我們怎樣來確定采樣率和存儲器帶寬? 采樣率由待處理信號的頻率決定。存儲器帶寬由采樣率

2017-10-24 08:23:54

問:在實際布線中,很多理論是相互沖突的;例如: 1。處理多個模/數地的接法:理論上是應該相互隔離的,但在實際的小型化、高密度布線中,由于空間的局限或者絕對的隔離會導致小信號模擬地走線過長,很難

2019-07-18 08:17:32

和loadKey的執行?這里還有一些問題需要解答:

1、如果不做任何處理,繼續執行這兩個函數,會不會報錯?

2.如果我不想執行這兩個功能,有什么推薦的策略讓我知道授權密鑰mater key已經加載成功?

3.Key是否可以校驗,類似于CMAC校驗功能?

2023-05-18 10:24:37

I2C總線實際應用中隱藏的一些問題的探 I2C 如今已經成為芯片間低速串行通信的事實標準,被廣泛使用在消費、控制類電子設備場合。本文就實際應用中隱藏的一些簡單問題進行討論。 [/hide]

2009-10-20 11:52:45

SI工程師給出的約束規則來完成布局布線的,這些也就是俗稱的“拉線工”。他們重復而機械的完成一塊塊PCB設計,一段時間設計后,他們中的一些或許已經有了這樣的一些經驗:哪些要做等長,哪些要走粗、哪些要平行

2016-12-20 17:34:18

PCB中電源部分如何處理?DDR的基本要求是什么啊 ?看了好多資料什么樣的說法都有

2013-03-14 14:51:56

1、如何處理實際布線中的一些理論沖突的問題問:在實際布線中,很多理論是相互沖突的;例如: 1。處理多個模/數地的接法:理論上是應該相互隔離的,但在實際的小型化、高密度布線中,由于空間的局限或者絕對

2014-12-31 14:32:05

、如何處理實際布線中的一些理論沖突的問題1). 基本上, 將模/數地分割隔離是對的。 要注意的是信號走線盡量不要跨過有分割的地方(moat), 還有不要讓電源和信號的回流電流路徑(returning

2017-04-16 11:58:12

平行也是因為要保持差分阻抗的一致性。若兩線忽遠忽近, 差分阻抗就會不一致, 就會影響信號完整性(signal integrity)及時間延遲(timing delay)。8、如何處理實際布線中的一些

2014-08-27 10:24:12

實際布線中的一些理論沖突的問題1. 基本上, 將模/數地分割隔離是對的。 要注意的是信號走線盡量不要跨過有分割的地方(moat), 還有不要讓電源和信號的回流電流路徑(returning

2012-08-05 19:33:41

忽遠忽近, 差分阻抗就會不一致, 就會影響信號完整性(signal integrity)及時間延遲(timing delay)8、如何處理實際布線中的一些理論沖突的問題1. 基本上, 將模/數地分割

2021-09-19 09:42:31

(signal integrity)及時間延遲(timing delay)。 8、如何處理實際布線中的一些理論沖突的問題 1. 基本上, 將模/數地分割隔離是對的。 要注意的是信號走線盡量不要跨過有分割

2018-08-30 10:49:23

完整性(signal integrity)及時間延遲(timing delay)。8、如何處理實際布線中的一些理論沖突的問題基本上, 將模/數地分割隔離是對的。 要注意的是信號走線盡量不要跨過有分割

2015-12-16 16:40:24

delay)。8、如何處理實際布線中的一些理論沖突的問題1. 基本上, 將模/數地分割隔離是對的。 要注意的是信號走線盡量不要跨過有分割的地方(moat), 還有不要讓電源和信號的回流電流路徑

2017-07-07 13:03:12

忽遠忽近, 差分阻抗就會不一致, 就會影響信號完整性(signal integrity)及時間延遲(timing delay)8、如何處理實際布線中的一些理論沖突的問題1. 基本上, 將模/數地分割

2015-10-30 15:25:15

)。 8、如何處理實際布線中的一些理論沖突的問題 1. 基本上, 將模/數地分割隔離是對的。 要注意的是信號走線盡量不要跨過有分割的地方(moat), 還有不要讓電源和信號的回流電流路徑

2015-01-09 11:14:05

1. 如何處理實際布線中的一些理論沖突的問題 問:在實際布線中,很多理論是相互沖突的;例如: 1。處理多個模/數地的接法:理論上是應該相互隔離的,但在實際的小型化、高密度布線中,由于空間的局限或者

2014-10-24 11:00:08

integrity)及時間延遲(timing delay)。8、如何處理實際布線中的一些理論沖突的問題基本上, 將模/數地分割隔離是對的。 要注意的是信號走線盡量不要跨過有分割的地方(moat), 還有不要

2016-09-12 14:53:53

間延遲(timing delay)。8、如何處理實際布線中的一些理論沖突的問題基本上, 將模/數地分割隔離是對的。 要注意的是信號走線盡量不要跨過有分割的地方(moat), 還有不要讓電源和信號的回流

2021-09-19 14:47:06

布線中的一些理論沖突的問題1. 基本上, 將模/數地分割隔離是對的。要注意的是信號走線盡量不要跨過有分割的地方(moat), 還有不要讓電源和信號的回流電流路徑(returning current

2011-03-17 10:05:21

,布線在高速PCB設計中是至關重要的。下面將針對實際布線中可能遇到的一些情況,分析其合理性,并給出一些比較優化的走線策略。主要從直角走線,差分走線,蛇形線等三個方面來闡述。

2009-08-20 20:58:49

a、如何處理實際布線中的一些理論沖突的問題 1. 基本上, 將模/數地分割隔離是對的。 要注意的是信號走線盡量不要跨過有分割的地方(moat), 還有不要讓電源和信號的回流電流路徑

2012-12-17 12:29:48

更新一下博客,最近有一些朋友問我如何處理數組中數據,順便發一下教程,代碼如下if(UartHandle->Instance == USART3)//stm32的串口

2022-02-21 07:09:59

遠忽近, 差分阻抗就會不一致, 就會影響信號完整性(signal integrity)及時間延遲(timing delay)。 8、如何處理實際布線中的一些理論沖突的問題 基本上, 將模/數地分割隔離

2018-09-12 20:53:55

忽遠忽近, 差分阻抗就會不一致, 就會影響信號完整性(signal integrity)及時間延遲(timing delay)8、如何處理實際布線中的一些理論沖突的問題1. 基本上, 將模/數地分割

2018-08-10 21:07:43

關于一些鋁基板焊盤及布線設計規范,大家僅供參考共同學習。

2017-08-13 17:04:31

怎樣去處理PCB板中的電源、地線?布線中網絡系統的作用是什么?

2021-04-25 09:07:37

BOTTOM層放置,放置后能過什么和TOP層連接,在哪里連接 3:誰能給小弟提供一些關于這方面的資料,小弟不勝感激

2012-12-10 11:34:57

**關于過孔的大小:電源還沒學完,待續。。。。關于電源線的一些規則:待續本章的一些零碎總結:1.不改變規則前提下消除錯誤綠色提示T+M2.電源布線盡量寬一些1mm(40mil)一般承載1Aled一般電流比較小,電源線可以細一些,蜂鳴器電流會大一些3.高頻版中,盡量少...

2021-11-11 07:09:48

(signal integrity)及時間延遲(timing delay)。 8、如何處理實際布線中的一些理論沖突的問題 基本上, 將模/數地分割隔離是對的。 要注意的是信號走線盡量不要跨過有分割的地方

2019-09-06 18:54:23

網絡布線是一項十分繁瑣和復雜的工作,但目前看來從事這項工作的人員中還普遍存在著相關知識與經驗不足的現象。比如,大量電話工程及電工人員同時也兼顧著網絡布線的工作。事實證明,這種做法存在有很多隱患,對于

2021-02-02 07:28:11

制作了TMS320F28335的PCB,但是JTAG調試時,經常遇到掉線的問題,哪里有關于C2000系列PCB布局布線的一些參考手冊啊?

2020-06-17 15:56:10

使用PADS2007軟件 由于一些板,尤其是U盤等面積很小的板,FLASH中只使用了為數不多的幾個PIN,為了可以讓其它PIN下面可以走線,增加GND網絡的面積,所以實際操作中要隱藏一些PIN

2018-09-17 17:13:49

本文主要從高頻PCB的手動布局、布線兩個方面,基于Protel99SE對在高頻PCB設計中的一些問題進行研究。

2021-04-22 06:21:32

主要做了一些數字濾波器,和對語音去噪處理!!!新人貼!!做的不太好。多多關照!!

2013-03-06 11:36:37

1.如何處理實際布線中的一些理論沖突的問題 問:在實際布線中,很多理論是相互沖突的;例如:1。處理多個模/數地的接法:理論上是應該相互隔離的,但在實際的小型化、高密度布線中,由于空間的局限或者絕對

2014-11-06 16:22:00

如何處理實際布線中的一些理論沖突的問題

2009-09-06 08:43:06

如何處理實際布線中的一些理論沖突的問題

2009-09-06 08:43:19

如何處理實際布線中的一些理論沖突的問題 基本上, 將模/數

2009-03-20 13:54:18

在我的設計中,有一些未使用的引腳。一些是IO,一些是僅輸入引腳。我將IO保持為開放但我很困惑如何處理僅輸入引腳。一般的做法是將它們連接到GND,但我覺得連接到gnd時功耗更大。善意的建議我適當的答案

2019-06-11 08:34:02

余時間研究了下 Vite 和 Rollup 的內部實現,借此機會來探究下構建工具是如何處理 external 這一類外部鏈接的,并對 external 的能力做一些擴展。如何解析 External因為

2022-11-30 14:58:57

大家好我有一個關于如何處理virtex 5中的復位信號的問題。用于復位整個設計的同步復位信號。復位信號的時序很難滿足,因為扇出很大。如果我減少synplify pro中的扇出限制。我為其余的東西留下了很多復雜的線條。這需要很多邏輯。應該有更好的解決方案。有人可以幫助嗎?問候小東宇

2020-06-03 08:18:11

你好,我查找了一些更復雜的項目,其中有多個中斷源。但是我只找到具有簡單和單個I/O的項目。我想了解如何處理具有多個可能中斷源的中斷。如果有關于這個主題的很好的示例或教程,它可以有所幫助。謝謝,Ran

2020-04-27 13:42:16

親愛的大家,我正在做一個關于一些bisic信號處理的項目。它描述如下,信號由PmodMic采樣,然后數字化信號被發送到我們定制的濾波器模塊,然后濾波后的信號被發送到ARM進行進一步處理,顯示等。我

2020-03-12 10:29:25

致, 就會影響信號完整性(signal integrity)及時間延遲(timing delay)。 8、如何處理實際布線中的一些理論沖突的問題 基本上, 將模/數地分割隔離是對的。 要注意的是信號走

2018-09-19 16:21:03

頗為頭疼。下面是PCB布線的一些常用規則,無論你是小白還是已入行的工程師,都應該掌握。 PCB布線常用規則 1、走線的方向控制規則 輸入和輸出端的導線應盡量避免相鄰平行。在 PCB 布線時,相鄰

2023-04-18 15:04:04

是保留地層的完整性。3、大面積導體中連接腿的處理在大面積的接地(電)中,常用元器件的腿與其連接,對連接腿的處理需要進行綜合的考慮,就電氣性能而言,元件腿的焊盤與銅面滿接為好,但對元件的焊接裝配就存在一些

2018-05-07 08:20:06

致, 就會影響信號完整性(signal integrity)及時間延遲(timing delay)。8、如何處理實際布線中的一些理論沖突的問題1. 基本上, 將模/數地分割隔離是對的。 要注意的是信號走線

2013-11-07 15:25:01

也要最終經過Layout得以實現并驗證,由此可見,布線在高速PCB設計中是至關重要的。下面將針對實際布線中可能遇到的一些情況,分析其合理性,并給出一些比較優化的走線策略。主要從直角走線,差分走線,蛇形線

2012-07-21 14:22:45

有的,他們有著很理性的知識,同時又帶著一些自我創作的情感去布線,布出來的線就頗為美觀有藝術感。 下面是一些好的布線技巧和要領: 首先,先對做個基礎介紹,PCB的層數可以分為單層,雙層和多層的,單層現在

2018-09-18 15:42:39

有的,他們有著很理性的知識,同時又帶著一些自我創作的情感去布線,布出來的線就頗為美觀有藝術感。下面是一些好的布線技巧和要領:首先,先對做個基礎介紹,PCB的層數可以分為單層,雙層和多層的,單層現在

2017-03-27 13:32:46

有的,他們有著很理性的知識,同時又帶著一些自我創作的情感去布線,布出來的線就頗為美觀有藝術感。下面是一些好的布線技巧和要領:首先,先對做個基礎介紹,PCB的層數可以分為單層,雙層和多層的,單層現在

2016-11-04 10:42:42

硬件中的一些術語什么是BOM2.什么是 LDO3.什么是ESR4.什么是TTL5.什么是MOS、NMOS、PMOS、CMOS6.什么是OC、OD7.什么是線或邏輯與線與邏輯8.什么是推挽結構9.

2011-08-03 11:30:27

delay)。8、如何處理實際布線中的一些理論沖突的問題基本上, 將模/數地分割隔離是對的。 要注意的是信號走線盡量不要跨過有分割的地方(moat), 還有不要讓電源和信號的回流電流路徑

2019-04-11 08:00:00

我一直在試圖把一些項目分割成多個可重用的文件,這并不是一件容易的事情。我終于解決了問題,除了最后一個錯誤:編譯器/匯編程序不知道如何處理“Extn”指令,就像試圖從其他文件導入子程序和變量標簽一

2019-09-23 12:58:36

)及時間延遲(timingdelay)。 8、如何處理實際布線中的一些理論沖突的問題 1. 基本上, 將模/數地分割隔離是對的。要注意的是信號走線盡量不要跨過有分割的地方(moat), 還有不要讓電源

2018-11-27 10:00:59

有沒有高手可以解決下這種問題,規則設置器件,但是不知道怎么設置布線不布線不沖突,一布線就沖突了

2019-09-30 05:36:21

本帖最后由 一只耳朵怪 于 2018-6-14 08:55 編輯

希望大神們、專家們、前輩們(反正大家各種牛人吧~~),能不能推薦一些關于MCU理論的書,像是什么微機原理接口技術這種,最好滿足

2018-06-13 02:36:16

距會影響到差分阻抗的值, 此值是設計差分對的重要參數。需要平行也是因為要保持差分阻抗的一致性。若兩線忽遠忽近, 差分阻抗就會不一致, 就會影響信號完整性及時間延遲。8.如何處理實際布線中的一些理論沖突

2018-08-14 15:41:11

(signal integrity)及時間延遲(timing delay)。 8、如何處理實際布線中的一些理論沖突的問題? 基本上, 將模/數地分割隔離是對的。 要注意的是信號走線盡量不要跨過有分割的地方

2018-09-20 10:36:56

delay)。7、如何處理實際布線中的一些理論沖突的問題(1)基本上, 將模/數地分割隔離是對的。要注意的是信號走線盡量不要跨分割,(2)晶振要有穩定的振蕩信號, 一定要將晶振和芯片盡可能靠近,間距

2019-11-16 07:00:00

, 差分阻抗就會不一致, 就會影響信號完整性(signal integrity)及時間延遲(timing delay)。 8、如何處理實際布線中的一些理論沖突的問題 基本上, 將模/數地分割隔離

2018-09-19 16:13:19

integrity)及時間延遲(timing delay)。8、如何處理實際布線中的一些理論沖突的問題晶振是模擬的正反饋振蕩電路, 要有穩定的振蕩信號, 必須滿足loop gain 與 phase

2017-09-13 22:09:15

)。 8、如何處理實際布線中的一些理論沖突的問題? 基本上,將模/數地分割隔離是對的。要注意的是信號走線盡量不要跨過有分割的地方(moat),還有不要讓電源和信號的回流電流路徑(returning

2018-09-21 16:26:48

是因為這間距會影響到差分阻抗的值, 此值是設計差分對的重要參數。需要平行也是因為要保持差分阻抗的一致性。若兩線忽遠忽近, 差分阻抗就會不一致, 就會影響信號完整性及時間延遲。8.如何處理實際布線中的一些

2019-09-28 08:00:00

for Windows V1.5軟件為例來介紹一下高頻電路布線時Protel軟件能提供的一些特殊對策。 (1)高頻電路往往集成度較高,布線密度大,采用多層板既是布線所必須的,也是降低干擾的有效手段

2018-08-23 13:50:27

間延遲(timing delay)。8、如何處理實際布線中的一些理論沖突的問題基本上, 將模/數地分割隔離是對的。 要注意的是信號走線盡量不要跨過有分割的地方(moat), 還有不要讓電源和信號的回流

2017-01-20 10:29:29

針對D-S證據理論的沖突證據融合問題進行了研究,通過對證據進行沖突檢驗及修正彌補了D-S證據理論在處理沖突證據時的不足。采用了加性策略對事件進行排序的方法,找出證據

2008-12-14 10:59:00 11

11 1、如何處理實際布線中的一些理論沖突的問題 問:在實際布線中

2006-04-16 21:59:29 391

391 本內容匯總了近30個PCB布線知識面試題是PCB工程師必備的知識點總結,也是面試者需要的知識。如何處理實際布線中的一些理論沖突的問題,在高速設計中,如何解決信號的完整性問題

2011-11-24 10:00:51 0

0 參數。需要平行也是因為要保持差分阻抗的一致性。若兩線忽遠忽近, 差分阻抗就會不一致, 就會影響信號完整性(signal integrity)及時間延遲(timing delay)。8、如何處理實際布線

2018-09-20 18:18:30 455

455 問:在實際布線中,很多理論是相互沖突的;例如: 1。處理多個模/數地的接法:理論上是應該相互隔離的,但在實際的小型化、高密度布線中,由于空間的局限或者絕對的隔離會導致小信號模擬地走線過長,很難

2019-05-28 14:56:54 389

389 隨著智能家居的興起,布線問題的嚴重性也日漸突出,那么在這個問題上,我們到底該如何處理呢?

2019-07-29 17:36:00 1

1 1、如何處理實際布線中的一些理論沖突的問題

問:在實際布線中,很多理論是相互沖突的;例如: 1。處理多個模/數地的接法:理論上是應該相互隔離的,但在實際的小型化、高密度布線中,由于空間的局限或者

2019-09-23 08:00:00 0

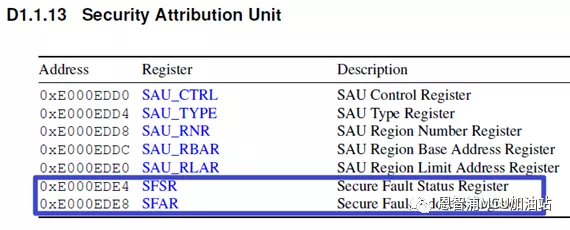

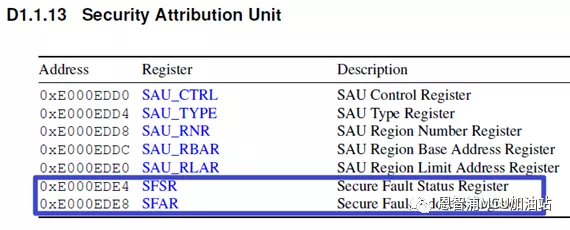

0 調試TrustZone時,如何處理HardFault?

2023-09-27 16:33:02 343

343

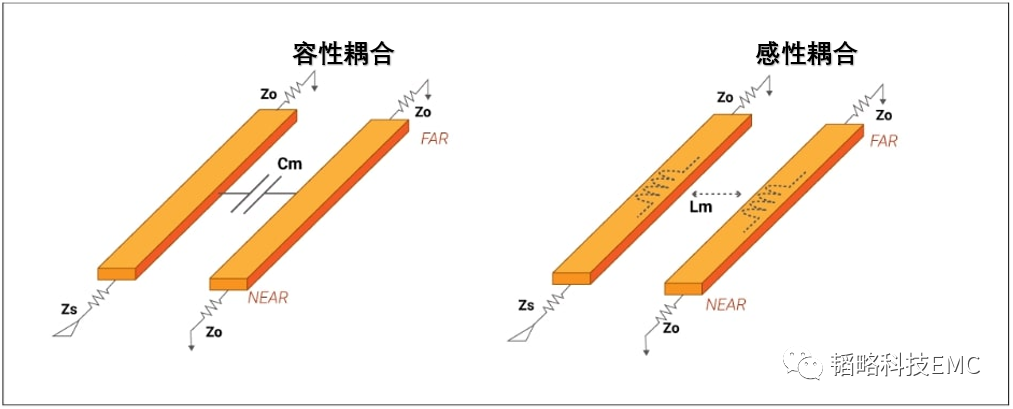

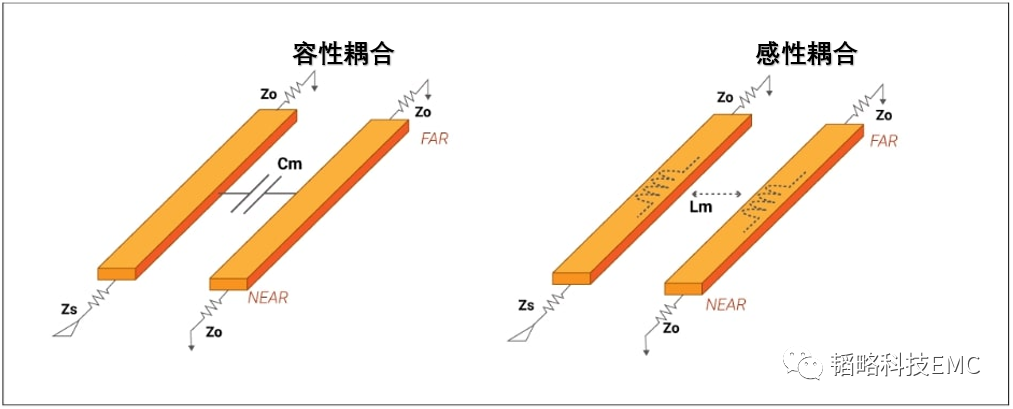

什么是串擾?該如何處理它?

2023-12-05 16:39:27 310

310

在布局、布線中如何處理才能保證50M以上信號的穩定性? 布局和布線是確保電子設備的信號穩定性的關鍵步驟。在保證50M以上信號穩定性的前提下,以下是一些布局和布線的最佳實踐,能夠幫助你處理電子設備

2023-11-24 14:51:05 189

189

電子發燒友App

電子發燒友App

評論