摘要:介紹了一種適用于主被動復合制導實時信號處理的多處理器并行處理系統。論述了實際系統中信號處理器的軟硬件結構和實現,針對主被動復合制導信息處理算法的特點和要求,充分利用了TMS320C6202芯片的軟硬件資源,如DMA、中斷、多通道串口、擴展總線等。經過外場試驗表明,該處理機能朗好地完成主被動復合制導的處理任務,實現預定目標。

在現代戰爭中,隨著戰場環境的日益復雜化,單一制導方式已經不能很好地滿足在復雜戰場環境下具有良好的戰術性能的要求。單純采用主動或單純采用被動制導都存在一定的總是,已經不適應現實的需求。主動跟蹤適用范圍廣、信息量大,但一旦受到復雜電子系統的干擾,其工作性能將受到影響,甚至完全失去工作能力;而被動制導的角通道精度較高,但缺乏距離分量。因此采用主被動復合制導可以彌補單一制導技術的缺陷,發揮各自的優點,通過信息的綜合利用使整個系統在性能上取得互補,從而提高系統總的性能指標。

在主被動復合制導中,背景復雜、目標較我,為了有效地從復雜背景中檢測和跟蹤目標,必須采用羅復雜的算法;為了滿足復雜算法的實時性要求,需要選用一款高速的DSP芯片進行系統設計。目前TI公司的高速定點DSP芯片中,速度最快的是TMS320C64X系列,但TMS320C64X系列現在只有商業級芯片,不能滿足制導信號處理的環境,因此選用TMS320C6202,它最高能工作在250MHz的主頻下,峰值處理速度可以達到2000MIPS。

1 處理機功能及結構

處理機功能如下:

根據上位機提供的目標距離、角度預定信息,對指定區域進行搜索。

能從多目標環境中分選識別多個目標。

能對目標的角度、距離進行跟蹤并具有抗干擾功能。

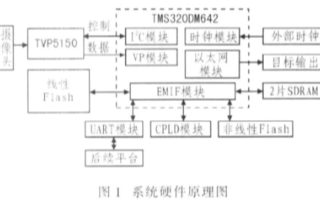

處理機的總體結構如圖1所示。

整個信號處理器由兩塊信號處理板和一塊電源板組成,分別完成主動通道的信號處理及主被動的數據融合、被動通道的信號處理主整個系統的電源轉換和產生。兩塊信號處理板之間通過同步串口通訊。另外,主動信號處理板產生的時鐘和定時信號通過軟線提供給被動信號處理板。

2 系統的硬件和軟件設計

2.1 信息處理系統原理框圖

信號處理機原理框圖如圖2所示。主要工作通道有兩個:主動通道和被動通道。主動通道完成波門內的目標檢測,被動通道則在全程上完成干擾檢測。然后對主、被動通道檢測到的信息進行融合,再對目標進行跟蹤。

2.2 信息處理系統硬件組成

2.2.1 主動信號處理板

主動信號處理板主要完成雷達回波信號的數據采集、目標的搜索跟蹤、主被動的數據融合以及各種定時信號的產生。主動信號處理板的結構如圖3所示。

主動信號處理板采用兩片TMS320C6202,在圖中標準為DSP0和DSP1。兩片DSP的周邊除了最小系統所必需的時鐘、復位電路、調試JTAG口外,還外掛了SBSRAM以提高系統的存儲容易,另外還有用來固化系統運行程序的引導FLASH。DSP1主要完成數據要集預處理任務,所以它的擴展總線上連接了六片同步FIFO,用來存儲A/D采樣后的雷達回波數據;DSP0則主要完成數據融合和控制的任務,故其EMIF總線上連接了低速A/D、低速D/A、異步串口,用來接收和輸出天線角度信息及控制信號。兩片DSP之間則通過64KB的高速雙口RAM和McBSP交換數據信息。雙口RAM的采用是考慮到它具有兩套數據和地址總線,非常適合作為系統之間的接口存儲器。總的來說,這種設計可以減小單個DSP信號處理負擔,同時使得整個系統擁有一定的處理裕量。

TMS320C6202的EMIF總線上需要訪問很多器件,其中一些器件的信號電平和TMS320C6202并不匹配,再加上不同速度器件的混合訪問,所以在實際系統中需要考慮如何分配EMIF存儲空間以及加入適當的緩沖隔離的問題。這里以DSP0的外部存儲器接口設計為例進行說明。參見圖4。

TMS320C6202整個EMIF外部空間最大容易為64MB,處理器內部將它分成四個子空間,并對每個子空間提供獨立的選通信號,也就是圖4中標注的CE0~CE3。

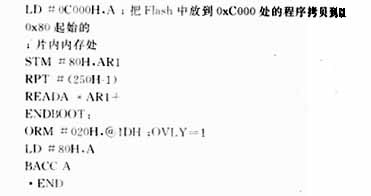

當處理器設置為ROM引導時,上電后首先從CE1空間讀取64KB數據到地址0處,然后程序從地址0處開始執行,所以引導FLASH必須配置在CE1地址空間。EPM7128的選通信號則通過高位地址譯碼獲得。

圖3

對于CE2空間,通過EPLD地址譯驪將該空間進一步細化,分配給三個低速器件。

這樣分配地址空間是基于如下一些考慮:

(1)由于TMS320C6202只能對每個地址空間統一地設置訪問器件類型和訪問時序,所以設計時盡可能將訪問速度相近的器件放置在同一個地址空間,如低速A/D、低速D/A以及導步串口都分配在CE2空間,這樣有利用EMIF寄存器的設計。

(2)訪問速度較高的器件在PCB布局時應當盡量靠DSP,緩沖級數要少,以減小總線延遲,提高訪問速度。

(3)對于SBSRAM或SDRAM,由于訪問的時鐘頻率較高,應當直接掛在TMS320C6202的EMIF總線上。

圖4中加入了隔離電路,主要是基于如下考慮:

(1)TMS320C6202本身輸出信號帶負載的能力不是很強,增加緩沖隔離電路可以提高信號的驅動能力。

(2)緩沖驅動芯片在未選通時輸入輸出均處于高阻狀態,且其輸入容性負載也很小,只有幾pF,所以可以用來隔離器件,避免由于大的容性負載而造成的上沖、下沖、信號上升下降沿變緩等信號完整性問題。

(3)采用的緩沖芯片的輸出管腳在片內都串接有一個小電阻,用作源端匹配電阻,用以吸引信號反射能量,從而可以改善輸出信號質量。

圖4

(4)由于低速A/D芯片的輸出信號電平和TMS320C6202的信號電平不匹配,而緩沖隔離芯片可以兼容二者,所以需要加入緩沖隔離。

(5)由于TMS320C6202為BGA封裝,在PCB布局布線時其周邊的布局空間是有限的,加入緩沖隔離可以延長信號傳輸距離,從而增大PCB布局的自由度。

當然,加入緩沖隔離后肯定會引起信號的傳輸延遲,從而降低訪問器件的速度,所以牽涉到高速器件時必須充分考慮這一點。

另外,設計中采用兩片EPLD(EPM7128AETI100-7和EPM7256144-7),主要完成定時信號、片選信號和控制信號的產生,這樣有利于系統的升級和二次開發。

2.2.2 被動信號處理板

被動處理板結構如圖5所示。可以看出是被動信號處理板和主動信號處理板的板型基本相同,只是由于被動信號處理板的處理量相對主動信號處理板較少,故只采用一片TMS320C6202。為了實現主、被動信號處理板的同步,將主動信號處理板的時鐘信號、定時同步信號引出并提供給了被動信號處理板。

TMS320C6202的多通道串口為同步串口,由于具有很強的可編程性,如時鐘、幀同步和時鐘源都是可以軟件設置的,因此實現起來非常簡單,最多只需要7根信號線就可以了。所以通過它實現主、被動信號處理板之間少量的數據交換非常方便。

2.2.3 電源板

整個系統所需要的電源品種較多,有數字3.3V、1.8V、5V和模擬的+/-5V、+/-15V。其中3.3V、1.8電源的功耗較大,整個系統功耗在18W左右。設計中,為了避免數字信號和模擬信號的相互干擾,數字電源和模擬電源分別產生。

2.2.4 設計難點

信號處理板設計的難點主要是高頻率數字電路設計和模/數電路的混合設計。

由于TMS320C6202工作在250MHz的主頻下,其外部存儲設備也工作在很高的時鐘頻率下,因此PCB布局布線時需要考慮信號的完整性問題。在實際設計過程當中,通過選擇合適的總線拓撲結構、合理的疊層結構,對高速數字信號線在仿真的基礎上加入適當的端接消除信號反射問題,較好地解決了信號的完整性問題。

由于信號處理板上模擬器件和數字器件共享,并且模擬部分的信號電平也存在較大差別,如低速A/D轉換器的輸入信號在±10V之間,而高速A/D轉換器的模擬輸入信號只有幾百mV,所以設計當中一方面應充分考慮數字電路對模擬電路的干擾問題。在實際系統中,采取器件隔離、元器件合理布局、電源濾波等方法,例如在運放和ADC的電源端,采用串接鐵氧體磁芯來獲得較好的濾波效果,模擬地、數字地僅在電源入口處一點連接,最終比較好地解決了噪聲串擾問題,A/D轉換器的精度均達到系統要求。

2.3 信息處理系統軟件設計

整個處理機需要編寫軟件的是三個EPLD和三個DSP。EPLD完成各種時序的產生和控制以及一些簡單的地址譯碼,編寫不是很復雜;軟件設計的重點是三個DSP的功能分配和軟件的編寫。

整個信號處理機的DSP處理流程如圖6所示。根據信號處理機的硬件結構和計算量的大小,將各個DSP的功能和流程分配如下:

(1)主動板DSP1

·利用DM將高速A/D轉換器采集的數據從FIFO讀到片內。利用DMA傳數有兩個原因:①高速A/D的FIFO連在TMS320C6202的擴展總線(XBUS)上,擴展總線工作在I/O口工作方式,只有DMA能訪問,CPU不能進行讀寫;②利用DMA可以將傳數和數據處理并行起來,充分利用DSP的處理能力。

·對讀入的數據進行非相參積累和恒虛警檢測。

·提取跟蹤波門的面積中心和角誤差信息。

·將檢測到的信息通過雙口RAM送到DSP0。

(2)主動板DSP0

·從雙口RAM接收DSP1的檢測結果。

·對DSP1的檢測結果進行二次檢測。

·根據二次檢測結果控制導引頭狀態的切換。

·通過低速A/D轉換器獲得天線的角度和速度,通過低速A/D轉換器控制天線的角度或速度。

·通過多通道串口(MCBSP)接收被動通道的檢測信息,完成主被動信息融合。

·通過異步串口和上位機進行通訊:傳送導師引頭狀態或連接上位機命令。

(3)被動板DSP

·利用DMA讀取高速A/D采樣數據。

·對采樣數據進行檢測。

·將檢測結果通過MCBSP送給主動板DSP0。

DSP的軟件開發一般分為三個階段:(1)編寫C代碼;(2)如果不滿足實時性要求,則要優化C代碼;(3)若仍不滿足實時性要求,則要對關鍵性代碼用線性匯編改寫。對于本文所設計的信號處理機,由于利用了三個高速的DSP芯片并行處理,再加上對C程序進行了人工優化和TI提供的C編譯器具有的良好的編譯性能,整個程序都是利用C代碼實現,完全能夠滿足信號處理實時性的要求。

本文設計的以TMS320C6202為核心處理器的信號處理機已應用于某導引頭的原理樣機,并經過外場試驗,性能指標滿足了系統各方面的要求,效果理想。

相關推薦

基于TMS320DM642 DSP芯片實現多功能視頻處理系統的設計

1111

1111

TMS320C6202|TMS320C6202B

TMS320C6678的相關資料推薦

DSP的各種并行處理方法和優缺點

TLC5620I+TMS320F2812串口通信的硬件接口及軟件設計

【TL6748 DSP申請】基于TMS320C6748 的高速DSP信號處理

【TL6748 DSP申請】基于TMS320C6748 高速DSP嵌入式信號處理模塊

【TL6748 DSP申請】基于TMS320C6748高速DSP信號處理模塊設計

分析一款不錯的基于多DSP與FPGA的實時圖像處理系統設計

創龍TMS320C6655TMS320C6657 DSP核心板

基于TMS320C6701信號處理器的高性能信號處理模塊的設計方案

基于DSP的圖像處理系統的應用研究

基于DSP的毫米波主被動復合探測器目標識別系統設計【回映分享】

基于labview語音信號處理系統設計

基于數字信號處理器TMS320F2812的逆變電路設計

廣州創龍TMS320C6655 TMS320C6657核心板

怎么實現基于TMS320 DM642的多路視頻處理系統設計?

怎么實現基于TMS320DM642視頻采集驅動開發?

怎么實現基于DSP的陣列聲波信號采集與處理系統的設計?

數字信號處理器TMS320F2802相關資料下載

數字信號處理器TMS320F2806電子資料

數字信號處理器TMS320C2801資料推薦

求一套基于TMS320C6x11系列DSP的圖像獲取方案

請問怎樣去設計激光多譜勒信號處理系統?

請問有TMS320C6416和TMS320C6747的對比表嗎?原來用的TMS320C6416,現在想換TMS320C6747 或TMS320C6747

TMS320C6202B pdf datasheet

24

24基于多互聯網絡的并行信號處理系統

13

13基于TMS320C6000和同步FIFO的多DSP系統設計與

30

30基于TMS320C6711 的線陣CCD 采集與處理系統

23

23基于TMS320C6415實現機載SAR方位向預濾波處理

11

11基于TMS320F240 的攝影點陣系統設計

12

12一種基于TMS320VC33 DSP的通用圖像處理系統設計

37

37基于DSP的實時圖像處理系統

15

15基于TMS320VC5402的汽車防撞信號處理系統設計與實現

32

32TI處理器TMS320C54CST

TI處理器TMS320C206

基于DSP的腦電信號處理系統設計

43

43通用語音處理系統的DSP實現

22

22基于TMS320C6711的交通圖像采集與處理系統設計

32

32基于TMS320C80的圖像采集系統

21

21基于DSP的語音信號處理系統設計

73

73TMS320F28335PGFA 這一款信號處理微控制器MCU

基于DSP和DSP/BIOS的實時雷達信號采集與處理系統

25

25數字信號處理系統的設計與實踐(實驗指導書)

37

37基于TMS320C6202的裝甲戰車智能圖像跟蹤系統硬件平臺

6

6基于雙DSP(TMS320C6414)的大視場紅外目標實時檢

14

14基于TMS320DM642的仿生眼視覺圖像處理系統

33

33基于TMS320F2812的雙機信息處理系統設計

18

18TMS320C6202B-300,pdf(Fixed-Poi

4

4TMS320C6202B-250,pdf(Fixed-Poi

10

10基于TMS320F2812的震動信號處理系統設計

27

27基于TMS320VC5410的實時信號處理系統的設計

828

828

TMS320C3x DSP和PC機的異步串行通信設計

1016

1016

基于DSP TMS320C6416的實時圖像處理系統

2563

2563

基于雙DSP的實時圖像處理系統

1009

1009

基于DSP芯片TMS320C6418的成像制導仿真系統設計

1061

1061

TMS320C6727的音頻采集處理系統及回放功能實現

3155

3155

基于TMS320VC5402的超聲檢測高速采樣系統

55

55基于TMS320C6711的光纖陀螺信號處理系統

25

25TMS320VC33實現高速多處理機圖像處理系統

62

62雙機信息處理系統設計方案解析

0

0基于雙TMS320VC5416處理器的實時圖像搜索跟蹤處理系統設計

0

0基于TMS320VC5502和CPLD XC95144的低功耗多路數據處理系統

10

10基于TMS320C6201的數字信號處理系統的設計方法

1

1實時圖像采集和處理系統的設計方法

7

7以FPGA和TMS320DM642為核心的實時圖像采集和處理系統設計詳解

2633

2633

TMS320UC5409和TMS320VC5409數字信號處理器硅勘誤表的詳細概述

2

2TMS320C6202B 定點數字信號處理器

數字信號處理器TMS320VC5402與音頻模擬芯片TLC320AD50C的接口設計

517

517基于TMS320VC5402的音頻信號采集與處理系統

779

779使用雙DSP和TMS320C6202B設計紅外制導系統的應用說明

2

2剖析TMS320LF2407的腦電信號處理系統設計

2031

2031

tms320f2808數字信號處理器中文資料

0

0基于8片TMS320C6416的衛星圖像目標提取高速處理系統

0

0 電子發燒友App

電子發燒友App

評論