FPGA中組合邏輯門占用資源過多怎么降低呢?有什么方法嗎?

2023-04-23 14:31:17

技術(shù)亞閾值漏電流是靜態(tài)功耗產(chǎn)生的主要原因之一,降低亞閾值漏電流將有效地降低芯片的靜態(tài)功耗。亞閾值漏電流的解析模型如下公式所示:Vt為閾值電壓,n為亞閾值擺幅系數(shù),W為晶體管的寬度,L為長度,μ為電子

2020-04-28 08:00:00

邏輯門開關(guān)活動(dòng)時(shí)的功率消耗,在這段時(shí)間內(nèi),電路的輸入輸出電容完成充電和放電,形成瞬間的軌到地的直通通路。與靜態(tài)功耗相比,通常有許多方法可降低動(dòng)態(tài)功耗。采用正確的結(jié)構(gòu)對于設(shè)計(jì)是非常重要的,最新的FPGA

2015-02-09 14:58:01

結(jié)合采用低功耗元件和低功耗設(shè)計(jì)技術(shù)在目前比以往任何時(shí)候都更有價(jià)值。隨著元件集成更多功能,并越來越小型化,對低功耗的要求持續(xù)增長。當(dāng)把可編程邏輯器件用于低功耗應(yīng)用時(shí),限制設(shè)計(jì)的低功耗非常重要。如何減小動(dòng)態(tài)和靜態(tài)功耗?如何使功耗最小化?

2019-08-27 07:28:24

。除此之外,設(shè)計(jì)中采用一些低功耗技巧,也可以降低靜態(tài)功耗。IGLOO具有功耗友好的器件架構(gòu),能提供靜態(tài)、睡眠、Flash*Freeze功耗模式,允許采用動(dòng)態(tài)電壓和頻率調(diào)節(jié)技術(shù)來降低系統(tǒng)整體實(shí)際功耗。提供可選擇

2019-07-05 07:19:19

自動(dòng)降耗將是對設(shè)計(jì)流程早期以及邏輯綜合過程中功耗減少的補(bǔ)充。 功耗是一個(gè)“機(jī)會(huì)均等”問題:從早期設(shè)計(jì)取舍到自動(dòng)物理功耗優(yōu)化,所有降低功耗的技術(shù)都彼此相互補(bǔ)充,并且需要作為每個(gè)現(xiàn)代設(shè)計(jì)流程中的一部分加以

2017-10-08 22:06:50

綜合過程中功耗減少的補(bǔ)充。 值得注意的是,功耗是一個(gè)"機(jī)會(huì)均等"問題,從早期設(shè)計(jì)取舍到自動(dòng)物理功耗優(yōu)化,所有降低功耗的技術(shù)都彼此相互補(bǔ)充,并且需要作為每個(gè)現(xiàn)代設(shè)計(jì)流程中的一部分加以

2017-06-29 16:46:52

MOS降低發(fā)熱功耗除了并聯(lián) 還有其他的方法不?電流是不能變的。并聯(lián)雖然內(nèi)阻可以減小,不過好像會(huì)影響同步的開關(guān)速度。不同步開關(guān)的話MOS可能就燒了

2020-11-23 11:57:47

有什么方法可以進(jìn)一步降低待機(jī)模式的功耗

2023-10-12 07:23:28

本人用了一塊vs1053作為解碼芯片,這個(gè)芯片在待機(jī)的時(shí)候電流為2.3ma左右,有沒方法降低功耗,數(shù)據(jù)手冊上也沒怎么寫,要是能降到1ma以內(nèi)就好了。

2016-08-10 19:40:43

隨著移動(dòng)通信技術(shù)的飛速發(fā)展和移動(dòng)通信網(wǎng)絡(luò)技術(shù)的廣泛應(yīng)用,移動(dòng)視頻監(jiān)控技術(shù)(mobile video supervision,MVS)也隨之得到發(fā)展。相比于有線視頻監(jiān)控技術(shù),MVS具有更高的應(yīng)用靈活性,適合移動(dòng)監(jiān)控和遠(yuǎn)程監(jiān)控,部署方便。因此,MVS系統(tǒng)在防暴、軍事、氣象、環(huán)保等領(lǐng)域的需求越來越迫切。

2019-08-09 06:52:35

你好,在無需使用BLE通信的應(yīng)用程序中,降低電力消耗的有效途徑是什么?在我的應(yīng)用程序中不存在節(jié)電選項(xiàng)。CYW20706是主要的主機(jī),所以我不能使用深度睡眠模式。應(yīng)用程序使用周期性計(jì)時(shí)器(幾十毫秒

2018-12-05 14:21:55

論低功耗藍(lán)牙技術(shù)在智能移動(dòng)設(shè)備中的應(yīng)用。

2021-05-11 07:04:58

預(yù)測的下一狀態(tài)條件列舉狀態(tài)機(jī),并選擇常態(tài)之間轉(zhuǎn)換位較少的狀態(tài)值。這樣,您就能夠盡可能減少狀態(tài)機(jī)網(wǎng)絡(luò)的轉(zhuǎn)換量(頻率)。確定常態(tài)轉(zhuǎn)換和選擇適當(dāng)?shù)臓顟B(tài)值,是降低功耗且對設(shè)計(jì)影響較小的一種簡單方法。編碼形式越簡單

2012-01-11 11:59:44

。 時(shí)鐘門控的主要挑戰(zhàn)是找到使用它的最佳位置,并在正確的周期創(chuàng)建時(shí)鐘門控的開關(guān)

邏輯。時(shí)鐘門控是一種成熟的

降低功耗技術(shù),已經(jīng)使用了很多年。Power Compiler等綜合工具可以在時(shí)鐘路徑適當(dāng)?shù)奈恢?/div>

2022-04-12 09:34:51

結(jié)合采用低功耗元件和低功耗設(shè)計(jì)技術(shù)在目前比以往任何時(shí)候都更有價(jià)值。隨著元件集成更多功能,并越來越小型化,對低功耗的要求持續(xù)增長。當(dāng)把可編程邏輯器件用于低功耗應(yīng)用時(shí),限制設(shè)計(jì)的低功耗非常重要。本文將討論減小動(dòng)態(tài)和靜態(tài)功耗的各種方法,并且給出一些例子說明如何使功耗最小化。

2019-07-12 06:38:08

FPGA的功耗高度依賴于用戶的設(shè)計(jì),沒有哪種單一的方法能夠?qū)崿F(xiàn)這種功耗的降低,如同其它多數(shù)事物一樣,降低功耗的設(shè)計(jì)就是一種協(xié)調(diào)和平衡藝術(shù),在進(jìn)行低功耗器件的設(shè)計(jì)時(shí),人們必須仔細(xì)權(quán)衡性能、易用性、成本、密度以及功率等諸多指標(biāo)。

2019-08-15 08:28:42

一些方法,例如睡眠模式和低功耗設(shè)置,但我不確定是否有任何其他方法或技巧可以進(jìn)一步降低功耗。有人有經(jīng)驗(yàn)可以分享嗎?我需要知道如何在保持通信穩(wěn)定的同時(shí)最大限度地降低功耗。

2024-03-01 07:38:34

ZED 和ZC,在組網(wǎng)正常的情況下,ZED可以進(jìn)入低功耗模式,電流在uA級(jí)別。CC2530芯片當(dāng)關(guān)閉ZC后,ZED會(huì)持續(xù)的進(jìn)行網(wǎng)絡(luò)發(fā)現(xiàn),無法進(jìn)入低功耗模式。電流達(dá)28mA;求教TI工程師,如何降低ZC發(fā)現(xiàn)網(wǎng)絡(luò)的頻次以降低功耗?或者有其他什么方法來降低功耗?

2020-08-07 07:03:22

低功耗mcu的選擇方法如何降低mcu的功耗

2021-02-24 06:11:07

電子產(chǎn)品的低功耗問題經(jīng)常讓產(chǎn)品設(shè)計(jì)者頭痛而又不得不面對。以單片機(jī)(MCU)為核心的系統(tǒng),其功耗主要由單片機(jī)功耗和單片機(jī)外圍電路功耗組成。要降低單片機(jī)系統(tǒng)的功耗,需要從硬件和軟件兩方面入手。

2021-02-19 07:23:26

如何降低可重構(gòu)系統(tǒng)的整體功耗?有什么方法能使可重構(gòu)系統(tǒng)的性能和功耗需求之間達(dá)到平衡?

2021-04-08 07:09:23

降低蜂窩手機(jī)功耗并且延長其電池壽命是每一位手機(jī)設(shè)計(jì)工程師的目標(biāo)。設(shè)計(jì)工程師正在不斷將MP3播放器、照相機(jī)以及全運(yùn)動(dòng)視頻等功能加入到現(xiàn)代手機(jī)中,從而需要不斷地將功耗降到最低。

2019-08-23 08:26:40

引言針對中心機(jī)房功耗越來越大的問題,某些電信運(yùn)營商制定了采購設(shè)備功耗每年降低20%的目標(biāo)。半導(dǎo)體是功耗問題的關(guān)鍵所在,其解決方法是重新設(shè)計(jì)芯片實(shí)施和交付方案,而最新一代FPGA可以說是主要的推動(dòng)力

2019-07-31 07:13:26

如何才能實(shí)現(xiàn)降低FPGA設(shè)計(jì)的功耗?

2021-04-29 06:47:38

隨著車載電子設(shè)備越來越多,功耗問題變得日趨嚴(yán)重。例如,如果音頻功率放大器的靜態(tài)電流達(dá)到200ma,則采用12v電源時(shí)靜態(tài)功耗就高達(dá)2.4w。有沒有一種方法能開機(jī)但不需要揚(yáng)聲器發(fā)出聲音的時(shí)候,關(guān)閉放大器來降低功耗?

2023-11-29 08:14:15

節(jié)省功耗的特性的實(shí)現(xiàn)和各種最少功耗數(shù)據(jù)存儲(chǔ)技術(shù)的實(shí)現(xiàn)。除此之外,設(shè)計(jì)中采用一些低功耗技巧,也可以降低靜態(tài)功耗。 IGLOO具有功耗友好的器件架構(gòu),能提供靜態(tài)、睡眠、Flash*Freeze功耗模式

2020-05-13 08:00:00

高低電平翻轉(zhuǎn)跳變沿期間,電流很大,存在較大功耗,所以,降低硬件電路功耗主要是降低電路動(dòng)態(tài)功耗。 (3)采用多CPU系統(tǒng) 盡管現(xiàn)在已有各種可在不過多加重功耗負(fù)擔(dān)的前提下提高性能的技術(shù),但用一個(gè)芯片

2020-07-08 15:52:10

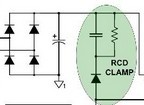

大功率開關(guān)電源降低功耗的技術(shù)方法

2019-03-15 08:54:20

速度和面積等指標(biāo)的優(yōu)化密切相關(guān),需要折中考慮。下面討論常用的低功耗設(shè)計(jì)技術(shù)。 2.1 動(dòng)態(tài)電壓調(diào)節(jié) 由式(1)可知,動(dòng)態(tài)功耗與工作電壓的平方成正比,功耗將隨著工作電壓的降低以二次方的速度降低,因此

2016-06-29 11:28:15

可以做哪些措施來降低功耗

2023-10-23 07:51:09

從當(dāng)前嵌入式消費(fèi)電子產(chǎn)品來看,媒體處理與無線通信、3D游戲逐漸融合,其強(qiáng)大的功能帶來了芯片處理能力的增加,在復(fù)雜的移動(dòng)應(yīng)用環(huán)境中,功耗正在大幅度增加。比如手機(jī),用戶往往希望待機(jī)時(shí)間、聽音樂時(shí)間,以及看MPEG4時(shí)間能更長。在這樣的背景下,如何降低入式芯片的功耗已迫在眉睫。

2019-08-28 08:27:58

從當(dāng)前嵌入式消費(fèi)電子產(chǎn)品來看,媒體處理與無線通信、3D游戲逐漸融合,其強(qiáng)大的功能帶來了芯片處理能力的增加,在復(fù)雜的移動(dòng)應(yīng)用環(huán)境中,功耗正在大幅度增加。比如手機(jī),用戶往往希望待機(jī)時(shí)間、聽音樂時(shí)間,以及看MPEG4時(shí)間能更長。在這樣的背景下,如何降低嵌入式芯片的功耗已迫在眉睫。

2019-09-18 06:22:27

自己做了一個(gè)電路板,因?yàn)?b class="flag-6" style="color: red">功耗除了點(diǎn)問題,怎么降低電路板功耗呢

2019-08-07 22:21:34

從事便攜式或手持產(chǎn)品設(shè)計(jì)的工程師都明白對于如今的設(shè)計(jì),最大限度地降低功耗是必不可少的要求。但是,只有經(jīng)驗(yàn)豐富的工程師理解盡可能地延長系統(tǒng)的電池壽命的那些微妙但又重要的細(xì)節(jié)。本文中我們的重點(diǎn)是,如何使用超低功耗的復(fù)雜可編程邏輯器件(CPLD)?如何在嵌入式設(shè)計(jì)中降低CPLD的功耗?

2019-08-01 08:19:42

怎樣來降低 MSP430 的功耗,請大家來討論下

2014-12-30 18:45:06

降低功耗的最重要的途徑是使用MSP430的時(shí)鐘系統(tǒng)來最大限度地提高M(jìn)SP430處于低功耗模式的時(shí)間。怎樣降低msp430的功耗?

2014-11-09 23:10:18

隨著移動(dòng)電話向著具有豐富媒體功能的無線平臺(tái)發(fā)展,對功率預(yù)算的控制是開發(fā)的重點(diǎn)。降低存儲(chǔ)器的功耗可以顯著延長移動(dòng)電話的電池壽命。為了降低存儲(chǔ)器的功耗,業(yè)界使用了兩種不同的基于DRAM的存儲(chǔ)器架構(gòu):本地

2009-10-08 15:53:49

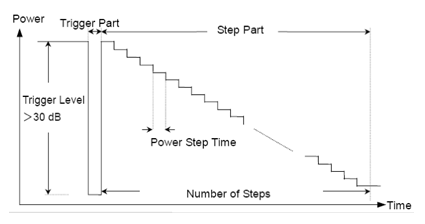

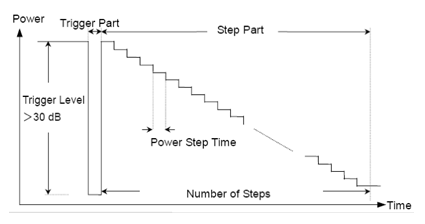

~1Gb/s的數(shù)據(jù)率以及支持OFDMA調(diào)制、支持MIMO天線技術(shù),乃至支持VoWLAN的組網(wǎng),因此,在射頻信號(hào)鏈設(shè)計(jì)的過程中,如何降低射頻功率放大器的功耗及提升效率成為了半導(dǎo)體行業(yè)的競爭焦點(diǎn)之一。目前行業(yè)發(fā)展呈現(xiàn)三條技術(shù)路線,本文就這三條技術(shù)路線進(jìn)行簡要的比較。

2019-07-05 06:29:06

降低功耗不光能夠大大的節(jié)約電能還能簡化電源部分的設(shè)計(jì),甚至可以用于手持設(shè)備上面使用,這些都已經(jīng)越來越成為未來產(chǎn)品的設(shè)計(jì)方向。

2021-02-26 07:27:17

時(shí)可以使用多線程下載方式,縮短了下載的時(shí)間,減少了WiFi開啟時(shí)間,及CPU的數(shù)據(jù)處理時(shí)間,相比單線程的低性能下載還是可以節(jié)省不少的功耗。Android應(yīng)用軟件采用不同的邏輯代碼編寫,能否降低功耗

2018-09-19 18:11:19

液晶顯示(LCD)技術(shù)的基本原理是什么?液晶顯示(LCD)噪聲產(chǎn)生的原因是什么?有什么方法可以降低LCD的噪聲?

2021-05-31 06:08:04

電源門控可以降低泄漏功耗嗎?有哪幾種情況采用PG能顯著減小泄漏功耗呢?

2022-02-11 06:34:36

方法 通過分析功耗產(chǎn)生的原因,可以判斷降低功耗受到很多約束,需要在各個(gè)要素之間反復(fù)衡量。數(shù)字IC低功耗的設(shè)計(jì)應(yīng)該從頂層到底層各個(gè)階段進(jìn)行優(yōu)化,如工藝級(jí)低功耗技術(shù)、電路級(jí)低功耗技術(shù)、RTL級(jí)(寄存器

2020-07-07 11:40:06

行為邏輯層次低功耗設(shè)計(jì)前言:隨著集成電路制造技術(shù)的快速發(fā)展,未來單一硅片上集成的晶體管數(shù)將超過lO億以上。這使得功耗問題變得越來越突出,將成為影響電路性能的關(guān)鍵問題。關(guān)鍵詞:低功耗設(shè)計(jì)SOC邏輯

2013-05-16 20:00:33

什么是TICKLESS?怎么能實(shí)現(xiàn)功耗的降低呢?TICKLESS是如何去實(shí)現(xiàn)功耗降低的呢?

2022-02-24 08:02:02

stm32進(jìn)入低功耗模式,必須用中斷來喚醒,現(xiàn)在就是不用這種模式,如何通過程序來降低功耗啊

2019-05-06 18:43:22

如何利用FPGA設(shè)計(jì)技術(shù)降低功耗?

2021-04-13 06:16:21

隨著車載電子設(shè)備越來越多,功耗問題變得日趨嚴(yán)重。例如,如果音頻功率放大器的靜態(tài)電流達(dá)到200ma,則采用12v電源時(shí)靜態(tài)功耗就高達(dá)2.4w。有沒有一種方法能開機(jī)但不需要揚(yáng)聲器發(fā)出聲音的時(shí)候,關(guān)閉放大器來降低功耗?

2018-08-06 08:23:20

降低顯示功耗來延長移動(dòng)電池壽命

2021-04-02 07:29:21

在嵌入式設(shè)計(jì)中降低CPLD的功耗

本文中我們將重點(diǎn)放在這些經(jīng)驗(yàn)豐富的專家是如何使用超低功耗的復(fù)雜可編程邏輯器件(CPLD),并從他們的嵌入式設(shè)計(jì)中的I/O子系

2010-04-12 10:04:02 27

27 利用先進(jìn)的校準(zhǔn)測試方法降低移動(dòng)設(shè)備的成本

如今消費(fèi)者利用10年前連聽都沒有聽說過的各種方式使用移動(dòng)設(shè)備已是很平常的事情了。無論是在他們喜愛

2009-04-05 12:57:58 690

690

降低藍(lán)牙裝置的功耗的方法

在2004年11月,Bluetooth SIG修訂了 2.0+ Enhanced Data Rate (EDR)規(guī)格,結(jié)合一種革命性的技術(shù),創(chuàng)造出更有效率

2010-03-05 14:34:48 1031

1031

的主要原因,但并非唯一因素,而且通過晶體管來降低功耗作用是有限的。通過更全面的系統(tǒng)級(jí)方法能夠更有效地降低功耗。只有全面兼顧芯片工藝技術(shù),充分發(fā)揮功率感知型 (power-aware tool)工具的作用

2017-11-24 18:37:33 1368

1368 們已經(jīng)開發(fā)出一系列的創(chuàng)新技術(shù),以用于減輕目前所面臨的問題,并可望對振興未來的芯片產(chǎn)業(yè)有所助益。 以下討論五種可用于降低未來IC功耗的技術(shù)。這些技術(shù)目前已經(jīng)在開發(fā)中,可望共同解決未來十年內(nèi)將會(huì)面臨的功耗問題。 擁抱協(xié)

2017-11-30 11:32:01 503

503

概率功耗估算方法和條件概率功耗估算方法估算的功耗作為優(yōu)化的成本函數(shù)時(shí),由于方法本身的局限性或忽略了電路節(jié)點(diǎn)特點(diǎn)會(huì)降低估算結(jié)果的準(zhǔn)確度,從而影響功耗優(yōu)化結(jié)果。針對上述問題,提出一種新的電路功耗估算方法

2018-03-12 16:24:05 0

0 我們首先來了解在嵌入式設(shè)計(jì)中如何降低CPLD的功耗、電路板的面積和元器件成本。下一步,我們將看到在待機(jī)模式下如何盡量降低CPLD的功耗,不僅要仔細(xì)地選擇器件,而且還要選擇一個(gè)合適的總線駐留方案。器件工作期間,我們對節(jié)省功耗的探討將包括選擇邏輯門、智能I/O設(shè)計(jì)和精密的電源電壓管理技術(shù)。

2018-12-04 09:09:00 2142

2142

設(shè)計(jì)人員總是在尋找減少不需要的功耗組件的方法,無論是通過以低功耗技術(shù)的方式設(shè)計(jì)設(shè)計(jì),還是采用可以降低功耗的工藝。但是,其中一些解決方案的代價(jià)是性能,可靠性,芯片面積或其中的幾個(gè)。最終,人們必須在功率,性能和成本之間達(dá)成妥協(xié)。下面的文章旨在討論其中的一些技巧。這些技術(shù)分為建筑技術(shù)和基于過程的技術(shù)。

2019-08-09 14:32:55 14246

14246

傳統(tǒng)上,降低軟件無線電(SDR)硬件的功耗一直是我們工作的重點(diǎn),但是,顯而易見軟件也有重要影響,因此,需要一種降低 SDR功耗的整體設(shè)計(jì)方法。一種能發(fā)揮SDR功能的測試床能幫我們解決這個(gè)問題。由于像美國聯(lián)合戰(zhàn)術(shù)無線電系統(tǒng)(JTRS)這樣的計(jì)劃,軟件定義的無線電(SDR)早已被證實(shí)。

2020-10-20 10:42:00 0

0 ,導(dǎo)致人工成本過高。 因此,如何降低LoRa節(jié)點(diǎn)的功耗,是本領(lǐng)域常見的技術(shù)追求。 本文介紹數(shù)據(jù)速率DR和LoRa節(jié)點(diǎn)功耗的關(guān)系,從而介紹一種顯著降低LoRa節(jié)點(diǎn)功耗的方法。 想了解更完整的LoRa節(jié)點(diǎn)低功耗策略,可以參見文章LoRa終端低功耗策略。 如果想

2020-10-26 15:21:36 1786

1786 clock) 是通過在時(shí)鐘路徑上增加邏輯門對時(shí)鐘進(jìn)行控制,使電路的部分邏輯在不需要工作時(shí)停止時(shí)鐘樹的翻轉(zhuǎn),而并不影響原本的邏輯狀態(tài)。在ASIC和FPGA設(shè)計(jì)中都存在門控時(shí)鐘的概念(前者應(yīng)用更廣)。 典型的門控時(shí)鐘邏輯如下圖所示: 二、門控時(shí)鐘降低功耗

2021-09-23 16:44:47 12192

12192

1、如何降低功耗?

(1) 優(yōu)化方向:

組合邏輯+時(shí)序邏輯+存儲(chǔ)

(2) 組合邏輯:

??(a)通過算法優(yōu)化的方式減少門電路

??(b)模塊復(fù)用、資源共享

(3) 時(shí)序邏輯:

??(a)盡量減少無用

2022-02-11 15:30:36 2

2 很明顯。對于消費(fèi)級(jí)芯片(如手機(jī)CPU,IoT芯片等),由于往往應(yīng)用在小型移動(dòng)設(shè)備中,低功耗設(shè)計(jì)就顯得尤為重要。

2022-08-17 11:04:42 5816

5816 邏輯系統(tǒng)設(shè)計(jì)技術(shù)降低開關(guān) CMOS 功耗

2022-11-15 20:05:46 0

0 如何降低設(shè)備功耗,降低采集設(shè)備功耗的幾種方法 工程監(jiān)測傳感器 以下是降低數(shù)采設(shè)備功耗的一些方法: 優(yōu)化硬件設(shè)計(jì):通過選擇低功耗的芯片、使用更高效的轉(zhuǎn)換器、減少功率損耗等方式來優(yōu)化硬件設(shè)計(jì),從而降低功耗

2023-10-11 09:29:00 511

511

電子發(fā)燒友App

電子發(fā)燒友App

評論