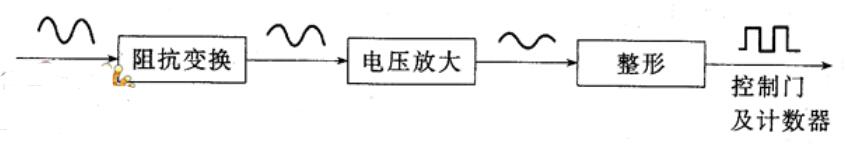

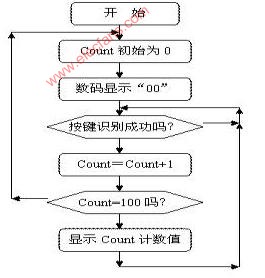

計數器應用實例

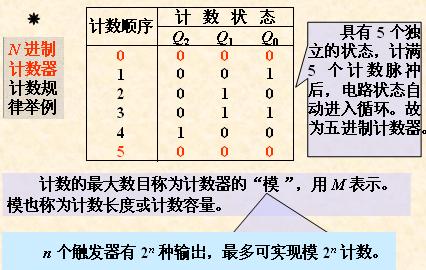

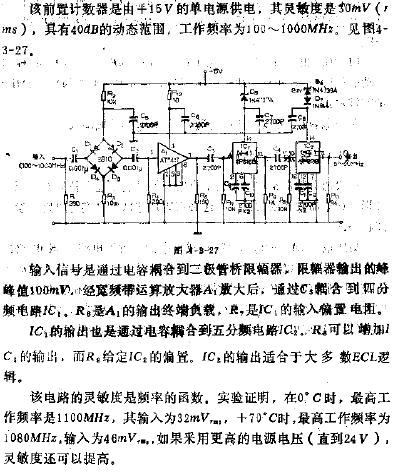

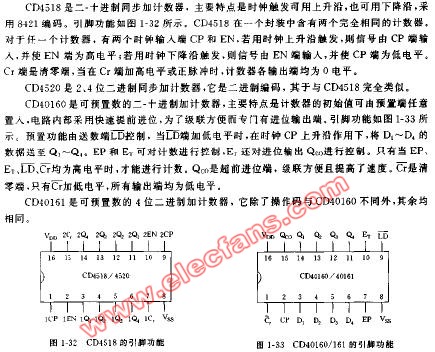

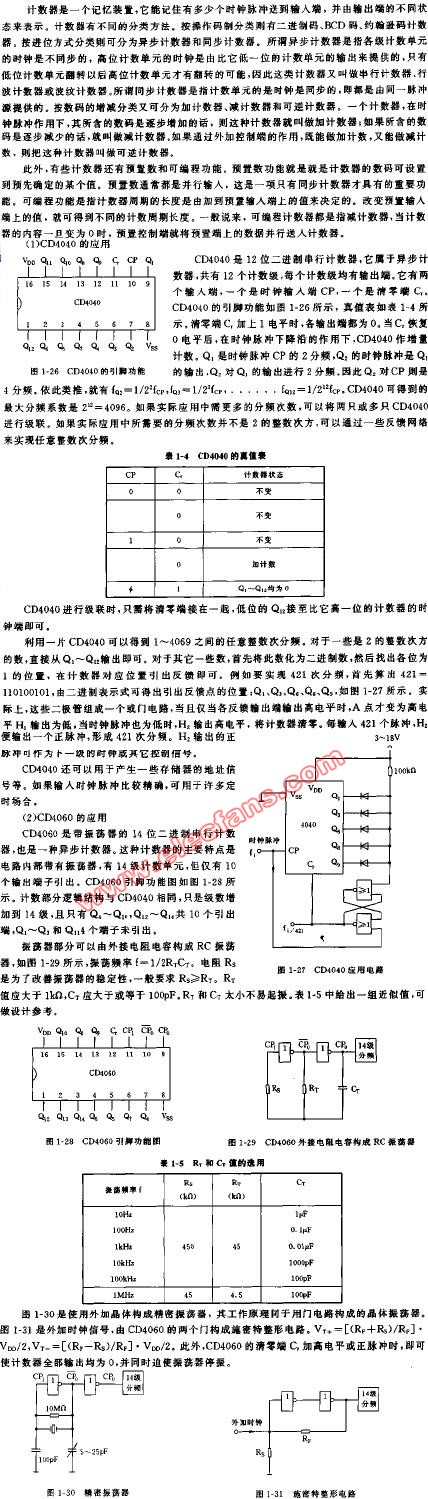

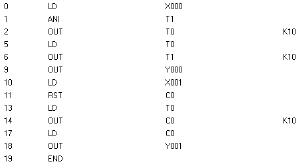

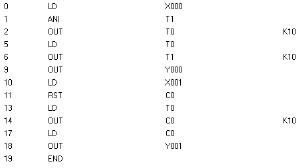

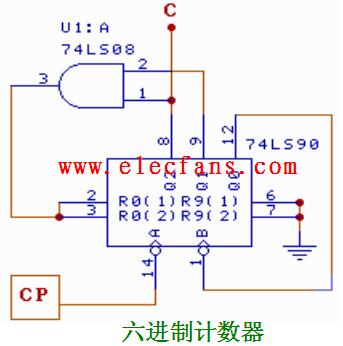

除了計數功能外,計數器產品還有一些附加功能,如異步復位、預置數(注意,有同步預置數和異步預置數兩種。前者受時鐘脈沖控制,后者不受時鐘脈沖控制)、保持(注意,有保持進位和不保持進位兩種)。雖然計數器產品一般只有二進制和十進制兩種,有了這些附加功能,我們就可以方便地用我們可以得到的計數器來構成任意進制的計數器。下面我們舉兩個例子。在這兩個例子中,我們分別用同步十進制加法計數器74LS160構成一個六進制計數器和一個一百進制計數器。

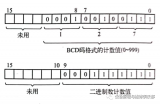

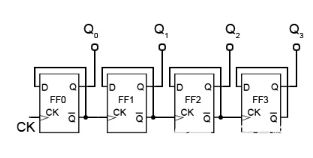

因為六進制計數器的有效狀態有六個,而十進制計數器的有效狀態有十個,所以用十進制計數器構成六進制計數器時,我們只需保留十進制計數器的六個狀態即可。74LS160的十個有效狀態是BCD編碼的,即0000、0001、0010、0011、0100、0101、0110、0111、1000、1001[圖5-1]。

圖5-1

我們保留哪六個狀態呢?理論上,我們保留哪六個狀態都行。然而,為了使電路最簡單,保留哪六個狀態還是有一點講究的。一般情況下,我們總是保留0000和1001兩個狀態。因為74LS160從1001變化到0000時,將在進位輸出端產生一個進位脈沖,所以我們保留了0000和1001這兩個狀態后,我們就可以利用74LS160的進位輸出端作為六進制計數器的進位輸出端了。于是,六進制計數器的狀態循環可以是0000、0001、0010、0011、0100和1001,也可以是0000、0101、0110、0111、1000和1001。我們不妨采用0000、0001、0010、0011、0100和1001這六個狀態。

如何讓74LS160從0100狀態跳到1001狀態呢?我們用一個混合邏輯與非門構成一個譯碼器[圖5.3.37b],當74LS160的狀態為0100時,與非門輸出低電平,這個低電平使74LS160工作在預置數狀態,當下一個時鐘脈沖到來時,由于![]() 等于1001,74LS160就會預置成1001,從而我們實現了狀態跳躍。

等于1001,74LS160就會預置成1001,從而我們實現了狀態跳躍。

圖5.3.37b 用置數法將74160接成六進制計數器(置入1001)

比這個方案稍微繁瑣一點的是利用74LS160的異步復位端。下面這個電路中[圖5.3.34],也有一個由混合邏輯與非門構成的譯碼器。

圖5.3.34 用置零法將74LS160接成六進制計數器

不過,這個譯碼器當輸入為0110時才輸出低電平,使74LS160異步復位,進入0000這個狀態。從0000狀態開始,隨著時鐘脈沖的不斷到來,74LS160依次變為0001、0010、0011、0100、0101、和0110狀態[圖5-2]。可能有人說:“不對!這個電路總共有七個狀態,應該是七進制計數器呀!”我們說,這個電路雖然要經歷七個狀態,但是只需六個脈沖就完成一個計數循環,因此它仍是六進制計數器。

圖5-2

我們仔細分析一下。假設74LS160的初始狀態為0000,第一個時鐘脈沖到達后,它的狀態變為0001,第二個時鐘脈沖到達后,它的狀態變為0010,……,第五個時鐘脈沖到達后,它的狀態變為0101,第六個時鐘脈沖到達后,它的狀態變為0110。當74LS160處于0110這個狀態時,譯碼器輸出低電平,使74LS160異步復位,進入0000這個狀態。這段話里,“異步復位”是一個關鍵詞。與同步復位不同,異步復位不受時鐘脈沖的控制。于是,譯碼器的輸出剛變成低電平,74LS160的狀態就變成了0000。理想情況下,74LS160在第六個時鐘周期內首先在0110狀態停留片刻,然后就穩定地停留在0000狀態。我們知道,計數器的工作對象是時鐘脈沖。計數,就是計時鐘脈沖的個數。在我們這個例子中,74LS160從0000狀態出發,經過六個(而不是七個)時鐘周期又回到了0000狀態,也就是說,每六個(而不是七個)時鐘脈沖就使74LS160的狀態循環一次。因此,這個電路是一個六進制計數器。計數循環中包括0000、0001、0010、0011、0100和0101這六個穩定狀態。可能有人說:“唔,聽你這么一解釋,我也覺得它是六進制計數器。不過,把七個狀態算成六個總是有點兒別扭。唉,只要它能工作,我就不計較它是經歷六個狀態還是七個狀態了。”我說:“對,我也這樣想。然而,事與愿違呀!不改進的話,這個電路還真不能工作。”為什么呢?我們知道,計數器的狀態是觸發器記憶的。74LS160有四個觸發器![]() ,分別記憶

,分別記憶![]() 。這四個觸發器的工作速度是有差異的。在74LS160從0110變成0000的過程中,

。這四個觸發器的工作速度是有差異的。在74LS160從0110變成0000的過程中,![]() 和

和![]() 的狀態不變,

的狀態不變,![]() 和

和![]() 的狀態要從1變成0。我們假設

的狀態要從1變成0。我們假設![]() 比

比![]() 快,那么

快,那么![]() 剛剛從1變0時,

剛剛從1變0時,![]() 仍然處于1狀態。這時,譯碼器的輸出就不是低電平了,74LS160的異步復位信號就消失了。在異步復位信號持續時間過短的情況下,

仍然處于1狀態。這時,譯碼器的輸出就不是低電平了,74LS160的異步復位信號就消失了。在異步復位信號持續時間過短的情況下,![]() 將保持1狀態不變。于是74LS160將停留在0010狀態,而不是我們期望的0000狀態。顯然,這是一種競爭冒險現象,因為74LS160是否能夠從0110變成0000取決于

將保持1狀態不變。于是74LS160將停留在0010狀態,而不是我們期望的0000狀態。顯然,這是一種競爭冒險現象,因為74LS160是否能夠從0110變成0000取決于![]() 和

和![]() 的競爭結果。怎樣使異步復位信號持續足夠長的時間呢?我們來看看這個電路[圖5.3.36]。

的競爭結果。怎樣使異步復位信號持續足夠長的時間呢?我們來看看這個電路[圖5.3.36]。

圖5.3.36? 圖5.3.34電路的改進

兩個與非門構成了RS鎖存器,以它的![]() 端輸出的低電平作為74LS160的異步復位信號。若74LS160從0000狀態開始計數,則第六個時鐘脈沖上升沿到達時進入0110狀態,使RS鎖存器置位,

端輸出的低電平作為74LS160的異步復位信號。若74LS160從0000狀態開始計數,則第六個時鐘脈沖上升沿到達時進入0110狀態,使RS鎖存器置位,![]() 端輸出低電平。74LS160在0110狀態作短暫停留后,迅速轉入其它狀態,如0010或0100,譯碼器輸出的負脈沖消失。如果我們把這個窄脈沖直接作為74LS160的異步復位信號,計數器不一定能夠可靠地工作。如果我們把這個窄脈沖作為RS鎖存器的置位信號,把時鐘脈沖作為RS鎖存器的復位信號,再將RS鎖存器的

端輸出低電平。74LS160在0110狀態作短暫停留后,迅速轉入其它狀態,如0010或0100,譯碼器輸出的負脈沖消失。如果我們把這個窄脈沖直接作為74LS160的異步復位信號,計數器不一定能夠可靠地工作。如果我們把這個窄脈沖作為RS鎖存器的置位信號,把時鐘脈沖作為RS鎖存器的復位信號,再將RS鎖存器的![]() 作為74LS160的異步復位信號,計數器一定能夠可靠地工作,因為

作為74LS160的異步復位信號,計數器一定能夠可靠地工作,因為![]() 輸出的負脈沖的寬度與時鐘脈沖高電平的持續時間相等。

輸出的負脈沖的寬度與時鐘脈沖高電平的持續時間相等。

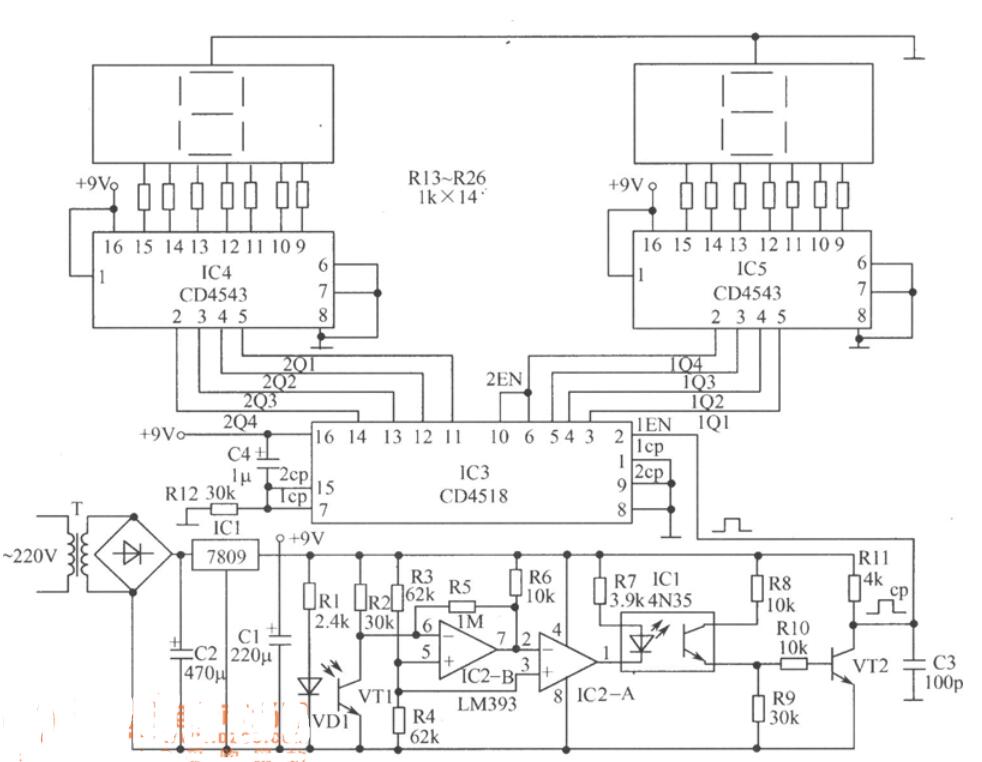

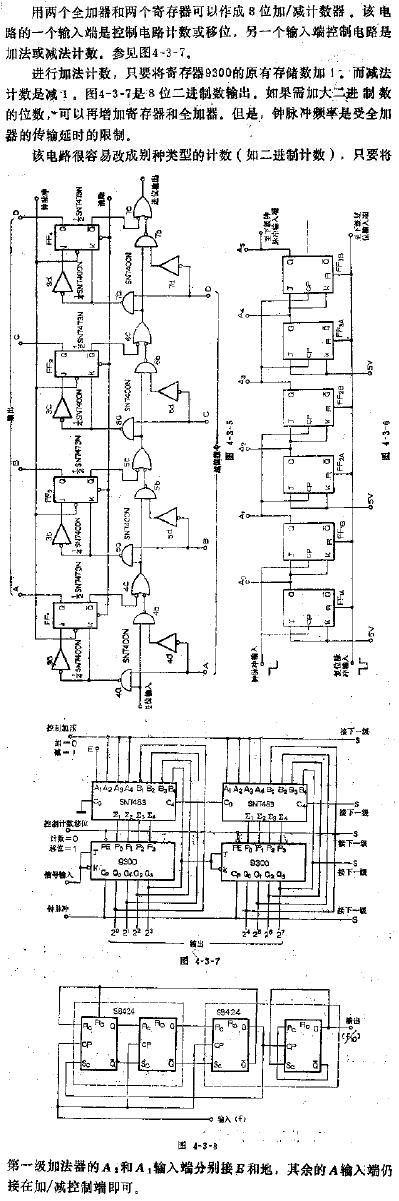

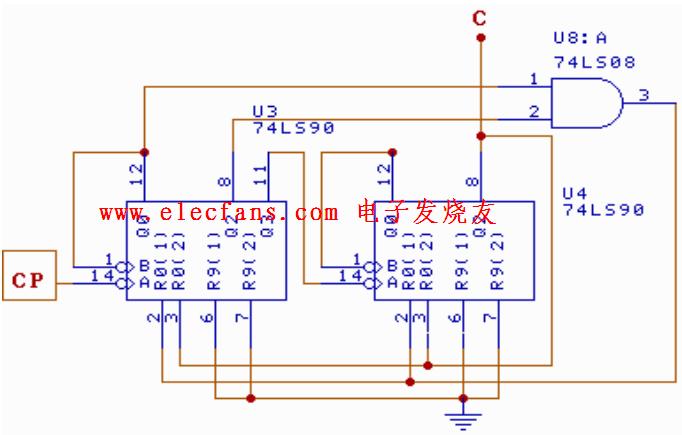

第二個例子要求我們構成一百進制計數器,也就是說,計數器的狀態為0010到9910。因為100等于10乘以10,所以我們可以用兩個74LS160構成一個一百進制計數器,其中一個計數器的狀態表示個位數,另一個計數器的狀態表示十位數,后者在前者的進位信號控制下計數。我們有兩種方案。第一種方案稱為并行進位方式[圖5.3.39]。

圖5.3.39 例5.3.3電路的并行進位方式

這種方案的特點是兩個74LS160的CP端都接到時鐘脈沖上。不過,第一個74LS160始終工作在計數方式,每一個時鐘脈沖都使其狀態發生變化;第一個74LS160只有在第一個74LS160進位輸出為高電平是才工作在計數方式,每十個時鐘脈沖才使其狀態發生變化。若計數器從0010狀態開始計數,則第九個時鐘脈沖到達后,第一個74LS160的狀態變為910且進位輸出變為高電平,使第二個74LS160進入計數方式。因為第二個74LS160進入計數方式的時間比第九個時鐘脈沖到達的時間晚,就是說,第九個時鐘脈沖到達時第二個74LS160尚未進入計數方式,所以,第九個時鐘脈沖并不能使第二個74LS160的狀態發生變化,其狀態仍為010。于是,計數器的狀態為0910。第十個時鐘脈沖到達后,第一個74LS160的狀態變為010且進位輸出變為低電平,使第二個74LS160退出計數方式。因為第二個74LS160退出計數方式的時間比第十個時鐘脈沖到達的時間晚,就是說,第十個時鐘脈沖到達時第二個74LS160尚未退出計數方式,所以,第十個時鐘脈沖使第二個74LS160的狀態發生變化,其狀態變為110。于是,計數器的狀態為1010。第二種方案稱為串行進位方式,這種方案的特點是,兩個74LS160都始終工作在計數方式。不過,第一個74LS160的CP端接到時鐘脈沖上,每一個時鐘脈沖都使其狀態發生變化;第一個74LS160的CP端接到第一個74LS160進位輸出上,每十個時鐘脈沖才使其狀態發生變化。經常有學生問:“為什么在第一個74LS160的進位輸出端和第二個74LS160的時鐘脈沖輸入端之間要加上一個非門呢?”這里面有點兒奧妙。若計數器從0010狀態開始計數,則第九個時鐘脈沖到達后,第一個74LS160的狀態變為910且進位輸出變為高電平。如果沒有這個非門,第一個74LS160的進位輸出端的電平變化將使第二個74LS160的狀態發生變化,其狀態變為110。于是計數器的狀態就從0810變成1910,而不是我們所希望的0910。有了這個非門,情況就不一樣了,因為第一個74LS160的進位輸出端的脈沖上升沿被非門轉換成下降沿,所以第一個74LS160的進位輸出端的電平變化并不能使第二個74LS160的狀態發生變化,其狀態仍為010。于是計數器的狀態就從0810變成我們所希望的0910。第十個時鐘脈沖到達后,第一個74LS160的狀態變為010且進位輸出變為低電平。因為第一個74LS160的進位輸出端的脈沖下降沿被非門轉換成上升沿,所以第一個74LS160的進位輸出端的電平變化使第二個74LS160的狀態發生變化,其狀態變為110。于是計數器的狀態又從0910變成1010。

我們再舉一個用74LS160構成二十九進制計數器的例子。因為29是一個素數,除了1和它本身外,不能表達為兩個整數的乘積,所以我們要把工作分解成兩個步驟。第一步,我們用兩個十進制計數器構成一個一百進制計數器;第二步,我們用這個一百進制計數器構成二十九進制計數器。第一步可以采用并行進位方式或串行進位方式實現;第二步可以用置位法或復位法實現。因為這里要對兩個74LS160同時置位或復位,所以也稱為整體置位法或整體復位法。

電子發燒友App

電子發燒友App

評論