在具有電阻、電感和電容的電路里,對(duì)交流電所起的阻礙作用叫做阻抗。阻抗匹配是微波電子學(xué)里的一部分,主要用于傳輸線上,來達(dá)到所有高頻微波信號(hào)都能傳至負(fù)載的目的,不會(huì)有

2012-03-06 16:27:09 1420

1420 為保證信號(hào)傳輸質(zhì)量、降低EMI干擾、通過相關(guān)的阻抗測試認(rèn)證,需要對(duì)PCB關(guān)鍵信號(hào)進(jìn)行阻抗匹配設(shè)計(jì)。本設(shè)計(jì)指南是綜合常用計(jì)算參數(shù)、電視機(jī)產(chǎn)品信號(hào)特點(diǎn)、PCB Layout實(shí)際需求、SI9000軟件計(jì)算

2020-11-02 14:05:20 11194

11194 100M到200M的ADC在PCB設(shè)計(jì)時(shí),要進(jìn)行嚴(yán)格的阻抗匹配么?有沒有一些標(biāo)準(zhǔn)性的文檔來說明呢

2023-12-05 06:30:10

50歐的阻抗匹配電路,哪個(gè)有,參考下。

2019-09-20 09:53:37

一、0歐電阻在電路中的作用1.PCB上走線需要。如果PCB上布線時(shí),時(shí)在無法繞過可以用一個(gè)0歐電阻器跨過。2.預(yù)留電流測量口。因?yàn)闇y量電流時(shí)需要斷開銅箔電路,此時(shí)可以在銅箔電路中預(yù)先留一個(gè)測量口

2015-07-19 09:47:18

0歐電阻 0歐電阻,即電阻標(biāo)值為0歐姆的電阻稱為0歐電阻。是一種理想電阻,多用于PCB設(shè)計(jì)等方面定義電阻標(biāo)值為0歐姆的電阻稱為0歐電阻。首先大家應(yīng)該了解,0歐電阻是理想狀態(tài)下才有的,現(xiàn)實(shí)中是不存在

2016-01-07 11:20:02

需要阻抗匹配,這個(gè)阻抗匹配串聯(lián)一個(gè)50歐姆的電阻?或者要求PCB制作廠家按50歐姆的阻抗要求制作效果是一樣的?請(qǐng)高手指導(dǎo),謝謝!

2015-05-02 17:26:17

PCB工程師每天會(huì)遇到不同的問題,而我們要解決的就是阻抗匹配這一問題。很多人對(duì)這個(gè)問題不是很清楚,到底什么是阻抗匹配?阻抗匹配重要性在哪里?阻抗匹配的方法又有哪些?下面就從這三點(diǎn)來深度剖析。對(duì)電路中

2020-11-02 07:20:49

開發(fā)了。平常我們?cè)?DIY 的過程中,一般很少會(huì)用到 0 歐電阻,但是對(duì)于電路板上的它來說,我們也要理解它的作用。下面總結(jié)一下 0 歐姆的多種用途:1、在電路中沒有任何功能,只是在 PCB 上為了調(diào)試

2020-10-09 17:15:27

阻抗匹配。串行電阻的阻值為20~75Ω,阻值大小與信號(hào)頻率成正比,與PCB走線寬度和長度成反比。在嵌入式系統(tǒng)中,一般頻率大于20M的信號(hào),PCB走線長度大于5cm時(shí)都要加串行匹配電阻,例如系統(tǒng)中的時(shí)鐘信號(hào)

2019-02-14 14:50:45

。(5)在高頻信號(hào)網(wǎng)絡(luò)中,充當(dāng)電感或電容(起阻抗匹配作用,0歐電阻也有阻抗!)。充當(dāng)電感用時(shí),主要是解決EMC問題。(6)單點(diǎn)接地,例如模擬地與數(shù)字地的單點(diǎn)對(duì)接共地。(7)配置電路,可以取代跳線和撥碼

2018-11-15 20:07:35

。(5)在高頻信號(hào)網(wǎng)絡(luò)中,充當(dāng)電感或電容(起阻抗匹配作用,0歐電阻也有阻抗!)。充當(dāng)電感用時(shí),主要是解決EMC問題。(6)單點(diǎn)接地,例如模擬地與數(shù)字地的單點(diǎn)對(duì)接共地。(7)配置電路,可以取代跳線和撥碼

2019-01-02 10:30:00

。(5)在高頻信號(hào)網(wǎng)絡(luò)中,充當(dāng)電感或電容(起阻抗匹配作用,0歐電阻也有阻抗!)。充當(dāng)電感用時(shí),主要是解決EMC問題。(6)單點(diǎn)接地,例如模擬地與數(shù)字地的單點(diǎn)對(duì)接共地。(7)配置電路,可以取代跳線和撥碼

2022-05-16 16:15:03

加一個(gè)0歐的電阻起跨接作用。 (5)在高頻信號(hào)網(wǎng)絡(luò)中,充當(dāng)電感或電容(起阻抗匹配作用,0歐電阻也有阻抗!)。充當(dāng)電感用時(shí),主要是解決EMC問題。 (6)單點(diǎn)接地,例如模擬地與數(shù)字地的單點(diǎn)對(duì)接共

2014-07-04 14:00:27

如何理解PCB設(shè)計(jì)中傳輸線阻抗匹配問題,以及傳輸線阻抗不匹配所引起的問題?求解,謝謝

2016-04-13 17:13:56

電阻的選定一般是要符合阻抗匹配的。電阻的主要作用是阻抗匹配,所以要清楚輸出級(jí)的輸出阻抗、輸入級(jí)的輸入阻抗,然后用一個(gè)電阻或電阻網(wǎng)絡(luò)去匹配。當(dāng)然,現(xiàn)在的集成電路阻抗匹配范圍很寬,很容易匹配。在高頻

2019-07-18 21:05:08

器.================================================================================阻抗匹配概念阻抗匹配是指負(fù)載阻抗與激勵(lì)源內(nèi)部阻抗互相適配,得到最大功率輸出的一種工作狀態(tài)。對(duì)于不同特性的電路,匹配條件是不一樣的。在純電阻電路中,當(dāng)負(fù)載電阻等于激勵(lì)源內(nèi)阻時(shí),則輸出功率為

2016-07-29 13:56:25

阻抗匹配中的Hyperlynx應(yīng)用阻抗匹配中的Hyperlynx

2008-07-17 13:47:49

說:阻抗是電阻與電抗在向量上的和。對(duì)于一個(gè)具體器件,阻抗不是不變的,而是隨著頻率變化而變化。在電阻、電感和電容串聯(lián)電路中,電路的阻抗一般來說比電阻大。阻抗匹配,信號(hào)源內(nèi)阻與所接傳輸線的特性阻抗大小相等且相位

2017-06-01 09:08:23

,但我們可以拿它來理解負(fù)載不匹配時(shí)的反射情況。高速PCB設(shè)計(jì)中的阻抗匹配(資料整理)阻抗匹配阻抗匹配是指在能量傳輸時(shí),要求負(fù)載阻抗要和傳輸線的特征阻抗相等,此時(shí)的傳輸不會(huì)產(chǎn)生反射,這表明所有能量都被負(fù)載

2019-06-19 02:34:01

內(nèi)部阻抗互相適配,得到最大功率輸出的一種工作狀態(tài)。對(duì)于不同特性的電路,匹配條件是不一樣的。在純電阻電路中,當(dāng)負(fù)載電阻等于激勵(lì)源內(nèi)阻時(shí),則輸出功率為最大,這種工作狀態(tài)稱為匹配,否則稱為失配。 當(dāng)激勵(lì)源

2014-12-01 10:37:44

PCB設(shè)計(jì)中的阻抗匹配(資料整理)阻抗匹配阻抗匹配是指在能量傳輸時(shí),要求負(fù)載阻抗要和傳輸線的特征阻抗相等,此時(shí)的傳輸不會(huì)產(chǎn)生反射,這表明所有能量都被負(fù)載吸收了。反之則在傳輸中有能量損失。在高速PCB設(shè)計(jì)中

2019-02-15 22:28:25

)。即,當(dāng)負(fù)載電阻跟信號(hào)源內(nèi)阻相等時(shí),負(fù)載可獲得最大輸出功率,這就是我們常說的阻抗匹配之一。對(duì)于純電阻電路,此結(jié)論同樣適用于低頻電路及高頻電路。當(dāng)交流電路中含有容性或感性阻抗時(shí),結(jié)論有所改變,就是需要

2019-05-31 07:11:29

阻抗匹配的原理與應(yīng)用阻抗匹配是指負(fù)載阻抗與激勵(lì)源內(nèi)部阻抗互相適配, 使激勵(lì)源得到最大功率翰出的一種工作狀態(tài)。對(duì)于不同特性的電路, 匹配條件是不一樣的。在純電阻電路中, 當(dāng)負(fù)載電阻等于激勵(lì)源內(nèi)阻

2009-11-20 10:44:36

上所有高頻的微波信號(hào)皆能傳至負(fù)載點(diǎn)上,并不會(huì)有信號(hào)反射回來源點(diǎn),進(jìn)而提高了能源效益。本文我們將介紹PCB設(shè)計(jì)知識(shí)中有關(guān)阻抗匹配的一些研究。 一阻抗匹配的研究 在高速的設(shè)計(jì)中,阻抗的匹配與否關(guān)系到

2011-04-11 09:55:40

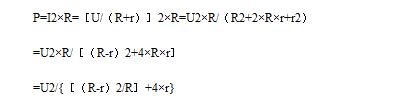

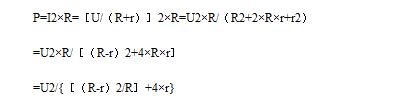

時(shí),(R-r)2/R可取得最小值0,這時(shí)負(fù)載電阻R上可獲得最大輸出功率Pmax=U2/(4×r)。即,當(dāng)負(fù)載電阻跟信號(hào)源內(nèi)阻相等時(shí),負(fù)載可獲得最大輸出功率,這就是我們常說的阻抗匹配之一。對(duì)于純電阻電路,此結(jié)論

2019-05-29 07:02:08

這里面為什么要接一個(gè)阻抗變換運(yùn)放?為什么要進(jìn)行阻抗匹配。接了對(duì)共模抑制為什么有幫助呢?阻抗匹配網(wǎng)上說避免自激振蕩,減小高頻噪聲。總是理解不了所以想問問論壇的大神們給我講講你對(duì)阻抗匹配的理解以及現(xiàn)實(shí)中關(guān)于阻抗匹配的一些使用。

2017-08-02 22:06:16

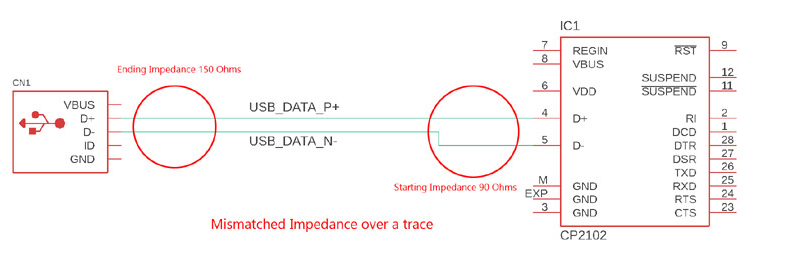

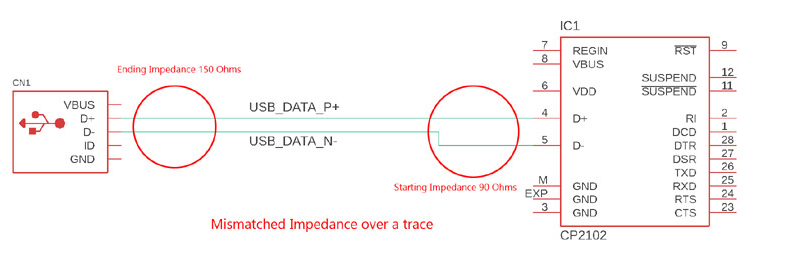

請(qǐng)教下大家USB之類的差分線的需要阻抗匹配90歐姆,但一般好像都會(huì)串個(gè)22歐的電阻,那線的阻抗是做成90-20=70歐的還是仍做90歐的?還有就是串個(gè)電阻后走線就被電阻從中間分成了兩段,需要和制版廠分別說這兩段每一段做45歐這樣嗎?求各位大佬指點(diǎn)迷津

2022-08-09 18:54:27

高頻信號(hào)網(wǎng)絡(luò)中,充當(dāng)電感或電容(起阻抗匹配作用,0歐電阻也有阻抗!)。充當(dāng)電感用時(shí),主要是解決EMC問題。(6)單點(diǎn)接地,例如模擬地與數(shù)字地的單點(diǎn)對(duì)接共地。(7)配置電路,可以取代跳線和撥碼開關(guān)。有時(shí)

2018-11-19 13:39:51

,但我們可以拿它來理解負(fù)載不匹配時(shí)的反射情況。高速PCB設(shè)計(jì)中的阻抗匹配(資料整理)阻抗匹配阻抗匹配是指在能量傳輸時(shí),要求負(fù)載阻抗要和傳輸線的特征阻抗相等,此時(shí)的傳輸不會(huì)產(chǎn)生反射,這表明所有能量都被負(fù)載

2018-05-21 16:59:18

阻抗匹配是指在能量傳輸時(shí),要求負(fù)載阻抗要和傳輸線的特征阻抗相等,此時(shí)的傳輸不會(huì)產(chǎn)生反射,這表明所有能量都被負(fù)載吸收了。反之則在傳輸中有能量損失。在高速PCB設(shè)計(jì)中,阻抗的匹配與否關(guān)系到信號(hào)的質(zhì)量優(yōu)劣。

2019-06-03 08:03:18

與內(nèi)阻必須滿足共扼關(guān)系,即電阻成份相等,電抗成份只數(shù)值相等而符號(hào)相反。這種匹配條件稱為共扼匹配。 一.阻抗匹配的研究 在高速的設(shè)計(jì)中,阻抗的匹配與否關(guān)系到信號(hào)的質(zhì)量優(yōu)劣。阻抗匹配的技術(shù)可以說是豐富多樣

2014-12-01 10:41:00

信號(hào)或廣泛電能在傳輸過程中,為實(shí)現(xiàn)信號(hào)的無反射傳輸或最大功率傳輸,要求電路連接實(shí)現(xiàn)阻抗匹配。阻抗匹配關(guān)系著系統(tǒng)的整體性能,實(shí)現(xiàn)匹配可使系統(tǒng)性能達(dá)到最優(yōu)。阻抗匹配的概念應(yīng)用范圍廣泛,阻抗匹配常見于各級(jí)

2019-08-20 07:23:39

才會(huì)說:阻抗是電阻與電抗在向量上的和。阻抗匹配是指負(fù)載阻抗與激勵(lì)源內(nèi)部阻抗互相適配,得到最大功率輸出的一種工作狀態(tài)。對(duì)于不同特性的電路,匹配條件是不一樣的。在純電阻電路中,當(dāng)負(fù)載電阻等于激勵(lì)源內(nèi)阻時(shí),則

2017-07-12 17:33:10

什么是輸出阻抗?什么是阻抗匹配?一、輸出阻抗在了解“阻抗匹配”這個(gè)問題之前,我們先來學(xué)習(xí)一下什么是“輸出阻抗”?在實(shí)際電路設(shè)計(jì)中,無論信號(hào)源、放大器或電源,都有輸出阻抗的問題。輸出阻抗其實(shí)就是一個(gè)

2019-12-06 09:10:59

、阻抗匹配的研究 在高速的PCB設(shè)計(jì)中,阻抗的匹配與否關(guān)系到信號(hào)的質(zhì)量優(yōu)劣。阻抗匹配的技術(shù)可以說是豐富多樣,但是在具體的系統(tǒng)中怎樣才能比較合理的應(yīng)用,需要衡量多個(gè)方面的因素。例如我們?cè)谙到y(tǒng)中PCB設(shè)計(jì)中

2019-05-31 06:45:06

。但是實(shí)際電路中很難做到這一點(diǎn),一般發(fā)送端的輸出阻抗會(huì)比較小,而接收端的輸入阻抗又很高,那么要處理好這對(duì)矛盾,端接就成為一種很自然的手段。因此,端接的本質(zhì)依然是阻抗匹配,這個(gè)是進(jìn)行PCB設(shè)計(jì)的重中之重

2020-02-26 08:00:00

在高速PCB設(shè)計(jì)時(shí)為了防止反射就要考慮阻抗匹配,但由于PCB的加工工藝限制了阻抗的連續(xù)性而仿真又仿不到,在原理圖的設(shè)計(jì)時(shí)怎樣來考慮這個(gè)問題?另外關(guān)于IBIS模型,不知在那里能提供比較準(zhǔn)確的IBIS

2012-03-03 12:41:55

傳輸線的特征阻抗跟負(fù)載阻抗不相等(即不匹配)時(shí),在負(fù)載端就會(huì)產(chǎn)生反射,造成自激振蕩。PCB板內(nèi)走線的低頻信號(hào)直接連通即可,一般不需要加串行匹配電阻。(2)并行阻抗匹配又叫“終端阻抗匹配”,一般用在輸入

2019-05-31 08:06:08

作用。(5)在高頻信號(hào)網(wǎng)絡(luò)中,充當(dāng)電感或電容(起阻抗匹配作用,0歐電阻也有阻抗!)。充當(dāng)電感用時(shí),主要是解決EMC問題。(6)單點(diǎn)接地,例如模擬地與數(shù)字地的單點(diǎn)對(duì)接共地。(7)配置電路,可以取代跳線和撥

2011-10-18 14:18:47

和電感結(jié)構(gòu)。串聯(lián)電阻的典型值為0.25——0.55ohms/foot,因?yàn)榻^緣層的緣故,并聯(lián)電阻阻值通常很高。將寄生電阻、電容和電感加到實(shí)際的PCB 連線中之后,連線上的最終阻抗稱為特征阻抗Z0 。線徑

2013-02-05 11:25:35

設(shè)計(jì)了一對(duì)收發(fā)線圈,發(fā)射線圈電阻2.3歐,電感1.4uH,射頻信號(hào)13.56MHz,匹配阻抗50歐。那阻抗匹配和線圈調(diào)諧先做哪步?該怎么做?它倆有關(guān)系么?怎么匹配和調(diào)諧?

2016-08-22 21:30:16

阻抗匹配是指負(fù)載阻抗與激勵(lì)源內(nèi)部阻抗互相適配,得到最大功率輸出的一種工作狀態(tài)。對(duì)于不同特性的電路,匹配條件是不一樣的。在純電阻電路中,當(dāng)負(fù)載電阻等于激勵(lì)源內(nèi)阻時(shí),則輸出功率為最大,這種工作狀態(tài)稱為

2019-06-03 08:07:23

阻抗匹配阻抗匹配是指在能量傳輸時(shí),要求負(fù)載阻抗要和傳輸線的特征阻抗相等,此時(shí)的傳輸不會(huì)產(chǎn)生反射,這表明所有能量都被負(fù)載吸收了。反之則在傳輸中有能量損失。在高速PCB設(shè)計(jì)中,阻抗的匹配與否關(guān)系到信號(hào)

2014-12-01 10:38:55

最近在設(shè)計(jì)pcb的時(shí)候,用到了MCX-KWE(50歐姆)天線接口,但有人說要阻抗匹配。大家有誰知道為什么要阻抗匹配嗎?如果不阻抗匹配會(huì)有什么結(jié)果?如果需要阻抗匹配該如何匹配?

2019-06-10 04:36:33

我是新手。 第一次畫網(wǎng)口電路的pcb,不知道差分信號(hào)布線時(shí)阻抗匹配怎么搞,請(qǐng)各位高手指點(diǎn)。謝謝

2019-04-22 06:28:45

“電阻”在電路中有限制電流的作用,不管是在交流電路還是直流電路中,電阻的作用都是相同的。“阻抗”則是電阻與電抗共同作用的結(jié)果,可見,阻抗只有在交流電路中才可能出現(xiàn)。所以談阻抗一定只是對(duì)交流電路而言

2017-09-05 21:56:53

“電阻”在電路中有限制電流的作用,不管是在交流電路還是直流電路中,電阻的作用都是相同的。“阻抗”則是電阻與電抗共同作用的結(jié)果,可見,阻抗只有在交流電路中才可能出現(xiàn)。所以談阻抗一定只是對(duì)交流電路而言

2017-09-06 15:00:11

什么是阻抗匹配?0歐電阻的作用是什么?

2021-04-21 06:29:42

得到最大功率,負(fù)載阻抗與內(nèi)阻必須滿 足共扼關(guān)系,即電阻成份相等,電抗成份只數(shù)值相等而符號(hào)相反。這種匹配條件稱為共扼匹配。. 在高速的設(shè)計(jì)中,阻抗的匹配與否關(guān)系到信號(hào)的質(zhì)量優(yōu)劣。阻抗匹配的技術(shù)可以說是

2011-08-04 08:56:54

一、輸出阻抗在了解“阻抗匹配”這個(gè)問題之前,我們先來學(xué)習(xí)一下什么是“輸出阻抗”?在實(shí)際電路設(shè)計(jì)中,無論信號(hào)源、放大器或電源,都有輸出阻抗的問題。輸出阻抗其實(shí)就是一個(gè)信號(hào)源的內(nèi)阻。本來,對(duì)于一個(gè)理想

2019-06-04 04:20:37

阻抗匹配阻抗匹配是指在能量傳輸時(shí),要求負(fù)載阻抗要和傳輸線的特征阻抗相等,此時(shí)的傳輸不會(huì)產(chǎn)生反射,這表明所有能量都被負(fù)載吸收了。反之則在傳輸中有能量損失。在高速PCB設(shè)計(jì)中,阻抗的匹配與否關(guān)系到信號(hào)的質(zhì)量優(yōu)劣。

2019-05-31 08:12:33

在高速pcb設(shè)計(jì)中,經(jīng)常聽到要求阻抗匹配。而設(shè)計(jì)中導(dǎo)致阻抗不匹配的原因有哪些呢?一般又對(duì)應(yīng)著怎么的解決方案?歡迎大家來討論

2014-10-24 13:50:36

在高速的設(shè)計(jì)中,阻抗的匹配與否關(guān)系到信號(hào)的質(zhì)量優(yōu)劣。阻抗匹配的技術(shù)可以說是豐富多樣,但是在具體的系統(tǒng)中怎樣才能比較合理的應(yīng)用,需要衡量多個(gè)方面的因素。例如我們?cè)谙到y(tǒng)中設(shè)計(jì)中,很多采用的都是源段的串連

2019-05-29 07:03:30

PCB設(shè)計(jì)時(shí),注意控制走線時(shí)的阻抗控制,往往可以做到很好的匹配。 對(duì)于通常的聚酯膠片PCB 來說,傳輸線的長度和微帶線 Stub 效應(yīng)是需要考慮的, 在本設(shè)計(jì)指南里面,主要是針對(duì) 4 層的 1080+2116 聚酯膠片PCB 進(jìn)行相關(guān)的阻抗匹配控制。

2019-05-17 10:40:14

挑戰(zhàn)。

在高速PCB設(shè)計(jì)中,阻抗匹配顯得尤為重要,為減少在高速信號(hào)傳輸過程中的反射現(xiàn)象,必須在信號(hào)源、接收端以及傳輸線上保持阻抗的匹配。

一般而言,單端信號(hào)線的阻抗取決于它的線寬以及與參考平面之間

2023-05-26 11:30:36

電路阻抗匹配設(shè)計(jì)

2010-08-12 18:37:28 0

0

阻抗匹配的基本原理

右圖中R為負(fù)載電阻,r為電源E的內(nèi)阻,E為電壓源。由于r

2006-04-16 18:28:39 1315

1315

什么是阻抗匹配?

阻抗匹配(Imped

2006-09-25 14:21:53 4313

4313 阻抗匹配的詳細(xì)介紹

阻抗匹配(Impedance matching)是微波電子學(xué)里的一部分,主要用于傳輸線上,來達(dá)至所有高頻的微波信號(hào)皆能傳至

2009-10-20 15:26:35 1606

1606 關(guān)于高速設(shè)計(jì)中的阻抗匹配的問題

一.阻抗匹配的研究 在高速的設(shè)計(jì)中,阻抗的匹配與否關(guān)系到信號(hào)的質(zhì)量優(yōu)劣。阻抗匹配的技術(shù)可以說是豐

2010-03-15 10:35:47 1161

1161 附件是一款PCB阻抗匹配計(jì)算工具,點(diǎn)擊CITS25.exe直接打開使用,無需安裝。附件還帶有PCB連板的一些計(jì)算方法,連板的排法和PCB聯(lián)板的設(shè)計(jì)驗(yàn)驗(yàn)。 PCB設(shè)計(jì)的經(jīng)驗(yàn)建議: 1.一般連板長寬比率

2012-11-02 17:11:10 1081

1081 什么是阻抗匹配以及為什么要阻抗匹配,個(gè)人收集整理了很久的資料,大家根據(jù)自己情況,有選擇性的下載吧~

2015-10-28 10:01:08 59

59 PCB阻抗匹配總結(jié),感興趣的小伙伴們可以看看。

2016-07-25 18:56:47 0

0 PCB阻抗匹配計(jì)算工具與教程,感興趣的小伙伴們可以瞧一瞧。

2016-10-14 14:17:18 0

0 PCB阻抗匹配計(jì)算工具與教程

2017-01-04 14:57:53 0

0 阻抗匹配是指在能量傳輸時(shí),要求負(fù)載阻抗要和傳輸線的特征阻抗相等,此時(shí)的傳輸不會(huì)產(chǎn)生反射,這表明所有能量都被負(fù)載吸收了。反之則在傳輸中有能量損失。在高速 PCB 設(shè)計(jì)中,阻抗的匹配與否關(guān)系到信號(hào)的質(zhì)量優(yōu)劣。PCB 走線什么時(shí)候需要做阻抗匹配?

2017-08-28 16:33:23 26

26 。串行電阻的阻值為20~75,阻值大小與信號(hào)頻率成正比,與PCB走線寬度成反比。在嵌入式系統(tǒng)中,一般頻率大于20M的信號(hào)且PCB走線長度大于5cm時(shí)都要加串行匹配電阻,例如系統(tǒng)中的時(shí)鐘信號(hào)、數(shù)據(jù)和地址總線信號(hào)等。串行匹配電阻的作用有兩

2017-11-03 10:28:39 19

19 。串行電阻的阻值為20~75,阻值大小與信號(hào)頻率成正比,與PCB走線寬度成反比。在嵌入式系統(tǒng)中,一般頻率大于20M的信號(hào)且PCB走線長度大于5cm時(shí)都要加串行匹配電阻,例如系統(tǒng)中的時(shí)鐘信號(hào)、數(shù)據(jù)和地址總線信號(hào)等。串行匹配電阻的作用有兩個(gè)

2017-12-04 11:12:53 0

0 阻抗匹配是指負(fù)載阻抗與激勵(lì)源內(nèi)部阻抗互相適配,得到最大功率輸出的一種工作狀態(tài)。對(duì)于不同特性的電路,匹配條件是不一樣的。在純電阻電路中,當(dāng)負(fù)載電阻等于激勵(lì)源內(nèi)阻時(shí),則輸出功率為最大,這種工作狀態(tài)稱為

2017-12-07 05:40:01 1733

1733 本文主要介紹的是阻抗匹配,首先介紹了阻抗匹配條件,其次闡述了如何理解阻抗匹配及常見阻抗匹配的方式,最后介紹了pcb阻抗匹配如何計(jì)算,具體的跟隨小編一起來了解一下。

2018-05-02 17:11:28 38669

38669

本文主要詳解什么是阻抗匹配,首先介紹了輸入及輸出阻抗是什么,其次介紹了阻抗匹配的原理,最后闡述了阻抗匹配的應(yīng)用領(lǐng)域,具體的跟隨小編一起來了解一下吧。

2018-05-03 11:42:28 47487

47487

阻抗匹配是指在能量傳輸時(shí),要求負(fù)載阻抗要和傳輸線的特征阻抗相等,此時(shí)的傳輸不會(huì)產(chǎn)生反射,這表明所有能量都被負(fù)載吸收了。反之則在傳輸中有能量損失。在高速PCB打樣設(shè)計(jì)中,阻抗的匹配與否關(guān)系到信號(hào)的質(zhì)量優(yōu)劣。

2018-07-12 08:00:00 0

0 在高速PCB設(shè)計(jì)時(shí)為了防止反射就要考慮阻抗匹配,但由于PCB的加工工藝限制了阻抗的連續(xù)性而仿真又仿不到,在原理圖的設(shè)計(jì)時(shí)怎樣來考慮這個(gè)問題?

2019-06-21 17:03:47 6432

6432 ? ? ? 阻抗匹配 阻抗匹配是指在能量傳輸時(shí),要求負(fù)載阻抗要和傳輸線的特征阻抗相等,此時(shí)的傳輸不會(huì)產(chǎn)生反射,這表明所有能量都被負(fù)載吸收了。反之則在傳輸中有能量損失。在高速PCB設(shè)計(jì)中,阻抗的匹配

2019-12-13 13:47:22 2619

2619 串行電阻的阻值為20~75,阻值大小與信號(hào)頻率成正比,與PCB走線寬度成反比。在嵌入式系統(tǒng)中,一般頻率大于20M的信號(hào)且PCB走線長度大于5cm時(shí)都要加串行匹配電阻,例如系統(tǒng)中的時(shí)鐘信號(hào)、數(shù)據(jù)和地址總線信號(hào)等。串行匹配電阻的作用有兩個(gè):

2020-09-17 11:04:15 4126

4126 在高速PCB設(shè)計(jì)時(shí)為了防止反射就要考慮阻抗匹配,但由于PCB的加工工藝限制了阻抗的連續(xù)性而仿真又仿不到,在原理圖的設(shè)計(jì)時(shí)怎樣來考慮這個(gè)問題?

2020-11-12 17:09:06 4684

4684 最近設(shè)計(jì)了一塊四層板pcb,因?yàn)槭歉咚匐娐罚?b class="flag-6" style="color: red">阻抗匹配的要求,所以在發(fā)給pcb板廠打樣時(shí),特定指定了哪些線要做

2020-12-07 12:08:23 18299

18299 射頻工程師大都遇到過匹配阻抗的問題,通俗的講,阻抗匹配的目的是確保能實(shí)現(xiàn)信號(hào)或能量從“信號(hào)源”到“負(fù)載”的有效傳送。

2021-03-18 08:18:55 84

84 在本文中,我們將更多地了解PCB 阻抗匹配,以及它為何如此重要。

2022-07-06 16:49:17 4387

4387

本文主要詳解什么是阻抗匹配,首先介紹了輸入及輸出阻抗是什么,其次介紹了阻抗匹配的原理,最后闡述了阻抗匹配的應(yīng)用領(lǐng)域,具體的跟隨小編一起來了解一下吧。

2022-08-22 14:10:05 2753

2753 JFW的在線阻抗匹配焊盤型號(hào)如下表所示。阻抗匹配焊盤使用內(nèi)部電阻器來設(shè)計(jì),內(nèi)部電阻器被配置為將每一側(cè)的阻抗匹配到不同的阻抗。

2022-10-28 16:48:55 815

815 阻抗匹配是指信號(hào)源或者傳輸線跟負(fù)載之間的一種合適的搭配方式。根據(jù)接入方式阻抗匹配有串行和并行兩種方式;根據(jù)信號(hào)源頻率阻抗匹配可分為低頻和高頻兩種。

2023-08-30 09:47:00 480

480 高頻信號(hào)一般使用串行阻抗匹配。串行電阻的阻值為20~75Ω,阻值大小與信號(hào)頻率成正比,與PCB走線寬度和長度成反比。在嵌入式系統(tǒng)中,一般頻率大于20M的信號(hào)PCB走線長度大于5cm時(shí)都要加串行匹配電阻

2023-09-12 17:32:33 854

854

放大器的增益和帶寬。因此,為了避免這些問題,需要進(jìn)行阻抗匹配。 實(shí)現(xiàn)阻抗匹配的方法有很多種,最常見的是使用匹配網(wǎng)絡(luò)或特定的連接方式。匹配網(wǎng)絡(luò)的作用是將輸入和輸出阻抗調(diào)整到合適的匹配值,以提高效率和帶寬。常用的匹

2023-10-11 17:43:07 869

869 為什么高頻小信號(hào)諧振放大器中要考慮阻抗匹配?如何實(shí)現(xiàn)阻抗匹配?常用有哪些連接方式? 一、高頻小信號(hào)諧振放大器的介紹 高頻小信號(hào)諧振放大器,是一種廣泛應(yīng)用于無線通信、雷達(dá)、衛(wèi)星通信、微波通信等領(lǐng)域

2023-10-20 14:55:44 679

679 什么是阻抗匹配?高速PCB設(shè)計(jì)為什么要控制阻抗匹配? 阻抗匹配是指在電路傳輸信號(hào)時(shí),控制電路中信號(hào)源、傳輸線和負(fù)載之間的阻抗相等的過程,從而確保信號(hào)的完整性和可靠性。在高速PCB設(shè)計(jì)中,阻抗匹配

2023-10-30 10:03:25 924

924 在完成PCB設(shè)計(jì)后一般要怎樣跟板廠對(duì)接使其了解哪些線需要做阻抗匹配呢? 在完成PCB設(shè)計(jì)后,為了使其與板廠對(duì)接,必須先了解哪些線需要進(jìn)行阻抗匹配。阻抗匹配是在 PCB 設(shè)計(jì)過程中非常重要的一部分

2023-10-30 10:03:34 610

610 和輸出端口的阻抗相匹配,從而最大程度地傳輸信號(hào),并最小化信號(hào)的反射和損耗。 在了解阻抗匹配的概念和原理之前,我們首先需要了解一些基本的電路理論。阻抗(Impedance)是指電路中的電阻、電感和電容的整體特性,它包含了電路元件對(duì)電流和電壓的阻

2023-12-18 13:39:56 482

482 一部分能量被反射回去,無法完全傳輸給目標(biāo)電路。 阻抗匹配的目標(biāo)是使得兩個(gè)電路的阻抗完全相等,從而實(shí)現(xiàn)最大功率傳輸。阻抗是指電路對(duì)電流和電壓的相互關(guān)系的阻抗特性。一般來說,阻抗可以分為電阻、電感和電容三種形式。

2023-12-21 11:31:33 394

394 什么是阻抗 在電學(xué)中,常把對(duì)電路中電流所起的阻礙作用叫做阻抗。阻抗單位為歐姆,常用Z表示,是一個(gè)復(fù)數(shù)Z= R+i(?ωL–1/(ωC)) 具體說來阻抗可分為兩個(gè)部分,電阻(實(shí)部)和電抗

2024-01-02 16:59:13 395

395

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論