作者:賽迪智庫(kù)集成電路研究所

EDA工具市場(chǎng)競(jìng)爭(zhēng)特征

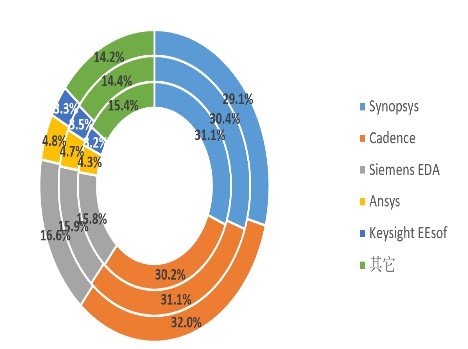

經(jīng)過(guò)30余年的行業(yè)整合發(fā)展,全球EDA工具市場(chǎng)體現(xiàn)出較明顯的寡頭壟斷特征,新思科技(Synopsys)、楷登電子(Cadence)與西門(mén)子EDA(原Mentor Graphics)作為目前僅有的擁有設(shè)計(jì)全流程EDA工具解決方案的企業(yè),集中了全球超77%的EDA工具市場(chǎng)。此外,Ansys憑借熱分析、壓電分析等優(yōu)勢(shì)點(diǎn)工具,Keysight EEsof憑借電磁仿真、射頻綜合等優(yōu)勢(shì)點(diǎn)工具,獲得市場(chǎng)第四、第五的位置。近三年來(lái),在優(yōu)勢(shì)工具的鞏固下,在2020年全球72.3億美元的市場(chǎng)中,前五大EDA工具企業(yè)控制了約85%市場(chǎng),其中市場(chǎng)前三大企業(yè)的市場(chǎng)占有率近80%。除市場(chǎng)前三的EDA工具企業(yè)外,其他企業(yè)缺少布局設(shè)計(jì)全流程工具技術(shù)的綜合實(shí)力,各企業(yè)均在各自擅長(zhǎng)領(lǐng)域開(kāi)發(fā)面向特定流程或個(gè)別環(huán)節(jié)的工具產(chǎn)品,瓜分剩余市場(chǎng)份額。

圖1 2018-2020年全球EDA工具市場(chǎng)競(jìng)爭(zhēng)格局

注:內(nèi)圈至外圈分別為2018-2020年數(shù)據(jù)

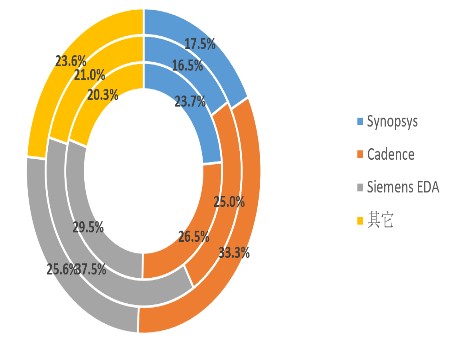

與國(guó)際市場(chǎng)相似,我國(guó)EDA工具市場(chǎng)同樣呈現(xiàn)出市場(chǎng)份額集中的特點(diǎn),近三年市場(chǎng)前五大企業(yè)的市場(chǎng)占有率在86%左右。其中,Synopsys、Cadence、Siemens EDA為我國(guó)市場(chǎng)前三大EDA工具供應(yīng)商。2020年,在我國(guó)66.2億元人民幣的EDA工具市場(chǎng)中,前五大供應(yīng)商占有85.4%的市場(chǎng)份額。按年度分析,由于單一市場(chǎng)大客戶周期性訂單影響,市場(chǎng)前三大供應(yīng)商的市場(chǎng)份額波動(dòng)較大,整體看均具有明顯市場(chǎng)優(yōu)勢(shì)。我國(guó)本土的華大九天公司通過(guò)十余年市場(chǎng)耕耘,近年來(lái)持續(xù)實(shí)現(xiàn)市場(chǎng)突破。據(jù)統(tǒng)計(jì),2020年華大九天公司在我國(guó)市場(chǎng)的銷(xiāo)售額超過(guò)Ansys公司,成為我國(guó)市場(chǎng)第四大EDA工具企業(yè)。

圖2 2018-2020年我國(guó)EDA工具市場(chǎng)競(jìng)爭(zhēng)格局

注:內(nèi)圈至外圈分別為2018-2020年數(shù)據(jù)

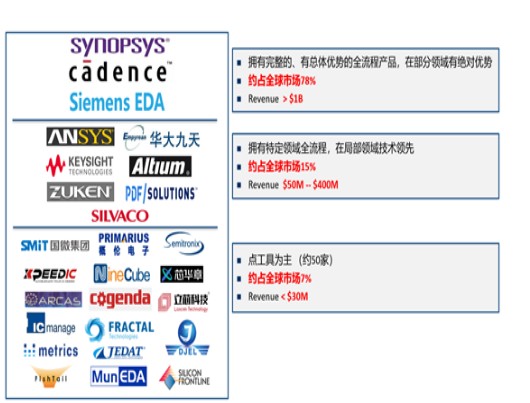

從技術(shù)格局來(lái)看,全球EDA行業(yè)企業(yè)可分為三個(gè)梯隊(duì)。其中,第一梯隊(duì)企業(yè)擁有完整的且總體優(yōu)勢(shì)明顯的全流程EDA工具,部分流程工具在細(xì)分領(lǐng)域擁有絕對(duì)優(yōu)勢(shì),EDA領(lǐng)域年?duì)I業(yè)收入超10億美元,代表企業(yè)有新思科技、楷登電子和西門(mén)子EDA(原Mentor Graphics)。第二梯隊(duì)企業(yè)擁有部分領(lǐng)域的全流程工具產(chǎn)品,且在局部領(lǐng)域具有絕對(duì)優(yōu)勢(shì),年?duì)I業(yè)收入在5000萬(wàn)美元至4億美元之間,面向處在第三梯隊(duì)的EDA企業(yè),相關(guān)公司產(chǎn)品以點(diǎn)工具為主,企業(yè)年?duì)I業(yè)收入普遍小于3000萬(wàn)美元。

圖3 EDA行業(yè)技術(shù)格局

對(duì)于我國(guó)EDA行業(yè)企業(yè),在市場(chǎng)驅(qū)動(dòng)與資本加持的助推下,代表性企業(yè)呈加速發(fā)展勢(shì)頭,未來(lái)數(shù)年有望出現(xiàn)多家企業(yè)進(jìn)入行業(yè)第二梯隊(duì)。華大九天公司作為我國(guó)唯一在部分領(lǐng)域擁有全流程工具的EDA工具企業(yè),在營(yíng)收規(guī)模上在本土企業(yè)中具有較明顯優(yōu)勢(shì),目前公司已在模擬/數(shù)模混合設(shè)計(jì)、數(shù)字設(shè)計(jì)、平板顯示設(shè)計(jì)以及晶圓制造部分相關(guān)領(lǐng)域進(jìn)行布局,整體技術(shù)水平在國(guó)內(nèi)具有領(lǐng)先性,并進(jìn)一步實(shí)現(xiàn)了各大類(lèi)工具的部分代表性點(diǎn)工具產(chǎn)品在關(guān)鍵參數(shù)上優(yōu)于市場(chǎng)國(guó)際主流產(chǎn)品。

EDA工具行業(yè)商業(yè)模式特征

集成電路設(shè)計(jì)工具(EDA工具)從計(jì)算機(jī)輔助設(shè)計(jì)軟件發(fā)展而來(lái),在行業(yè)商業(yè)、銷(xiāo)售模式上具有與工業(yè)軟件相似的方式。經(jīng)過(guò)三十余年獨(dú)立發(fā)展,EDA工具結(jié)合集成電路領(lǐng)域特殊的市場(chǎng)形態(tài)和運(yùn)作方式,形成了具有自身特色的行業(yè)商業(yè)和銷(xiāo)售模式。綜合看,國(guó)際主流廠商推廣EDA工具商業(yè)應(yīng)用的方式包括“定期授權(quán)+技術(shù)服務(wù)”,以及面向高校、科研院所推廣教育應(yīng)用。

面向“定期授權(quán)+技術(shù)服務(wù)”的商業(yè)模式,原美國(guó)Arcsys公司在商業(yè)競(jìng)爭(zhēng)中為降低客戶的EDA工具使用成本、增強(qiáng)公司與客戶間的耦合度,實(shí)現(xiàn)公司產(chǎn)業(yè)市場(chǎng)競(jìng)爭(zhēng)力提升,在20世紀(jì)90年代一改傳統(tǒng)的EDA工具永久許可銷(xiāo)售模式,將EDA工具的一次性售賣(mài)改為有限期租賃,并在產(chǎn)品服務(wù)期為客戶提供開(kāi)發(fā)技術(shù)支持等的服務(wù)。通過(guò)商業(yè)模式變革,原Arcsys在一年多時(shí)間年實(shí)現(xiàn)銷(xiāo)售額超600%增長(zhǎng),進(jìn)一步深刻影響其他EDA工具企業(yè)的經(jīng)營(yíng)向“定期授權(quán)+技術(shù)服務(wù)”的方式上轉(zhuǎn)變。目前,EDA工具企業(yè)對(duì)客戶每一期的EDA工具租賃時(shí)長(zhǎng)普遍在2-3年,由此導(dǎo)致大客戶新一期訂單對(duì)部分企業(yè)銷(xiāo)售收入造成周期性影響。

面向高校、科研院所的產(chǎn)業(yè)推廣與應(yīng)用是EDA企業(yè)培養(yǎng)市場(chǎng)生態(tài)、客戶習(xí)慣的重要方式和手段。一方面,為支持教學(xué)和科技研發(fā)創(chuàng)新,包括EDA工具在內(nèi)的軟硬件產(chǎn)品生產(chǎn)商均有面向高校、科研院所推出“教育版”產(chǎn)品,產(chǎn)品售價(jià)普遍低于商業(yè)化產(chǎn)品。另一方面,面向EDA工具的推廣與應(yīng)用,主流EDA企業(yè)均高度重視院校市場(chǎng),推出各自的“高校計(jì)劃”,面對(duì)院校方以成本價(jià)或贈(zèng)與的方式進(jìn)行產(chǎn)品銷(xiāo)售,并在院校師生使用產(chǎn)品進(jìn)行教學(xué)和科研中提供EDA產(chǎn)品技術(shù)支持與服務(wù)。

EDA工具技術(shù)發(fā)展趨勢(shì)特征

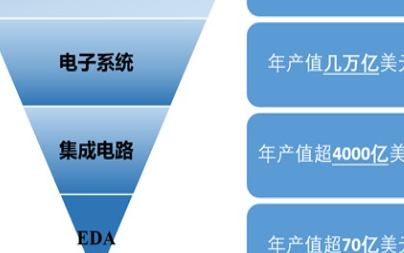

1、后摩爾時(shí)代技術(shù)演進(jìn)驅(qū)動(dòng)EDA技術(shù)應(yīng)用延伸拓展

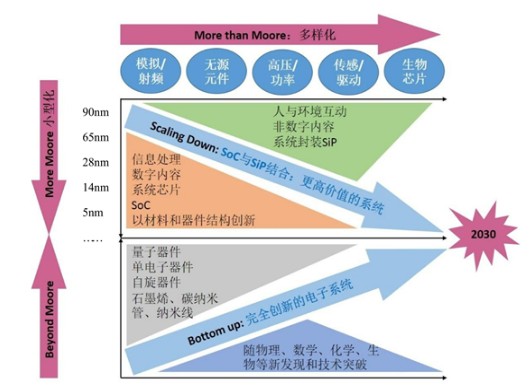

后摩爾時(shí)代的集成電路技術(shù)演進(jìn)方向主要包括延續(xù)摩爾定律(More Moore)、擴(kuò)展摩爾定律(More than Moore)以及超越摩爾定律(Beyond Moore)三類(lèi),主要發(fā)展目標(biāo)涵蓋了建立在摩爾定律基礎(chǔ)上的生產(chǎn)工藝特征尺寸的進(jìn)一步微縮、以增加系統(tǒng)集成的多重功能為目標(biāo)的芯片功能多樣化發(fā)展,以及通過(guò)三維封裝(3D Package)、系統(tǒng)級(jí)封裝(SiP)等方式實(shí)現(xiàn)器件功能的融合和產(chǎn)品的多樣化。伴隨芯片技術(shù)的持續(xù)發(fā)展,人工智能、高性能計(jì)算、新一代信息技術(shù)、物聯(lián)網(wǎng)等新應(yīng)用不斷涌現(xiàn),技術(shù)和應(yīng)用發(fā)展的疊加讓芯片技術(shù)和功能復(fù)雜度不斷提升,同時(shí)帶來(lái)對(duì)集成電路設(shè)計(jì)工具(EDA)的新發(fā)展需求。其中,面向延續(xù)摩爾定律(More Moore)方向,單芯片的集成規(guī)模呈現(xiàn)爆發(fā)性增增長(zhǎng),為EDA工具的設(shè)計(jì)效率提出更高要求。面向擴(kuò)展摩爾定律(More than Moore)方向,伴隨邏輯、模擬、存儲(chǔ)等功能被疊加到同一芯片,EDA工具需具備對(duì)更強(qiáng)復(fù)雜功能設(shè)計(jì)的支撐能力。面向超越摩爾定律(Beyond Moore)方向,新工藝、新材料、新器件等的應(yīng)用要求EDA工具的發(fā)展在仿真、驗(yàn)證等關(guān)鍵環(huán)節(jié)實(shí)現(xiàn)方法學(xué)的創(chuàng)新。

圖4 后摩爾時(shí)代集成電路技術(shù)演進(jìn)路徑

2、設(shè)計(jì)方法學(xué)創(chuàng)新輔助平抑芯片設(shè)計(jì)成本

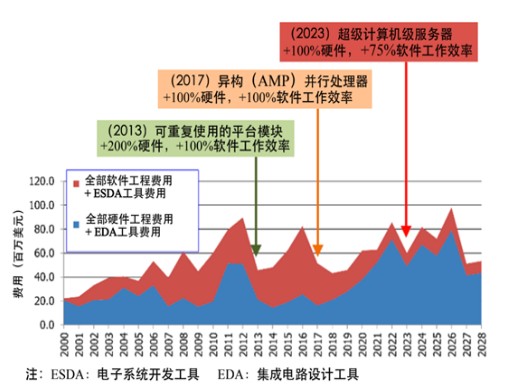

EDA工具的發(fā)展創(chuàng)新極大程度提高了芯片設(shè)計(jì)效率,一直以來(lái)是推動(dòng)芯片設(shè)計(jì)成本保持在合理范圍的重要方式。根據(jù)加州大學(xué)圣迭戈分校Andrew Kahng教授在2013年的推測(cè),2011年設(shè)計(jì)一款消費(fèi)級(jí)應(yīng)用處理器芯片的成本約4000萬(wàn)美元,如果不考慮1993年至2009年的EDA技術(shù)進(jìn)步,相關(guān)設(shè)計(jì)成本可能高達(dá)77億美元,EDA技術(shù)進(jìn)步讓設(shè)計(jì)效率提升近200倍。整體看,既往及今后一段時(shí)間,推動(dòng)設(shè)計(jì)效率提升的相關(guān)技術(shù)進(jìn)步包括可重復(fù)使用的平臺(tái)模塊、異構(gòu)(AMP)并行處理器的應(yīng)用等。

圖5 EDA技術(shù)進(jìn)步對(duì)芯片設(shè)計(jì)成本的影響

在后摩爾時(shí)代,由“摩爾定律”驅(qū)動(dòng)的芯片集成度和復(fù)雜度持續(xù)提升將為EDA工具發(fā)展帶來(lái)新需求。在設(shè)計(jì)方法學(xué)層面,EDA工具的發(fā)展方向主要包括系統(tǒng)級(jí)或行為級(jí)的軟硬件協(xié)同設(shè)計(jì)方法、跨層級(jí)芯片協(xié)同驗(yàn)證方法、面向設(shè)計(jì)與制造相融合的設(shè)計(jì)方法和芯片敏捷設(shè)計(jì)方法四方面。其中,系統(tǒng)級(jí)或行為級(jí)的軟硬件協(xié)同設(shè)計(jì)方法可以讓設(shè)計(jì)師在完成芯片行為設(shè)計(jì)的基礎(chǔ)上自動(dòng)完成后續(xù)的芯片硬件的具體實(shí)現(xiàn),同時(shí)支持同步開(kāi)展應(yīng)用軟件的開(kāi)發(fā),以達(dá)到設(shè)計(jì)效率提升的目的。跨層級(jí)芯片協(xié)同驗(yàn)證方法則強(qiáng)調(diào)驗(yàn)證工作實(shí)現(xiàn)芯片設(shè)計(jì)與封裝、印制電路板(PCB)甚至整個(gè)應(yīng)用系統(tǒng)相組合的跨層級(jí)協(xié)同驗(yàn)證,以確保設(shè)計(jì)的正確性。面向設(shè)計(jì)與制造相融合的設(shè)計(jì)方法則追求在芯片設(shè)計(jì)的各個(gè)階段實(shí)現(xiàn)與制造工藝的融合,以期提升芯片最終生產(chǎn)良率。芯片敏捷設(shè)計(jì)方法則通過(guò)算法和軟件需求定義芯片架構(gòu),結(jié)合模板元編程(Meta-Programming)和高層次綜合(HLS)的設(shè)計(jì)方法,實(shí)現(xiàn)快速設(shè)計(jì)和快速迭代。

3、人工智能技術(shù)將在EDA領(lǐng)域扮演更重要角色

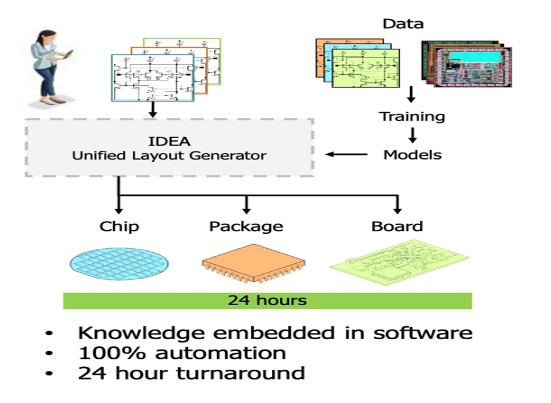

人工智能(AI)技術(shù)應(yīng)用于EDA領(lǐng)域始于20世紀(jì)80年代,一直以來(lái)受制于運(yùn)算能力不強(qiáng)、AI性能不理想、芯片設(shè)計(jì)的數(shù)據(jù)需求量不夠大等因素,導(dǎo)致AI技術(shù)與EDA的融合并不充分。近年來(lái),伴隨芯片設(shè)計(jì)基礎(chǔ)數(shù)據(jù)量的不斷增加、系統(tǒng)運(yùn)算能力的階躍式上升,人工智能技術(shù)應(yīng)用在EDA工具領(lǐng)域的算法和算力需求正在被更好地滿足。此外,芯片復(fù)雜度的提升以及設(shè)計(jì)效率要求的提高同樣要求人工智能技術(shù)賦能EDA工具的升級(jí),輔助降低芯片設(shè)計(jì)門(mén)檻、提升芯片設(shè)計(jì)效率。2017年美國(guó)國(guó)防部高級(jí)研究計(jì)劃局(DARPA)推出的“電子復(fù)興計(jì)劃(ERI)”中的電子設(shè)備智能設(shè)計(jì)(IDEA)項(xiàng)目,描繪出新的AI技術(shù)賦能EDA工具發(fā)展目標(biāo)與方向。其中提出目標(biāo)實(shí)現(xiàn)“設(shè)計(jì)工具在版圖設(shè)計(jì)中無(wú)人干預(yù)的能力”,即通過(guò)人工智能和機(jī)器學(xué)習(xí)的方法將設(shè)計(jì)經(jīng)驗(yàn)固化,進(jìn)而形成統(tǒng)一的版圖生成器,以期實(shí)現(xiàn)通過(guò)版圖生成器在24小時(shí)之內(nèi)完成SoC(系統(tǒng)級(jí)芯片)、SiP(系統(tǒng)級(jí)封裝)和印刷電路板(PCB)的版圖設(shè)計(jì)。

圖6 IDEA項(xiàng)目設(shè)計(jì)框架

4、云技術(shù)在EDA領(lǐng)域的應(yīng)用日趨深入

一直以來(lái),企業(yè)對(duì)核心知識(shí)產(chǎn)權(quán)、工藝設(shè)計(jì)套件(PDKs)等高度敏感數(shù)據(jù)的安全顧慮是限制云技術(shù)在EDA領(lǐng)域應(yīng)用推廣的重要阻礙。近年來(lái),伴隨相關(guān)技術(shù)方式的逐步成熟、用戶使用習(xí)慣的改變,疊加應(yīng)用云技術(shù)進(jìn)行芯片設(shè)計(jì)研發(fā)方面的綜合成本、效率優(yōu)勢(shì),云技術(shù)正在EDA領(lǐng)域獲得快速發(fā)展。伴隨EDA云平臺(tái)的逐步發(fā)展,云技術(shù)在EDA領(lǐng)域的應(yīng)用第一可以有效避免芯片設(shè)計(jì)企業(yè)因流程管理、計(jì)算資源不足帶來(lái)的研發(fā)風(fēng)險(xiǎn),保障企業(yè)研發(fā)生產(chǎn)效率;第二可以有效降低企業(yè)在服務(wù)器配置和維護(hù)方面的費(fèi)用,讓企業(yè)根據(jù)實(shí)際需求更加靈活地使用計(jì)算資源;第三可以讓芯片設(shè)計(jì)工作擺脫物理環(huán)境制約,尤其在新冠疫情帶來(lái)的居家辦公需求下讓EDA云平臺(tái)發(fā)揮了重要作用;第四有助于EDA技術(shù)在教育領(lǐng)域的推廣和應(yīng)用,支持設(shè)計(jì)人才培養(yǎng)等相關(guān)工作。此外,類(lèi)似RISC-V的開(kāi)源化模式也更適合采用云平臺(tái)進(jìn)行相關(guān)如基于RISC-V內(nèi)核芯片的芯片設(shè)計(jì)工作。

責(zé)任編輯:tzh

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論