采用FPGA進行的數字電路設計具有更大的靈活性和通用性,已成為目前數字電路設計的主流方法之一。本文給出一種基于FPGA的數字鐘設計方案。該方案采用VHDL設計底層模塊,采用電路原理圖設計頂層系統。整個系統在QuartusⅡ開發平臺上完成設計、編譯和仿真,并在FPGA硬件實驗箱上進行測試。測試結果表明該設計方案切實可行。

EDA(Electronic Design AutomaTI on)又名電子設計自動化,其基本特征是:以超大規模可編程邏輯器件,如FPGA,為設計載體,以硬件描述語言,如VHDL,為系統邏輯描述的主要表達方式,以計算機、大規模可編程邏輯器件的開發軟件及實驗開發系統為設計工具,完成電子系統的設計。

使用EDA進行電子系統設計具有以下特點:

1) 用軟件方式設計硬件;

2) 用軟件方式設計的系統到硬件系統的轉換是由有關開發軟件自動完成的;

3) 設計過程中可用有關軟件進行各種仿真;

4) 系統可現場編程,在線升級;

5) 整個系統可集成在一個芯片上,體積小、功耗低、可靠性高;

6) 設計的移植性好、效率高;

7)適合分工設計、團隊協作。因此,EDA技術是現代電子設計的發展趨勢。

1、數字鐘的設計方案

本文以FPGA平臺為基礎,采用VHDL語言在QuartusⅡ開發環境下設計開發多功能數字鐘,具有計時、校時、蜂鳴鬧鈴的功能,具體功能為:

1) 能夠對秒、分、小時進行正常計時,每日按24小時計時制,能用八個七段數碼管進行友好界面的顯示;

2) 具有復位功能,可以對當前時間進行清零;

3) 能夠對電子時鐘進行時分秒設置,方便在時鐘跑錯時進行校正;

4) 能夠設定電子鬧鐘,在指定的時間驅動蜂鳴器等外設工作,引起使用者注意;

5) 電子鐘具有溢出警報功能,當小時數超過24時,用一個LED小燈進行溢出警報說明,然后從00—00—00開始從新計時,此功能可以使電子鐘很方便的擴展為萬年歷。

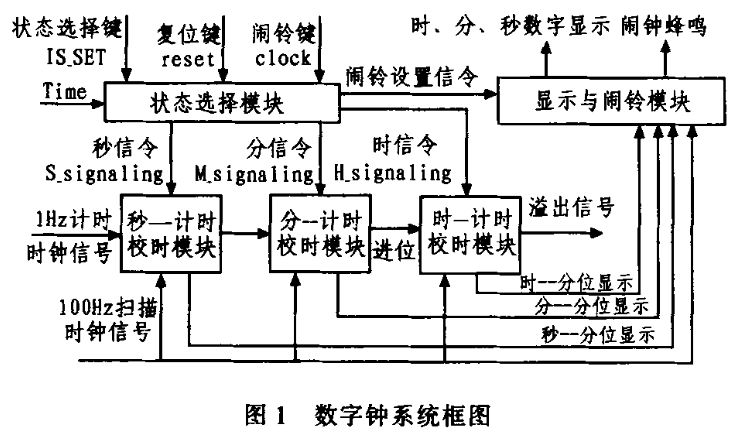

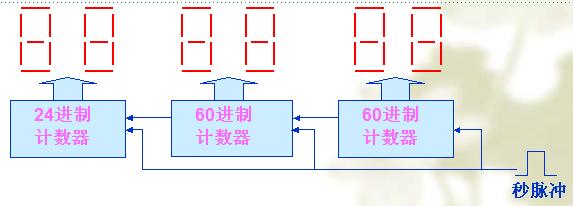

我們采用自頂向下的層次化設計方法進行設計,其輸入為狀態選擇信號(使用一個2位二進制表示選擇,00正常運行或顯示鬧鈴信息,01設置秒,10設置分,11設置時)、復位信號、鬧鈴開關(配合狀態選擇信號進行鬧鈴的設置)、1 Hz的計時時鐘信號和1 kHz的掃描時鐘信號;輸出為時、分、秒數字顯示(這里使用了8個共陰極的七段數碼管作為顯示輸出)、鬧鐘蜂鳴、溢出信號。系統由狀態選擇模塊、時、分、秒計時校時模塊、顯示與鬧鈴模塊組成。數字鐘的系統框圖圖如圖1所示。

2、核心模塊設計

2.1 狀態選擇模塊設計

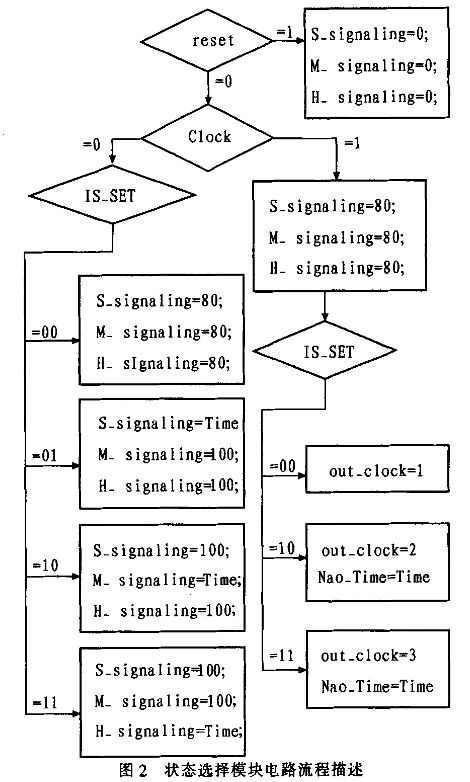

該模塊主要功能其實是對輸入端的匯總,然后根據設置方法對不同的模塊進行使能和參數傳遞,輸出不同的信令signaling控制到各個模塊,使每個模塊工作在一個有序的狀態。狀態選擇模塊的電路描述如圖2所示,具體說明如下:當輸入一個脈沖到復位鍵reset時,數字鐘啟動并對時間清零。

鬧鈴鍵clock=0時,模塊根據狀態選擇鍵IS_SET輸出不同秒、分、時信令到秒、分、時計時校時模塊,控制這些模塊的運行狀態。此時,當IS_SET=00時為正常計時狀態,秒、分、時的輸出信令均為80;IS_SET=01時為秒校時狀態,輸出秒信令S_signaling為時間輸入TI me(顯然該輸出小于60),而輸出分信令M_signaling和時信令H_signaling均為100,表示暫停分、時計時;

IS_SET=10和11時則分別為分和時的校時狀態。鬧鈴鍵clock=1時,當IS_SET=10和11時分別設置鬧鈴的分、時為時間輸入TI me并將設置的鬧鈴時間輸出到“顯示與鬧鈴模塊”中保存;當IS_SET=00時,輸出out_clock=1,控制顯示與鬧鈴模塊顯示設置的鬧鈴時間。注意,當鬧鈴鍵clock=1時,計時正常運行,不論IS_SET如何設置,秒、分、時的輸出信令均為80。

2.2 計時校時模塊設計

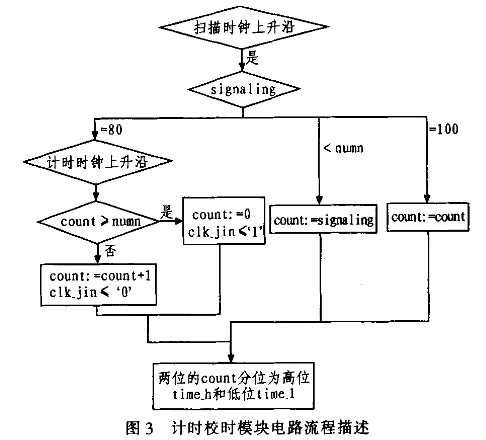

該模塊用于時、分、秒的計時校時,根據狀態選擇模塊傳輸過來的信令signaling分別進行計時和校時。時、分、秒計時校時模塊是一樣的,只是分秒的進位為60,而小時的進位為24。

我們在實體聲明中的使用generic變量定義一個numn,該值設置進制為60或24,通過修改numn值就完成分、秒計時模塊到小時計時模塊的轉換。模塊的輸入為掃描時鐘、計時時鐘和信令signaling,輸出為輸出時間高位TI me_h和輸出時間低位time_l,以及進位clk_jin。

計時校時模塊的電路描述如圖3所示,具體說明如下:每當掃描時鐘上升沿時,啟動進程,并根據信令signaling執行不同操作.

1)當signaling

2)當signaling=80時,模塊正常計時,通過判斷計時時鐘信號是否為上升沿進行計數自加操作,秒計時校時模塊的計時時鐘為1Hz的方波信號,分和小時計時校時模塊的計時時鐘為前一個模塊進位過來的clk_jin信號;

3)當signaling=100時,為暫停狀態,此時其他計時校時模塊正在校時,本模塊計時暫停。為了便于顯示,本模塊將時間count分位為時間高位time_h和時間低位time_l,并輸出到顯示與鬧鈴模塊。

2.3 顯示、鬧鈴模塊設計

本模塊是數字鐘系統中的輸出模塊,用于輸出LED數字顯示和鬧鈴,其輸入為掃描時鐘,從計時校時模塊輸出的秒低位、秒高位、分低位、分高位、時低位、時高位信號和狀態選擇模塊輸出的鬧鈴顯示Nao_En鬧鈴時間Nan_In。

如果Nao_En=0則正常顯示時間,當Nao_En=1時,在LED數碼管上顯示鬧鐘時間。當當前時間與保存的鬧鈴時間Nan_In相同時,蜂鳴器鳴響1 min。這里我們使用了八個共陰極的七段數碼管顯示時間,當選位信號sel=“01111111”時,第一個數碼管顯示數字,其他七位不顯示。

我們通過動態掃描,輪流顯示秒低位sec_ge、秒高位sec_shi、分低位min_ge、分高位min_shi、時低位hour_ge、時高位hour_shi共6路信號,當掃描時鐘sanc_clk頻率高于28 Hz時,由于人眼的視覺殘留效果,使得這6路信號看上去是同時顯示在6個七段數碼管上。顯示、鬧鈴模塊電路描述如圖4所示。

總結

在QuartusⅡ軟件開發平臺上,采用“自頂向下設計,自底向上實現”的方法完成了數字鐘的設計與實現。

其基本過程如下:

1) 完成數字鐘的總體設計;

2) 完成各個底層模塊的設計和波形仿真:底層模塊采用VHDL語言編寫,在編譯和仿真成功后,對其進行封裝;

3) 完成數字鐘的頂層電路設計:根據數字鐘的系統框圖(圖1)在QuartusⅡ中采用電路原理圖方式,調用封裝好的底層模塊,完成頂層電路圖的設計;

4) 對頂層電路進行編譯和仿真,結果表明仿真波形符合設計要求;

5)進行引腳分配,再編譯后,將下載文件下載到FPGA開發板中進行驗證和調試。測試結果表明數碼管能正確的顯示計時時間,能通過按鍵調整時間,能實現整點報時,完全符合設計要求。

-

FPGA設計

+關注

關注

9文章

428瀏覽量

27172 -

數字電路

+關注

關注

193文章

1637瀏覽量

81638

原文標題:如何做FPGA數字鐘方案?從封裝、原理圖到調試,教你一套全流程設計方法!

文章出處:【微信號:elecfans,微信公眾號:電子發燒友網】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

基于FPGA顯示數字鐘

數字鐘的設計任務及功能要求

多功能數字鐘的設計與實現

數字鐘設計方案

基于FPGA和Quartus II的多功能數字鐘設計與實現

基于fpga的數字鐘設計的兩款方案(含程序)

基于Quartus II平臺的多功能數字鐘的設計

fpga數字鐘介紹_fpga數字鐘設計

FPGA數字鐘方案設計

FPGA數字鐘方案設計

評論