大量的新節(jié)點、半節(jié)點,以及在兩者之間的每一個數(shù)字的產(chǎn)生正在芯片制造商之造成混淆。雖然大多數(shù)人認(rèn)為有選擇是好事,但大家并不清楚哪個或哪些選擇是上策。

問題在于哪個IP可用于這些節(jié)點;該IP在功率、性能、面積和對各種噪聲類型的敏感度方面與其他節(jié)點的差異如何;面對不同的節(jié)點和nodelet,不同版本的IP對應(yīng)那些不同制造工藝進(jìn)行測試。因為大多數(shù)新的不全節(jié)的節(jié)點定義尚未明確。因此,對于哪種類型的晶體管會被使用,哪種會影響柵極泄漏和動態(tài)功率密度,以及這將如何影響相鄰的IP和其他組件需要多少額外的掩模圖案等等問題,現(xiàn)在下結(jié)論還為時過早。

ClioSoft公司的營銷副總裁Ranjit Adhikary表示:“現(xiàn)在,不同廠商之間的節(jié)點數(shù)字和名字不盡相同,每一種的PPA(性能、功耗、面積)表現(xiàn)怎么樣?因為PPA是決定你設(shè)計產(chǎn)品使用哪種IP的最基礎(chǔ)因素。但是,因為選擇太多,現(xiàn)在你需要查看哪些代工廠提供它,它支持哪個節(jié)點。對于每個IP,可能會有不同的內(nèi)存或緩存,并且因代工廠、類別和工藝節(jié)點而異。”

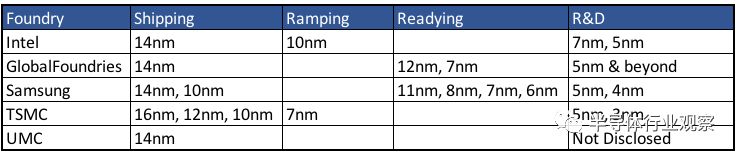

代工廠的計劃和它們?nèi)缃竦奈恢谩?(來源:Analysts, Foundry Reports/Semiconductor Engineering)

但是,所有主要的工藝節(jié)點都有多種類型,多個部分節(jié)點從22nm到3nm不等。這引發(fā)了關(guān)于哪些IP可用的問題,它是否已針對每個節(jié)點進(jìn)行了充分的特性描述和測試,以及是否會支持適用于不同的終端市場所需要的時間。這對移動器件而言并不是問題,在過去的幾十年中,移動器件以相對較短的產(chǎn)品周期占據(jù)了芯片市場的主導(dǎo)地位,但對于工業(yè)和汽車應(yīng)用而言則完全是另外一回事,此處的器件需要數(shù)十年的支持。

Synopsys公司DesignWare Analog和MSIP解決方案集團(tuán)的高級營銷總監(jiān)Navraj Nandra表示:“我們從未見過如此的代工廠節(jié)點激增。我們有從18nm到1nm的節(jié)點名稱。但這需要管理層承諾投資一個節(jié)點。他們希望看到硬IP是否可用,為此,你需要一個可用的SoC,因為你確實希望看到在新節(jié)點中使用的IP的芯片測試報告。這同樣需要IP供應(yīng)商的投資。所以代工廠可能會從時序角度和ROI角度(如高速內(nèi)存接口或基于HBM的產(chǎn)品)中找到一些稍好的東西。 但你也可能在這里花一大筆錢,卻賺不到錢。”

這似乎是IP開發(fā)人員的一致意見。他們沒有像過去那樣支持每個節(jié)點,而是試圖評估哪些節(jié)點可能產(chǎn)生足夠的產(chǎn)量,以創(chuàng)造合理的投資回報。努力并不總是轉(zhuǎn)化為利潤,特別是在高級節(jié)點上,而錯誤的選擇可能代價高昂。

Cadence公司的產(chǎn)品營銷,DDR,HBM,F(xiàn)lash/存儲和MIPI IP部門主管 Marc Greenberg表示:“我們都知道,較新的工藝掩模圖案更多的是一種工藝能力(晶體管密度和功率/速度的折中)指南,而不是工藝的任何實際物理尺寸。迄今為止的行業(yè)標(biāo)準(zhǔn)一直是指出工藝中的關(guān)鍵差異——例如,SiON(氮氧化硅)vs high-k/metal gate,是否使用EUV——使用字母或符號后綴對工藝進(jìn)行標(biāo)記。但是這可能最終會成為新的nodelet而不是新的后綴。在28nm節(jié)點上,我們看到了28nm工藝的很多變種,它們通常互不兼容。這為IP行業(yè)帶來了許多工作,以涵蓋所有這些工藝節(jié)點的變化。我們還看到一些早期的finFET節(jié)點起飛出現(xiàn)了一些困難,這對于IP行業(yè)來說是更大的工作,而這并不一定會轉(zhuǎn)化為銷量。”

nodelet是什么?

市場營銷術(shù)語是造成nodelet困惑的主要原因。數(shù)字也模糊到?jīng)]有人確切知道數(shù)字的真正含義。例如臺積電和三星所謂的5nm實際上是英特爾、GlobalFoundries和Imec的7nm,對于10/7nm和5/3nm也是如此。最重要的是,這些節(jié)點有不同的版本,基于低功耗、基于高性能、基于成本,每一種都有其不同的特點。

Synopsys公司的Nandra表示:“一個既定節(jié)點的預(yù)想的工藝是,如果它在量產(chǎn),那么你可以優(yōu)化該節(jié)點。例如,你有28nm,你知道它很好用,而缺陷密度是一個固定的百分比。為了改善這一點,你可以稍微壓縮一下,給它一個新的名字,比如22nm。但這并不意味著它有22nm的柵極長度。你只是做了一些事情來讓它擁有更好的密度。對于IP行業(yè)而言,這不應(yīng)該是一個大的改變。但是,當(dāng)涉及到高速版本時,由于封裝的提取,仿真,電阻,電容和感應(yīng)關(guān)系,光學(xué)縮小對晶體管的影響,所有這些都會造成大量的重新工作。你需要對IP進(jìn)行完全的重新驗證。布局后寄生參數(shù)提取可能是一個相當(dāng)大的挑戰(zhàn)。或者你需要完成一個新的測試芯片,以確保你沒有遺漏任何東西。”

在finFET時代之前,代工廠將采用英特爾的節(jié)點和半節(jié)點的“Tick-Tock”策略。但是,在28nm之后,節(jié)點編號開始分裂成可能或不可能出現(xiàn)的編號片段,這在很大程度上是因為沒有足夠的IP選擇使它們可行。雖然大IP供應(yīng)商將跟進(jìn),至少目前來說,目前還不清楚行業(yè)其他廠商能否跟上。

Cadence公司的Greenberg表示:“12/11nm節(jié)點也獲得了代工廠的良好支持。我們從代工廠得到的指導(dǎo)是,它應(yīng)該是一個從16/14nm到12/11nm的‘簡單’IP端口。然而,在某些情況下,我們已經(jīng)采取了生產(chǎn)和描述這些節(jié)點的新IP測試芯片的步驟。一些代工廠正在支持10nm半節(jié)點和它的8nm nodelet,我們正在支持選擇的IP。在7nm處,我們有一個強大的節(jié)點,Cadence廣泛支持最新的先進(jìn)技術(shù)IP。現(xiàn)在還無法確定是否會有一個廣泛支持的6nm節(jié)點,或者行業(yè)是否會跳躍到5nm。”

Nandra指出,這一工作可能比IP開發(fā)者預(yù)期的更昂貴。“如果可以的話,客戶會要求基于芯片的特性報告。如果有強大的模擬/混合信號部分,客戶會更加保守。他們希望看到更多的芯片。”

越來越多細(xì)節(jié)中的魔鬼

對于28nm及以下的節(jié)點,節(jié)點的微縮似乎沒有盡頭。目前的估計是在1.2到1.3nm之間,盡管確切的數(shù)字可能會根據(jù)環(huán)繞閘極FET vs finFET的類型而變化,例如,引入光刻選項,如定向自組裝和high-NA EUV來擴展器件微縮比例,以及在計量、蝕刻和沉積方面的進(jìn)步。

Fraunhofer公司工程自適應(yīng)系統(tǒng)部門設(shè)計方法負(fù)責(zé)人Roland Jancke表示:“7nm技術(shù)正在開發(fā)中,5nm和4nm已經(jīng)公布。為了提高這種技術(shù)的性能,集成器件是極度優(yōu)化的。因此,在技術(shù)節(jié)點中出現(xiàn)了大量的獨立器件類型,例如I/O器件、核心器件、上拉和下拉器件、以及器件的幾個閾值電壓版本。這種趨勢極大地增加了技術(shù)特性、資格和模型開發(fā)的工作量,這需要在每次工藝變更后重復(fù)進(jìn)行。”

此外,這些器件對諸如溫度和噪音等物理因素越來越敏感。閾值電壓在不同溫度下響應(yīng)不同,并且靈敏度隨著每個節(jié)點縮小而增加。其結(jié)果是需要比過去更詳細(xì)的描述。

Rambus公司的首席科學(xué)家Craig Hampel表示:“我們在高Vt段上做了調(diào)整,起初沒能解決這個問題。所以,現(xiàn)在如果我們有高Vt,我們會提高特性描述的級別。在過去的幾年里,隨著節(jié)點遷移到16nm,我們的特性描述幾乎增加了四倍。”

在此之后,每個新節(jié)點的問題也會越來越嚴(yán)重。但是,增加的特性描述不再只是較低節(jié)點的問題。舊節(jié)點工藝也有許多變體,而且還有更多涉及安全性和可靠性的使用案例,即使在較舊節(jié)點上也需要更多特性描述。

Fraunhofer公司的Jancke表示:“對于低至110nm以內(nèi)的混合信號技術(shù)節(jié)點,在給定節(jié)點中存在著巨大的多樣性。對于超低功耗、高功率、高電壓、RF和光學(xué)應(yīng)用、MEMS器件等等,通常有單獨的技術(shù)版本。另一方面,設(shè)計師傾向于將SoC的幾個部分集成到一個硅片裸片中,這導(dǎo)致了功率集成電路的BCD工藝等組合技術(shù)的興趣和發(fā)展。”

這也使得評估哪個IP最有效變得更困難,因為一個IP需要與其他IP協(xié)同工作。 所有這些都會影響上市時間,整體成本以及功率/性能。甚至更糟糕的是,如果可用選項較少,則可能會限制器件的功能。

ClioSoft公司的Adhikary表示:“有很多問題需要用IP來解答。如果你想要更高的性能,從9nm節(jié)點獲取IP并將其移動到5nm,那么這樣做你能獲得多少面積?為一個新節(jié)點開發(fā)IP可能需要三到四個月的時間。不過,你真的能在面積和性能上獲得好處嗎?如果你每年都要做多次流片,你使用的是什么版本的IP?如果其他人使用該IP,他們是否使用相同的PDK庫?如果你正在將IP與其他IP集成,你確實需要確保你擁有相同版本的PDK。我們現(xiàn)在更關(guān)注PDK的版本和什么版本的庫正在使用。你需要了解的細(xì)節(jié)越來越多。”

從IP開發(fā)人員的角度來看,這也是有問題的。Synopsys公司的Nandra表示:“這種工作的差異顯然會出現(xiàn)在更新的技術(shù)版本上。開發(fā)7nm或10nm IP比14nm或28nm需要更長的時間,而且這項工作通常是原來工作量的兩到四倍。”

結(jié)論

所有這一切都因新節(jié)點、nodelet和節(jié)點命名約定而變得更加復(fù)雜。代工廠已經(jīng)加大了提供更多數(shù)據(jù)的力度,而且IP供應(yīng)商的特性描述要比過去更多,因為每個新節(jié)點和nodelet的容限變得更加緊密。

Greenberg表示:“每個人都從28nm時代開始學(xué)習(xí),雖然在節(jié)點的生命周期中總會有工藝方面的進(jìn)步,但代工廠已經(jīng)更好地為IP提供商提供了早期的指導(dǎo),并指導(dǎo)了基本過程及其變體之間的差異。在某些情況下,這允許我們針對來自同一IP開發(fā)的節(jié)點及其nodelet或多個后綴工藝的混合信號IP進(jìn)行開發(fā)。當(dāng)代工廠能夠提前將這些計劃傳達(dá)給我們時,它有助于我們提供更廣泛的IP,并最終有助于降低成本。”

但至少在可預(yù)見的將來,管理節(jié)點名稱、數(shù)字和IP版本將變得更加困難。有太多的選擇和潛在的交互作用,還有太多的定義不清或尚未定義的變動部分。

-

芯片

+關(guān)注

關(guān)注

459文章

52199瀏覽量

436371 -

工藝

+關(guān)注

關(guān)注

4文章

672瀏覽量

29260 -

高功率

+關(guān)注

關(guān)注

1文章

199瀏覽量

18625

發(fā)布評論請先 登錄

TSV以及博世工藝介紹

關(guān)于工藝節(jié)點的分析和介紹以及發(fā)展

關(guān)于工藝節(jié)點的分析和介紹以及發(fā)展

評論